Примечание

Для установки плат не требуется кабель Ethernet или карта SD.

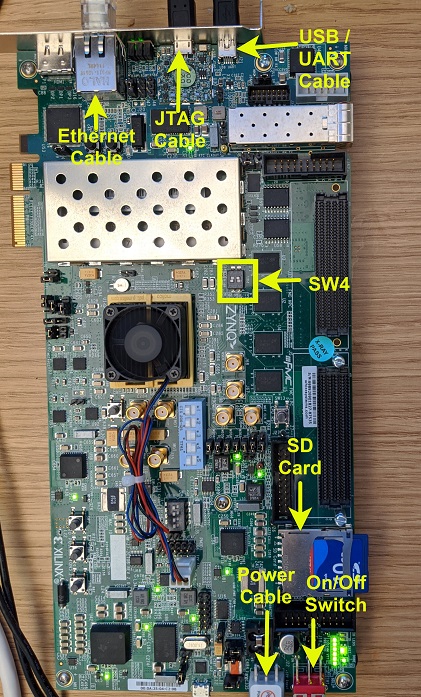

На этом рисунке показана настройка платы для оценки Xilinx ® Zynq ® -7000 ZC706. Для установки платы:

Настроить SW4 и использовать интерфейс Digilent USB-TO-JTAG с использованием следующей таблицы конфигурации:

| Источник конфигурации | SW4 переключатель 1 | SW4 переключатель 2 |

| Ничего | 0 | 0 |

| Кабельный разъем J3 | 1 | 0 |

| Интерфейс Digilent USB-TO-JTAG | 0 | 1 |

| JTAG (летающий свинец) J62 заголовка | 1 | 1 |

Подключите кабель питания, а затем подключите хост-компьютер к плате FPGA с помощью кабеля JTAG, как показано на рисунке ниже:

Сведения об использовании Ethernet см. в разделе Создание целевого объекта с интерфейсом Ethernet и установка IP-адреса.

Для получения дополнительной информации о конфигурации платы см. Руководство пользователя платы Xilinx ZC706 Evaluation Board.

После настройки соединения с платой выполните следующие действия:

Создайте объект рабочего процесса, используя имя битового потока, предоставленное для платы, как указано в разделе Использование битовых потоков глубокого обучения (пакет поддержки панели инструментов HDL для глубокого обучения для устройств Xilinx FPGA и SoC).

Дополнительные сведения о рабочем процессе см. в разделе Прототипы сетей глубокого обучения для рабочих процессов FPGA и SoC.

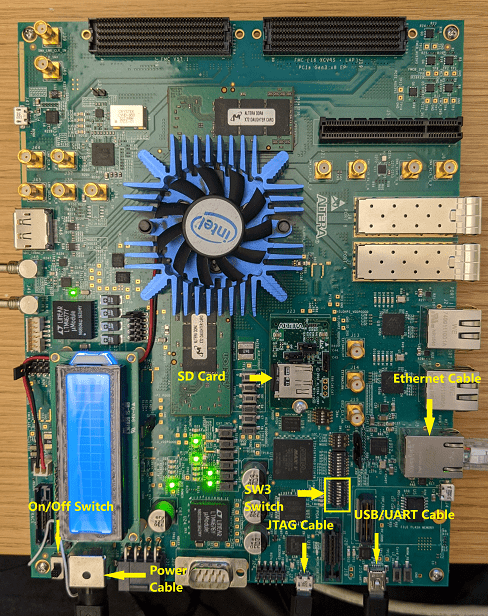

На этом рисунке показано, как настроить комплект для разработки Intel ® Arria ® 10 SoC. Для установки платы:

Подключите кабель питания, а затем подключите хост-компьютер к плате FPGA с помощью кабеля JTAG.

Укажите параметры переключения SW3:

| Бит 1 | Бит 2 | Бит 3 | Бит 4 | Бит 5 | Бит 6 | Бит 7 | Бит 8 |

| Прочь | На | На | На | На | Прочь | Прочь | Прочь |

Подключите две DDR4 платы подключаемых модулей к слоту подключаемых модулей памяти.

Сведения об использовании Ethernet см. в разделе Создание целевого объекта с интерфейсом Ethernet и установка IP-адреса.

На этом рисунке показаны настройки конфигурации комплекта для разработки Intel Arria 10 SoC.

Дополнительные сведения о конфигурации платы см. в Руководстве пользователя пакета разработки Arria 10 SoC.

После настройки соединения с платой выполните следующие действия:

Создайте объект workflow-процесса, используя имя битового потока, предоставленное для платы, как указано в разделе Использование битпотоков Deep Learning (пакет поддержки панели инструментов Deep Learning HDL Toolbox для устройств Intel FPGA и SoC).

Дополнительные сведения о рабочем процессе см. в разделе Прототипы сетей глубокого обучения для рабочих процессов FPGA и SoC.

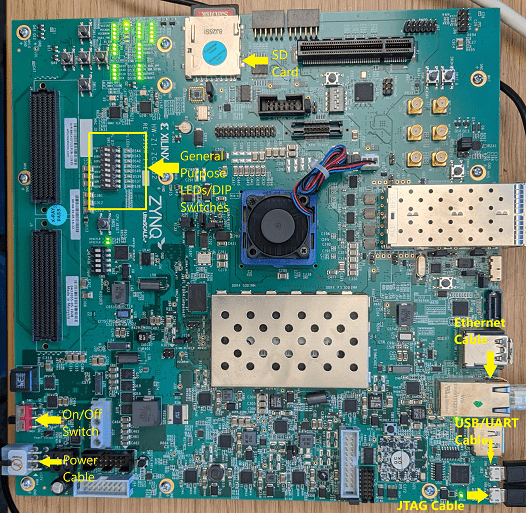

1. Настройте комплект для оценки ZCU102 Xilinx Zynq UltraScale + MPSoC, как показано на рисунке ниже :

Для установки платы:

Подключите шнур питания. При использовании JTAG подключите плату FPGA к хост-компьютеру с помощью кабеля JTAG. При использовании Ethernet подключите плату FPGA к хост-компьютеру с помощью кабеля Ethernet.

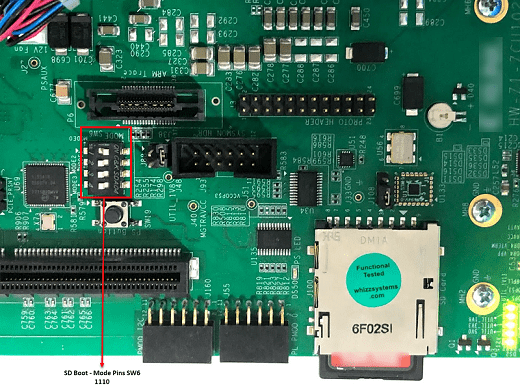

Настроить SW6 переключатель, который показан на рисунке ниже:

Используйте приведенную ниже таблицу конфигурации для конфигурирования параметров коммутатора:

| Режим загрузки | Контакты режима [3:0] | SW6 Положение переключателя [3:0] |

JTAG | 0, 0, 0, 0 | вкл., вкл., вкл., вкл. |

QSPI32 | 0, 0, 1, 0 | вкл., вкл., выкл., вкл. |

SD | 1, 1, 1, 0 | выкл., выкл., выкл., вкл. |

SW6 позиция по умолчанию - QSPI32. Для SW6 DIP-переключатель перемещает переключатель в направлении ON метка имеет значение 0.

Сведения об использовании Ethernet см. в разделе Создание целевого объекта с интерфейсом Ethernet и установка IP-адреса.

Дополнительные сведения о настройке ZCU102 оборудования см. в документации Xilinx.

После настройки соединения с платой выполните следующие действия:

Создайте объект рабочего процесса, используя имя битового потока, предоставленное для платы, как указано в разделе Использование битовых потоков глубокого обучения (пакет поддержки панели инструментов HDL для глубокого обучения для устройств Xilinx FPGA и SoC).

Дополнительные сведения о рабочем процессе см. в разделе Прототипы сетей глубокого обучения для рабочих процессов FPGA и SoC.