При определении собственной пользовательской ссылочной конструкции можно динамически настраивать ссылочную конструкцию с помощью CustomizeReferenceDesignFcn способ hdlcoder.ReferenceDesign класс.

Путем настройки параметров ссылочной конструкции вместо ведения отдельных ссылочных конструкций, имеющих различные варианты интерфейса, ширину данных или подключаемые модули ввода-вывода, создайте одну ссылочную конструкцию, которая имеет различные варианты интерфейса или ширину данных в качестве параметров. Затем можно использовать CustomizeReferenceDesignFcn метод для ссылки на функцию обратного вызова, которая имеет различные варианты для интерфейсов или ширины данных.

Например, вместо создания отдельных ссылочных проектов, имеющих различную ширину данных для интерфейсов, можно параметризовать ширину данных, а затем создать ссылочный параметр конструкции. При запуске IP Core Generation workflow-процесс, можно использовать параметр для выбора ширины данных, которую требуется использовать. Точно так же вместо того, чтобы использовать несколько справочных проектов, Вы можете создать один справочный дизайн, у которого есть только Основной AXI4-поток или только Раб AXI4-потока или и Рабские интерфейсы Владельца и AXI4-потока AXI4-потока.

Для определения функции обратного вызова:

В plugin_rd определите ссылочные параметры конструкции, которые требуется настроить, с помощью addParameter способ.

Создайте файл MATLAB ®, определяющий функцию обратного вызова. Для функции обратного вызова можно использовать любое произвольное имя.

Сохраните функцию обратного вызова в той же папке, что и plugin_rd.m файл.

Зарегистрировать дескриптор функции обратного вызова в определении ссылочного проекта plugin_rd с помощью CustomizeReferenceDesignFcn способ.

Для использования различных настроек ссылочной конструкции:

Откройте помощник по рабочим процессам HDL. В задании Set Target Device and Synthesis Tool выберите IP Core Generation в качестве целевого рабочего процесса, а затем выберите целевую плату, для которой был создан собственный пользовательский эталонный проект в качестве целевой платформы.

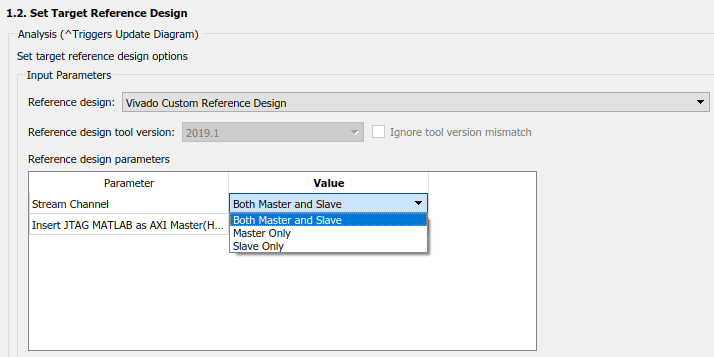

При выборе пользовательской ссылочной конструкции, которую требуется настроить для целевой платы, в задании Задать целевую ссылочную конструкцию (Set Target Reference Design) HDL Coder™ заполняет ссылочные параметры конструкции. В зависимости от выбора параметров, например, указанных типов интерфейса, вычисляется функция обратного вызова. Запустите эту задачу.

Выберите задачу Задать целевой интерфейс. В зависимости от параметра, выбранного на предыдущем шаге, выбор целевого интерфейса заполняется в таблице интерфейса целевой платформы.

В функции обратного вызова можно настроить эти ссылочные параметры конструкции. Не указывайте эти параметры в plugin_rd файл.

Файл Tcl проекта блока

% ... % if ~isempty(ParamValue) hRD.addCustomVivadoDesign( ... 'CustomBlockDesignTcl', 'system_top.tcl', ... 'VivadoBoardPart', 'xilinx.com:zc706:part0:1.0'}; % ...

Ссылочные интерфейсы проектирования и свойства ссылочного интерфейса проектирования

Например, можно параметризовать ширину данных главного канала AXI4-Stream. В этом случае используйте addAXI4StreamInterface метод в функции обратного вызова вместо plugin_rd файл.

% ... % Add AXI4-Stream interface by parameterizing data width DataWidth = hRD.getParamValue(paramValue) if ~isempty(DataWidth) hRD.addAXI4StreamInterface( 'MasterChannelEnable', 'true', ... 'SlaveChannelEnable', 'true', ... 'MasterChannelConnection', 'ByPass_0.AXI4_Stream_Slave', ... 'SlaveChannelConnection', 'ByPass_0.AXI4_Stream_Master', ... 'MasterChannelDataWidth', DataWidth, ... 'SlaveChannelDataWidth', DataWidth); end % ...

Репозитории IP

При добавлении репозиториев IP в функции обратного вызова необходимо указать Tcl-файл конструкции блока.

% ... %% Add IP Repository hRD.addIPRepository(... 'IPListFunction', 'mathworks.hdlcoder.vivado.hdlcoder_video_iplist', 'NotExistMessage', 'IP repository not found'); %% Add custom design files hRD.addCustomVivadoDesign( ... 'CustomBlockDesignTcl', 'system_top.tcl', ... 'VivadoBoardPart', 'em.avnet.com:zed:part0:1.0'); % ...

Примечание

В функции обратного вызова нельзя изменить ссылочное имя конструкции, имя платы и поддерживаемые версии инструментов. Эти параметры используются в задаче Set Target Device and Synthesis Tool перед оценкой функции обратного вызова при выборе целевой эталонной конструкции в задаче Set Target Reference Design.

Вместо использования нескольких ссылочных конструкций можно создать одну ссылочную конструкцию, имеющую только интерфейс AXI4-Stream Master или только AXI4-Stream Slave или оба интерфейса AXI4-Stream Master и AXI4-Stream Slave. В этом примере показано, как можно настроить каналы интерфейса AXI4-Stream, которые необходимо использовать при выборе собственного ссылочного проекта для Xilinx Zynq ZC706 evaluation kit.

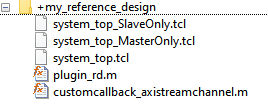

Этот код показывает ссылочный параметр конструкции и варианты интерфейса для ссылочной конструкции my_reference_design задается с помощью addParameter метод в plugin_rd файл. CustomizeReferenceDesignFcn метод ссылается на функцию обратного вызова, имеющую имя customcallback_axistreamchannel.

function hRD = plugin_rd() % Reference design definition % Copyright 2017-2019 The MathWorks, Inc. % Construct reference design object hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Xilinx Vivado'); hRD.ReferenceDesignName = 'Vivado Custom Reference Design'; hRD.BoardName = 'Xilinx Zynq ZC706 evaluation kit'; % Tool information hRD.SupportedToolVersion = {'2019.1'}; % ... % ... % Parameter For calling AXI4 Master interface from Callback function hRD.addParameter ... ('ParameterID' , 'stream_channel', ... 'DisplayName' , 'Stream Channel', ... 'DefaultValue' , 'Both Master and Slave',... 'ParameterType' , hdlcoder.ParameterType.Dropdown, ... 'Choice' , {'Both Master and Slave','Master Only','Slave Only'}); % Reference the callback function. hRD.CustomizeReferenceDesignFcn = @my_reference_design.customcallback_axistreamchannel; % ...

При создании функции обратного вызова передайте infoStruct аргумент функции. Аргумент содержит ссылочную конструкцию и информацию о плате в structure формат. Этот код показывает функцию обратного вызова customcallback_axistreamchannel , который имеет ведущие или подчиненные каналы AXI4-Stream или оба канала, указанные с помощью addAXI4StreamInterface способ.

% Control AXI Master or Slave channel selection by using callback function function customcallback_axistreamchannel(infoStruct) %% Reference design callback run at the end of the task Set Target Reference Design % % infoStruct: information in structure format % infoStruct.ReferenceDesignObject: current reference design registration object % infoStruct.BoardObject: current board registration object % infoStruct.ParameterStruct: custom parameters of the current reference design, in struct format % infoStruct.HDLModelDutPath: the block path to the HDL DUT subsystem % infoStruct.ReferenceDesignToolVersion: Reference design Tool Version set in 1.2 Task paramStruct = infoStruct.ParameterStruct; if ~isempty(paramStruct) paramIDCell = fieldnames(paramStruct); paramValue = ''; for ii = 1:length(paramIDCell) paramID = paramIDCell(ii); if strcmp(paramID,'Both Master and Slave') paramValue = paramStruct.paramID; break; elseif strcmp(paramID,'Master Only') paramValue = paramStruct.paramID; break; elseif strcmp(paramID,'Slave Only') paramValue = paramStruct.paramID; break; end end end interface_type = str2double(paramValue); if ~isempty(interface_type) if strcmp(interface_type, 'Both Master and Slave') % add custom vivado design hRD.addCustomVivadoDesign( ... 'CustomBlockDesignTcl', 'system_top.tcl', ... 'VivadoBoardPart', 'xilinx.com:zc706:part0:1.0'); hRD.addAXI4StreamInterface( ... 'MasterChannelEnable', 'true', ... 'SlaveChannelEnable', 'true', ... 'MasterChannelConnection', 'axi_dma_s2mm/S_AXIS_S2MM', ... 'SlaveChannelConnection', 'axi_dma_mm2s/M_AXIS_MM2S', ... 'MasterChannelDataWidth', 32, ... 'SlaveChannelDataWidth', 32); elseif strcmp(interface_type, 'Master Only') % add custom vivado design hRD.addCustomVivadoDesign( ... 'CustomBlockDesignTcl', 'system_top.tcl', ... 'VivadoBoardPart', 'xilinx.com:zc706:part0:1.0'); hRD.addAXI4StreamInterface( ... 'MasterChannelEnable', true, ... 'MasterChannelConnection', 'axi_dma_s2mm/S_AXIS_S2MM', ... 'MasterChannelDataWidth', 32); % ...

Сохраните функцию обратного вызова в той же папке, что и plugin_rd файл.

При запуске IP Core Generation рабочий процесс с Xilinx Zynq ZC706 evaluation kit в качестве целевой платформы отображается параметр Stream Channel в задаче Set Target Reference Design.

Можно указать тип эталонного проекта, который требуется использовать, а затем запустить рабочий процесс для определения интерфейсов целевой платформы, а затем создать ядро IP HDL и затем интегрировать ядро IP в эталонный проект.

hdlcoder.Board | hdlcoder.ReferenceDesign