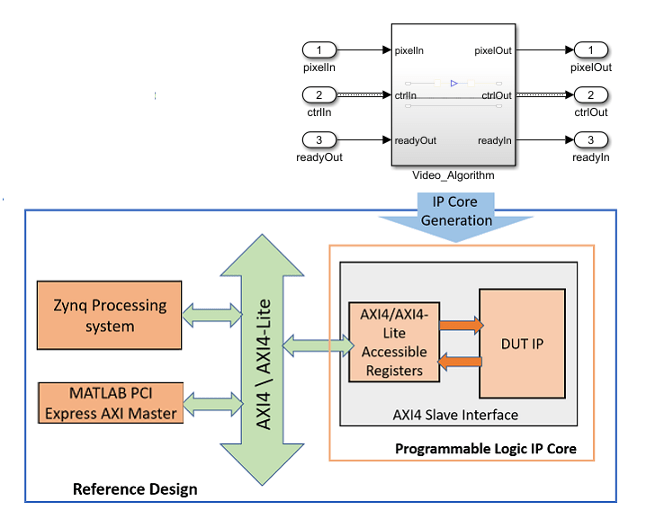

Можно определить несколько главных интерфейсов AXI в пользовательском эталонном проекте и получить доступ к AXI4 подчиненным интерфейсам в сгенерированном IP-ядре HDL DUT для DUT. Эта функция позволяет одновременно подключить IP-ядро HDL DUT к двум или более IP-адресам AXI Master в эталонной конструкции, таким как HDL Verifier™ JTAG AXI Master IP и процессор ARM ® в процессорной системе Zynq ®.

Для определения нескольких главных интерфейсов AXI необходимо указать BaseAddressSpace и MasterAddressSpace для каждого экземпляра AXI Master, а также IDWidth собственность.

IDWidth - ширина всех ID-сигналов, например, AWID, WID, ARID, и RID, указано как положительное целое число. По умолчанию IDWidth является 12, которая позволяет указать одно соединение главного интерфейса AXI с ядром IP DUT. Для подключения ядра DUT IP к нескольким главным интерфейсам AXI, возможно, потребуется увеличить IDWidth. IDWidth значение зависит от инструмента. Чтобы увидеть значение, которое необходимо использовать при указании нескольких главных интерфейсов AXI, см. документацию по этому инструменту. Если используется неправильная ширина идентификатора, инструмент синтеза генерирует ошибку и сообщает о правильном IDWidth которые вы должны использовать.

Этот код является синтаксисом для MasterAddressSpace при указании нескольких интерфейсов AXI Master в эталонных конструкциях на базе Vivado ®:

'MasterAddressSpace', ...

{'AXI Master Instance Name1/Address Space of Instance Name1', ...

'AXI Master Instance Name2/Address_Space of Instance Name2',...};Например, этот код иллюстрирует, как можно изменить plugin_rd для определения двух главных интерфейсов AXI.

% ... %% Add custom design files % add custom Vivado design hRD.addCustomVivadoDesign( ... 'CustomBlockDesignTcl', 'system_top.tcl', ... 'VivadoBoardPart', 'xilinx.com:zc706:part0:1.0'); % ... % ... % The DUT IP core in this reference design is connected % to both Zynq Processing System and the MATLAB as AXI % Master IP. Because of 2 AXI Master, ID width % has to be increased from 12 to 13. hRD.addAXI4SlaveInterface( ... 'InterfaceConnection', 'axi_interconnect_0/M00_AXI', ... 'BaseAddress', {'0x40010000', '0x40010000'}, ... 'MasterAddressSpace', {'processing_system7_0/Data', 'hdlverifier_axi_master_0/axi4m'}, ... 'IDWidth', 13); % ...

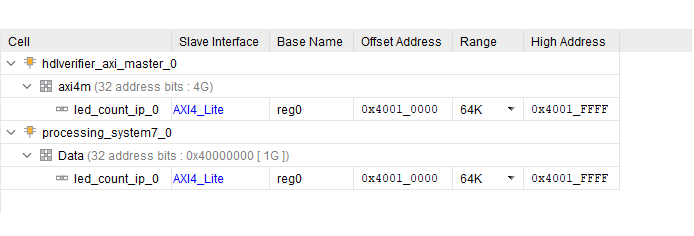

В этом примере двумя главными IP-адресами AXI являются верификатор HDL MATLAB в качестве главного IP-адреса AXI и процессор ARM. На основе синтаксиса MasterAddressSpace, для верификатора HDL MATLAB в качестве AXI Master IP, AXI Master Instance Name является hdlverifier_axi_master_0 и Address_Space of Instance Name является axi4m.

Подчиненные интерфейсы AXI4 в IP-ядре HDL DUT подключаются к IP-соединению Xilinx ® AXI, которое определяется InterfaceConnection имущества addAXI4SlaveInterface способ. Ведомые интерфейсы AXI4 имеют BaseAddress. Это BaseAddress должен сопоставляться с MasterAddressSpace для двух главных IP-адресов AXI, которые задаются как массив ячеек символьных векторов.

Вы должны убедиться, что AXI Master IP уже включены в проект эталонного дизайна Vivado. system_top.tcl - файл TCL, определенный CustomBlockDesignTcl имущества addCustomVivadoDesign способ. В этом файле TCL необходимо убедиться, что два основных IP-адреса AXI подключены к одному IP-адресу Xilinx AXI Interconnect. Затем межсоединения соединяют ведущие IP-адреса AXI с AXI4 подчиненными интерфейсами в ядре IP HDL.

После запуска IP Core Generation и создайте проект Vivado, откройте проект. В проекте Vivado, если открыть дизайн блока, вы увидите два основных IP-адреса AXI, подключенных к IP-ядру HDL DUT. При выборе вкладки Редактор адресов (Address Editor) отображаются имена экземпляров AXI Master и соответствующие адресные пространства.

Для определения нескольких главных интерфейсов AXI необходимо указать InterfaceConnection и BaseAddressSpace для каждого экземпляра AXI Master, а также IDWidth собственность. Этот код является синтаксисом для InterfaceConnection при указании нескольких главных интерфейсов AXI во Qsys™-based ссылочных конструкциях:

'InterfaceConnection', ...

{'AXI Master Instance Name1/Port name of Instance Name1', ...

'AXI Master Instance Name2/Port name of Instance Name1', ...};Например, этот код иллюстрирует, как можно изменить plugin_rd для определения трех главных интерфейсов AXI.

% ... %% Add custom design files % add custom Qsys design hRD.addCustomQsysDesign('CustomQsysPrjFile', 'system_soc.qsys'); hRD.CustomConstraints = {'system_soc.sdc','system_setup.tcl'}; % ... % add AXI4 slave interfaces hRD.addAXI4SlaveInterface( ... 'InterfaceConnection', {'hps_0.h2f_axi_master','master_0.master','MATLAB_as_AXI_Master_0.axm_m0'}, ... 'BaseAddress', {'0x0000_0000','0x0000_0000','0x0000_0000'},... 'InterfaceType', 'AXI4'... 'IDWidth', 14); % ...

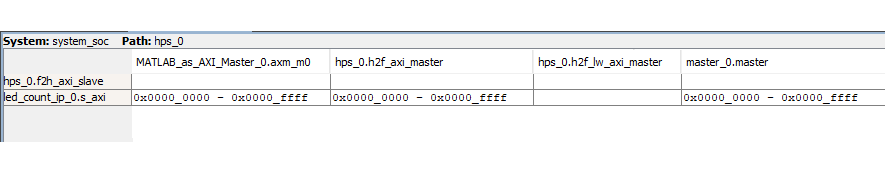

На основе синтаксиса InterfaceConnection для верификатора HDL MATLAB в качестве AXI Master IP, AXI Master Instance Name является MATLAB_as_AXI_Master_0 и Port name является axm_m0. Для каждого главного IP-адреса AXI BaseAddress IP-ядра ЛПВП и InterfaceConnection должен быть указан как массив ячеек символьных векторов.

Необходимо убедиться, что основные IP-адреса AXI уже включены в справочный дизайн Qsys. system_soc.qsys является файлом, который определен CustomQsysPrjFile имущества addCustomQsysDesign способ. В этом файле необходимо убедиться, что два основных IP-адреса AXI подключены к одному IP-адресу Qsys AXI Interconnect.

Затем межсоединения соединяют ведущие IP-адреса AXI с AXI4 подчиненными интерфейсами в ядре IP HDL.

После запуска IP Core Generation и создайте проект Quartus ®, откройте проект. В проекте Quartus отображаются три интерфейса AXI Master IP и AXI Master, подключенные к ядру HDL IP для DUT. При выборе вкладки «Карта адресов» отображаются имена экземпляров AXI Master, имена портов и соответствующие адресные пространства.

hdlcoder.Board | hdlcoder.ReferenceDesign