HDL Coder™ поддерживает несколько оптимизаций, реализаций блоков и опций, которые вводят дискретные задержки в модель, с целью более эффективного использования аппаратного обеспечения или достижения более высокой тактовой частоты. Примеры:

Оптимизация: Оптимизация, такая как конвейерная передача, потоковая передача или совместное использование ресурсов, может привести к задержкам.

Каскадирование: Некоторые блоки поддерживают каскадные реализации, которые вводят цикл задержки в генерируемый код.

Блочные реализации: некоторые блочные реализации, такие как архитектура Ньютона-Рафсона, врождают задержки в генерируемом коде.

Когда оптимизации или варианты реализации блоков вводят задержки вдоль критического пути в модели, цифры исходной модели и сгенерированной модели или кода HDL могут отличаться, поскольку эквивалентные задержки не вводятся на других параллельных каналах сигнала. Ручная вставка компенсирующих задержек вдоль других путей возможна, но подвержена ошибкам и плохо масштабируется для больших моделей с множеством путей сигнала или множественными скоростями дискретизации.

Для решения этой проблемы кодер HDL поддерживает балансировку задержки. По умолчанию в модели включена балансировка задержки. Генератор кода обнаруживает введение новых задержек по одному пути, а затем вставляет совпадающие задержки по другим путям. Когда балансировка задержки включена, создаваемая модель функционально эквивалентна исходной модели. Не рекомендуется отключать балансировку задержки в модели. Если этот параметр отключен, кодер HDL генерирует предупреждение о том, что в модели проверки могут возникать числовые различия. Чтобы исправить это предупреждение, включите параметр Задержки баланса в модели или запустите параметр Балансировка задержки проверки модели.

Можно задать балансировку задержки для всей модели. Для более точного управления можно также установить балансировку задержки для подсистем в подсистеме DUT верхнего уровня.

Используйте следующее makehdl свойства для задания балансировки задержки для модели:

BalanceDelaysПо умолчанию балансировка задержки на уровне модели включена, и подсистемы внутри модели наследуют настройку на уровне модели. Сведения о настройке балансировки задержки для модели см. в разделе Задержки балансировки.

GenerateValidationModelПо умолчанию создание модели проверки отключено. При включении балансировки задержки создайте модель проверки для просмотра задержек и других различий между исходной моделью и созданной моделью. Сведения о включении генерации модели проверки см. в разделе Создание модели проверки в разделе Параметры генерации модели для кода HDL.

Например, следующие команды генерируют код HDL с балансировкой задержки и формируют модель проверки.

dut = 'ex_rsqrt_delaybalancing/Subsystem'; makehdl(dut,'BalanceDelays','on','GenerateValidationModel','on');

Можно отключить балансировку задержки для всей модели или отключить подсистему в подсистеме DUT верхнего уровня. Например, если не требуется сбалансировать задержки для управляющего тракта, можно поместить управляющий тракт в подсистему и отключить балансировку задержки для этой подсистемы.

Чтобы отключить балансировку задержки для подсистемы в подсистеме DUT верхнего уровня, отключите балансировку задержки на уровне модели. При отключении балансировки задержки для модели модель проверки не компенсирует задержки, вставленные в создаваемую модель из-за оптимизации или реализации блоков. Поэтому в модели проверки могут быть обнаружены несоответствия между исходной моделью и созданной моделью.

Чтобы отключить балансировку задержки для подсистемы в подсистеме DUT верхнего уровня:

Отключить балансировку задержки для модели.

Включите балансировку задержки для подсистемы DUT верхнего уровня.

Деактивизация балансировки задержки для подсистемы в подсистеме DUT.

Когда в модели включена балансировка задержки, настройка балансировки задержки для отдельных подсистем игнорируется. Сведения о настройке балансировки задержки для подсистемы см. в разделе Настройка балансировки задержки для подсистемы.

Если балансировка задержки неуспешна, hdlcoder.optimizeDesign не удается оптимизировать созданный код HDL.

Следующие блоки и подсистемы не поддерживают балансировку задержки:

Срабатывающая подсистема

Атомная подсистема

HDLCosimulation

Дублирование типа данных

Уменьшение до нуля

Преобразование кадров

Земля

FFT HDL оптимизирован

Фильтр LMS

Ссылка на модель

В файл VCD

Величина - угол к комплексу

Блоки, которые имеют NoHDL архитектура не поддерживает балансировку задержки:

Кодер HDL не поддерживает балансировку задержки, если:

Существует несколько экземпляров атомной подсистемы в различных условных подсистемах.

В диалоговом окне «Параметры блока» атомной подсистемы можно установить для параметра «Упаковка функций» значение Nonreusable function.

Свойство блока BalureDelays для всех экземпляров атомной подсистемы или ссылки на модель получает другое значение.

Чтобы устранить эту ошибку, отключите BalanceDelays для всех экземпляров атомной подсистемы или ссылки на модель.

Блок находится внутри условной подсистемы и имеет задержки конвейера.

Подсистема с BlackBox

Свойство блока ImplementateLatency архитектуры имеет отрицательное значение.

Чтобы устранить эту ошибку, для параметра ImplementityLatency введите неотрицательное целое число.

Кодер HDL не поддерживает балансировку задержки, если:

Задержки вводятся в петлю обратной связи, и кодер HDL не может сбалансировать задержки тракта. Например, если применяется конвейер тактовой частоты внутри контура обратной связи, кодер HDL вводит задержку на тактовой частоте и может привести к сбою балансировки задержки.

Чтобы уменьшить количество задержек тактовой частоты, увеличьте коэффициент избыточной дискретизации.

Время выборки не является дискретным или отношение времени выборки самой быстрой к самой медленной скорости слишком велико.

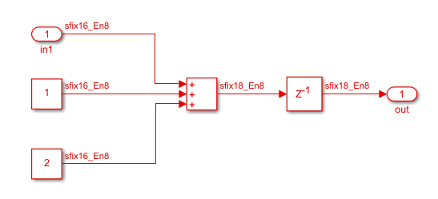

При наличии постоянных блоков в качестве входных данных в подсистеме DUT, для которой включена балансировка задержки, в модели проверки отображается начальное несоответствие моделирования. Рассмотрим эту модель в подсистеме DUT. Блок константы, который выдает значение 1 свойство блока HDL OutputPipeline имеет значение 1 .

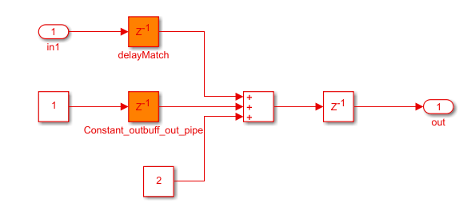

На этом рисунке показана созданная модель проверки. Вы видите, что балансировка задержки добавила соответствующую задержку к входному порту, чтобы сбалансировать регистр трубопровода, вставленный для блока задержки. Генератор кода не вставляет соответствующую задержку на параллельный путь, содержащий блок константы со значением 2 поскольку выходное значение блока является константой. Эта задержка не вставлена приводит к начальному несоответствию моделирования

Чтобы устранить несоответствие моделирования, в модели проверки вручную добавьте соответствующую задержку на выходе блока константы со значением 2.

Для просмотра информации о балансировке задержки в отчете перед созданием кода для каждой подсистемы или ссылки на модель включите отчет оптимизации. Чтобы включить этот отчет, на вкладке Код HDL (HDL Code) выберите Параметры отчета (Report Options), а затем выберите Создать отчет по оптимизации (Generate optimization report).

При создании кода для каждой подсистемы, ссылки на модель или функционального блока MATLAB кодер HDL создает отчет по оптимизации. В отчете выберите раздел «Балансировка задержки» отчета.

Отчет о балансировке задержки показывает изменения задержки, задержки конвейера и фазовой задержки на выходных портах, а также количество трубопроводов, добавленных на выходных портах для соответствия задержкам. При сбое балансировки задержки в отчете упоминаются нарушенные критерии и отображается ссылка на любой блок или подсистему, вызвавший сбой балансировки задержки.