Встроенная поддержка с плавающей запятой в Coder™ HDL позволяет создавать код из проекта с плавающей запятой. Если в конструкции имеются сложные математические и тригонометрические операции или данные с большим динамическим диапазоном, используйте собственную плавающую точку.

В модели Simulink ®:

Можно использовать типы данных и операции с плавающей запятой с половинной, одинарной и двойной точностью.

Можно использовать комбинацию целочисленных, фиксированных и плавающих операций. С помощью блоков преобразования типов данных можно выполнять преобразования между типами данных с плавающей и фиксированной точками.

Созданный код:

Соответствует стандарту IEEE-754 арифметики с плавающей запятой.

Не зависит от цели. Код можно развернуть на любом универсальном FPGA или ASIC.

Не требует блоков обработки с плавающей запятой или жестких блоков DSP с плавающей запятой на целевой ASIC или FPGA.

Кодер HDL поддерживает:

Математические и тригонометрические функции

Большое подмножество блоков Simulink

Денормальные числа

Настройка задержки оператора с плавающей запятой

Собственная технология с плавающей запятой в кодере HDL соответствует стандарту IEEE арифметики с плавающей запятой. Для базовых арифметических операций, таких как сложение, вычитание, умножение, деление и обратное, при создании кода HDL в собственном режиме с плавающей запятой полученные числовые результаты соответствуют исходной модели Simulink.

Некоторые расширенные математические операции, такие как экспоненциальные, логарифмические и тригонометрические операторы, имеют специфичное для машины поведение реализации, поскольку эти операторы используют повторяющиеся реализации на основе рядов Тейлора и выражений Ремеза. При использовании этих операторов в собственном режиме с плавающей запятой созданный код HDL может иметь относительно небольшие числовые отличия от модели Simulink. Эти числовые различия находятся в пределах допустимого диапазона и, следовательно, указывают на соответствие стандарту IEEE-754.

Для создания кода, соответствующего стандарту IEEE-754, кодер HDL поддерживает:

Округление до ближайшего режима округления

Денормальные числа

Исключения, такие как NaN (не число), Inf и Zero

Настройка ULP (единицы на последнем месте) и относительная точность

Дополнительные сведения см. в разделе Числовые соображения с собственной плавающей точкой.

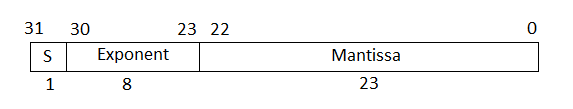

В стандарте IEEE 754-2008 число с плавающей запятой одинарной точности равно 32 битам. 32-битное число кодирует 1-битный знак, 8-битную экспоненту и 23-битную мантиссу.

Этот граф является нормализованным представлением для чисел с плавающей запятой. Фактическое значение нормального числа можно вычислить следующим образом:

− i) * 2 (e − 127)

Поле экспоненты представляет экспоненту плюс смещение 127. Размер мантиссы - 24 бита. Начальный бит равен 1, поэтому представление кодирует нижние 23 бита.

Использование типов с одной точностью для приложений, для которых требуется больший динамический диапазон, чем для типов с полуконкурсной точностью. Операции с одной точностью потребляют меньше памяти и имеют меньшую задержку, чем операции с двойной точностью.

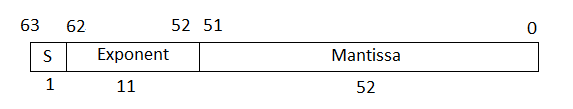

В стандарте IEEE 754-2008 число с плавающей запятой одинарной точности - 64 бита. 64-битное число кодирует 1-битный знак, 11-битную экспоненту и 52-битную мантиссу.

Поле экспоненты представляет экспоненту плюс смещение 1023. Размер мантиссы составляет 53 бита. Начальный бит равен 1, поэтому представление кодирует нижние 52 бита.

Используйте типы с двойной точностью для приложений, требующих большего динамического диапазона, точности и точности. Эти операции занимают большую площадь на FPGA и более низкую целевую частоту.

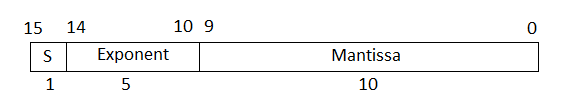

В стандарте IEEE 754-2008 число с плавающей запятой половинной точности равно 16 битам. 16-битное число кодирует 1-битный знак, 5-битную экспоненту и 10-битную мантиссу.

Поле экспоненты представляет экспоненту плюс смещение 15. Размер мантиссы - 11 бит. Начальный бит равен 1, поэтому представление кодирует нижние 10 битов.

Используйте типы половинной точности для приложений, которые требуют меньшего динамического диапазона, потребляют гораздо меньше памяти, имеют меньшую задержку и экономят ресурсы FPGA.

При использовании half типы, можно явно установить тип данных Output блоков на half вместо настройки по умолчанию Inherit: Inherit via internal rule. Сведения о том, как изменять параметры программно, см. в разделе Установка параметров блоков HDL для нескольких блоков программно.

Благодаря собственной поддержке с плавающей запятой HDL Coder поддерживает генерацию кода из моделей Simulink, содержащих сигналы с плавающей запятой и сигналы с фиксированной запятой. Возможно, потребуется смоделировать конструкцию с типами с плавающей запятой, чтобы:

Реализуйте алгоритмы, имеющие большой или неизвестный динамический диапазон, который может выходить за пределы диапазона представимых типов фиксированных точек.

Реализуйте сложные математические и тригонометрические операции, которые трудно спроектировать в фиксированной точке.

Получение более высокой точности и точности.

Конструкции с плавающей запятой потенциально могут занимать больше места на целевом оборудовании. В модели Simulink рекомендуется использовать типы данных с плавающей запятой в пути данных алгоритма и типы данных с фиксированной запятой в логике управления алгоритмом. На этом рисунке показан раздел модели Simulink, в которой используется Single и типы фиксированных точек. С помощью блоков преобразования типов данных можно выполнять преобразования между типами с одной точкой и с фиксированной точкой.