При разработке алгоритма с использованием Simscape™ коммутируемых линейных блоков можно запустить Simscape HDL Workflow Advisor для создания модели реализации HDL. При открытии модели реализации HDL появляется алгоритм HDL, моделирующий представление пространства состояний с помощью блоков Simulink ®, совместимых с генерацией кода HDL. Дополнительные сведения о помощнике Simscape HDL Workflow Advisor см. в разделе Задачи помощника Simscape HDL Workflow Advisor.

При создании кода HDL и развертывании модели установки на FPGA может потребоваться улучшить частоту выборки. Частота дискретизации зависит от следующих параметров:

Тактовая частота FPGA

Коэффициент избыточной выборки

Количество итераций решателя

![]()

Чтобы улучшить частоту дискретизации, необходимо максимизировать тактовую частоту FPGA и минимизировать коэффициент избыточной дискретизации и число итераций решателя. По мере улучшения частоты выборки убедитесь, что обновленная частота выборки эквивалентна фиксированному времени выборки, указанному для исходной модели Simscape с помощью блока Конфигурация решателя (Solver Configuration). Дополнительные сведения об использовании этого блока в модели перед запуском Simscape HDL Workflow Advisor см. в разделе Создание кода HDL для моделей Simscape.

В предыдущем разделе модель повышающего преобразователя используется в качестве примера для иллюстрации того, как можно изменить коэффициент избыточной дискретизации и количество итераций решателя для улучшения частоты дискретизации.

В этом примере модель повышающего преобразователя используется для иллюстрации изменения времени выборки в созданной модели реализации HDL и коэффициента избыточной выборки, который сохраняется в модели.

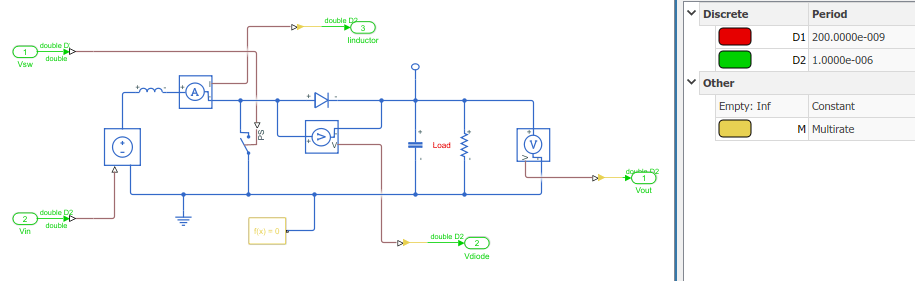

Откройте модель повышающего преобразователя. Чтобы узнать, как реализован повышающий преобразователь, откройте Simscape_system Подсистема. Для открытия модели повышающего преобразователя в окне команд MATLAB ® введите:

open_system('sschdlexBoostConverterExample') open_system('sschdlexBoostConverterExample/Simscape_system')

Вы видите, что модель работает во время образца 1e-6. Время выборки 200e-9 соответствует времени выборки источников, управляющих алгоритмом Simscape.

Откройте Simscape HDL Workflow Advisor для модели:

sschdladvisor('sschdlexBoostConverterExample')Запустите рабочий процесс в задачу Создать модель внедрения.

После выполнения этой задачи появится ссылка на созданную модель внедрения HDL. Щелкните ссылку, чтобы открыть модель внедрения HDL.

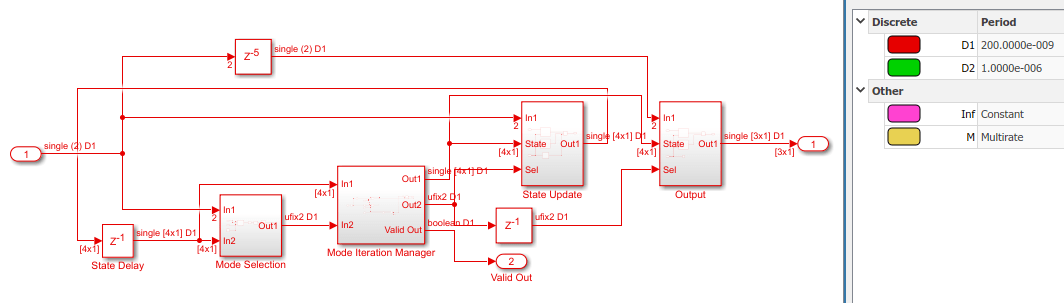

Моделирование модели внедрения ЛПВП. При переходе к модели HDL Algorithm Подсистема, вы видите, что модель использует single типы данных и выполнение во время выборки 200e-9, что является 5 в несколько раз быстрее, чем исходная модель Simscape.

Для просмотра параметров HDL, сохраненных в модели, выполните следующую команду:

hdlsaveparams('gmStateSpaceHDL_sschdlexBoostConverterExamp')

%% Set Model 'gmStateSpaceHDL_BoostConverter_HDL' HDL parameters

hdlset_param('gmStateSpaceHDL_BoostConverter_HDL', 'FloatingPointTargetConfiguration', ...

hdlcoder.createFloatingPointTargetConfig('NativeFloatingPoint' ...

, 'LatencyStrategy', 'MIN') ...

);

hdlset_param('gmStateSpaceHDL_BoostConverter_HDL', 'HDLSubsystem', ...

'gmStateSpaceHDL_BoostConverter_HDL');

hdlset_param('gmStateSpaceHDL_BoostConverter_HDL', 'MaskParameterAsGeneric', 'on');

hdlset_param('gmStateSpaceHDL_BoostConverter_HDL', 'Oversampling', 60);

% Set SubSystem HDL parameters

hdlset_param('gmStateSpaceHDL_BoostConverter_HDL/HDL Subsystem', 'FlattenHierarchy', 'on');

% Set SubSystem HDL parameters

hdlset_param('gmStateSpaceHDL_BoostConverter_HDL/HDL Subsystem/HDL Algorithm/State Update/Multiply State', ...

'SharingFactor', 1);

Сохраненные параметры HDL указывают на то, что модель имеет встроенный режим с плавающей запятой и использует коэффициент избыточной дискретизации, равный 60 и имеет значение «Стратегия задержки» MIN. Эти значения по умолчанию, выбранные для количества итераций решателя и комбинации параметров HDL, обеспечивают оптимальный компромисс между коэффициентом избыточной дискретизации и целевой тактовой частотой FPGA и улучшают частоту дискретизации. Для дальнейшего улучшения частоты дискретизации уменьшите число итераций и коэффициент избыточной дискретизации.

Для каждого режима в физической системе коммутируемый линейный рабочий процесс поступает в представление пространства состояний. Метод решателя является итеративным и выполняет несколько вычислений, чтобы определить правильный режим для следующего временного шага. После определенного числа итераций выходное значение следующего временного шага становится таким же, как и значение предыдущего временного шага. Эта непротиворечивость выходного значения указывает на правильное количество итераций решателя.

Помощник по умолчанию выбирает оптимальное значение для числа итераций решателя. См. раздел Использование числа итераций решателя. Чтобы улучшить частоту дискретизации, уменьшите число итераций решателя. Количество итераций решателя зависит от различных факторов, таких как сложность конструкции, количество режимов в конструкции, вычисляемых рабочим процессом, и т. д.

В задаче Создать модель реализации помощника Simscape HDL Workflow Advisor выполните следующие действия.

Начните с уменьшения числа итераций решателя до значения, например 3

Выберите Генерировать логику проверки для модели реализации, а затем создайте модель реализации HDL.

Смоделировать модель реализации HDL и открыть средство просмотра диагностики, чтобы убедиться, что в модели нет предупреждений или утверждений.

Если отображаются предупреждения или утверждения, это указывает на несоответствие моделирования, поскольку указанное число итераций решателя не подходит для вычисления необходимого количества режимов в конструкции «состояние-пространство». Устраните несоответствие, увеличив значение допуска логики проверки или число итераций решателя. Изменение точности с плавающей запятой на double не рекомендуется. Операции с двойной точностью имеют большие задержки и требуют большого коэффициента избыточной дискретизации для выделения достаточных задержек, что снижает частоту дискретизации. См. раздел Проверка модели реализации HDL в алгоритме Simscape.

Коэффициент избыточной дискретизации определяет коэффициент, на который тактовая частота FPGA кратна базовой частоте дискретизации модели реализации HDL. Модель реализации ЛПВП содержит контуры обратной связи и выполняет умножение больших матриц, которые имеют типы данных с плавающей запятой внутри контуров обратной связи. Чтобы учесть большую задержку, введенную этими операциями с плавающей запятой внутри петель обратной связи, генератор кода использует большое значение коэффициента избыточной дискретизации в сочетании с оптимизацией конвейеризации тактовой частоты в модели. Дополнительные сведения см. в разделе Стратегия 1: глобальная избыточная выборка.

Вы изменяете коэффициент избыточной дискретизации и стратегию задержки оператора с плавающей запятой в сочетании. Коэффициент избыточной выборки по умолчанию 60 и стратегия минимальной задержки дает оптимальную частоту дискретизации. Для достижения максимальной тактовой частоты FPGA используйте стратегию максимальной задержки. При указании этой стратегии задержки операции с плавающей запятой вводят максимальное количество задержек. Чтобы распределить эти задержки, увеличьте коэффициент избыточной выборки. Если увеличение тактовой частоты FPGA перевешивает увеличение коэффициента избыточной дискретизации, достигается более высокая частота дискретизации.

Чтобы изменить стратегию задержки и коэффициент избыточной выборки совместно в диалоговом окне Параметры конфигурации (Configuration parameters), выполните следующие действия.

На панели Создание кода HDL > Плавающая точка измените стратегию задержки на Max .

На панели «Создание кода HDL» > «Глобальные параметры» увеличьте коэффициент избыточной дискретизации до значения, например 100 в зависимости от сложности конструкции ЛПВП.

Для модели повышающего преобразователя для параметров по умолчанию Число итераций решателя (Number of solver iterations) установлено значение 5, Коэффициент избыточной выборки установлен в 60и для стратегии задержки установлено значение Min обеспечивает оптимальную частоту дискретизации.

sschdladvisor | simscape.findNonlinearBlocks (Simscape)