Смоделировать создаваемую конструкцию ЛПВП с использованием тестовых векторов с испытательного стенда с помощью указанного инструмента моделирования.

Запустите MATLAB для помощника по рабочим процессам HDL.

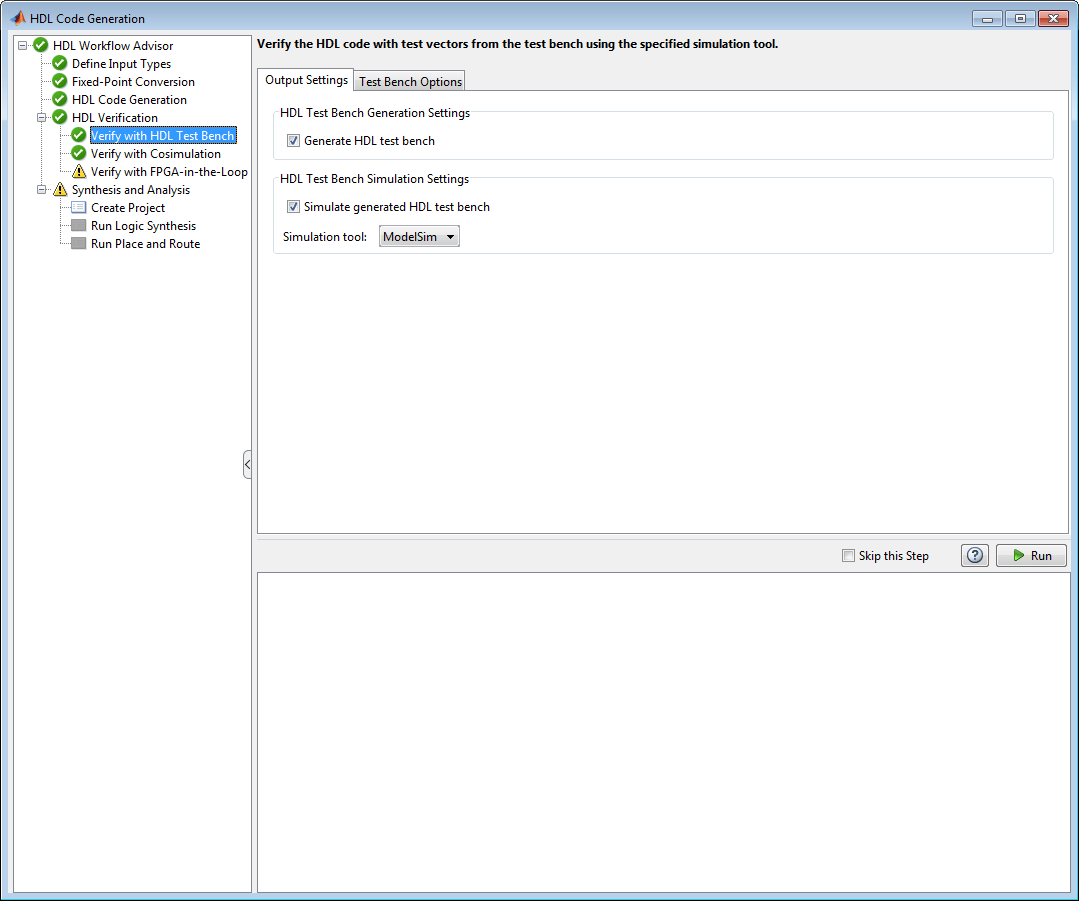

На шаге Проверка HDL (HDL Verification) щелкните Проверить с тестом HDL (Verify with HDL Test Stench).

Выберите Generate HDL test stench (Генерировать испытательный стенд ЛПВП).

Эта опция позволяет Coder™ HDL генерировать код стенда для тестирования HDL из тестового сценария MATLAB ® .

При необходимости выберите «Моделирование созданного стенда HDL». Эта опция позволяет MATLAB моделировать тестовый стенд HDL с помощью HDL DUT.

При выборе этой опции необходимо также выбрать инструмент «Моделирование».

В поле «Test Stench Options» (Параметры испытательного стенда) выберите и установите дополнительные параметры в соответствии с описаниями, приведенными в следующей таблице.

| Параметр испытательного стенда ЛПВП | Описание |

|---|---|

| Постфикс имени испытательного стенда | Укажите постфикс для имени испытательного стенда. |

| Силовые часы | Дать возможность испытательному стенду форсировать входные синхросигналы. |

| Время высокого тактового сигнала (нс) | Укажите количество наносекунд, в течение которого тактовый сигнал является высоким. |

| Малое время синхронизации (нс) | Укажите количество наносекунд, в течение которого тактовый сигнал находится на низком уровне. |

| Время удержания (нс) | Укажите время удержания входных сигналов и сигналов принудительного сброса. |

| Принудительное включение синхросигнала | Включить для принудительного включения часов. |

| Задержка включения синхронизации (в тактах) | Укажите время (в тактах) между отключением сброса и включением синхронизации. |

| Принудительный сброс | Дать возможность испытательному стенду форсировать входные сигналы сброса. |

| Длина сброса (в тактах) | Укажите время (в тактах) между утверждением и отменой сброса. |

| Удержание входных данных между образцами | Возможность хранения сигналов субскоростной передачи между выборками синхросигналов. |

| Интервал входных данных | Указывает количество тактовых циклов между утверждениями включения тактовых импульсов. Дополнительные сведения см. в разделе Указание частоты включения и переключения часов стенда тестирования. |

| Инициализация входов испытательного стенда | Включить инициализацию значений на входах тестового стенда перед передачей данных тестового стенда в DUT. |

| Многофайловый тестовый стенд | Позволяет разделить сформированный стенд на вспомогательные функции, данные и код стенда HDL. |

| Постфикс имени файла данных испытательного стенда | Укажите вектор символов для добавления к имени файла данных тестового стенда при создании многофайлового тестового стенда. |

| Постфикс эталонного стенда | Укажите вектор символов для добавления к именам опорных сигналов в коде испытательного стенда. |

| Игнорировать проверку данных (количество выборок) | Укажите количество выборок в начале моделирования, во время которого проверка выходных данных подавляется. |

| Предел итерации моделирования | Укажите максимальное количество тестовых образцов для использования при моделировании генерируемого кода ЛПВП. |

При необходимости выберите Пропустить этот шаг, если не требуется использовать тестовый стенд HDL для проверки HDL DUT.

Щелкните Выполнить (Run).

Если тестовый стенд и моделирование прошли успешно, на панели сообщений должны появиться сообщения, подобные следующим:

### Begin TestBench generation. ### Collecting data... ### Begin HDL test bench file generation with logged samples ### Generating test bench: mlhdlc_sfir_fixpt_tb.vhd ### Creating stimulus vectors... ### Simulating the design 'mlhdlc_sfir_fixpt' using 'ModelSim'. ### Generating Compilation Report mlhdlc_sfir_fixpt_vsim_log_compile.txt ### Generating Simulation Report mlhdlc_sfir_fixpt_vsim_log_sim.txt ### Simulation successful. ### Elapsed Time: 113.0315 sec(s)

При наличии ошибок эти сообщения отображаются на панели сообщений. Исправьте ошибки и нажмите кнопку Выполнить.