Распределенная арифметика (DA) - широко используемая методика реализации вычислений суммы произведений без использования множителей. Проектировщики часто используют DA для создания эффективной схемы умножения-накопления (MAC) для фильтров и других приложений DSP.

Основным преимуществом DA является его высокая вычислительная эффективность. DA распределяет операции умножения и накопления по блокам сдвига, таблицам поиска (LUT) и сумматорам таким образом, что обычные множители не требуются.

Кодер поддерживает DA в коде HDL, генерируемом для нескольких односкоростных и многоскоростных фильтров FIR для конструкций фильтров с фиксированной точкой. (См. раздел Требования и соображения по созданию распределенного арифметического кода.)

В этом разделе кратко описывается работа DA. Подробное обсуждение теоретических основ DA появляется в следующих публикациях:

Meyer-Baese, U., Digital Signal Processing with Field Programmable Gate Arrays, Second Edition, Springer, pp 88-94, 128-143.

White, S.A., Приложения распределенной арифметики для цифровой обработки сигналов: Учебное пособие. Журнал IEEE ASSP, том 6, № 3.

В реализации DA структуры КИХ-фильтра последовательность слов входных данных ширины W подается через параллельно-последовательный сдвиговый регистр. Этот канал создает сериализованный поток битов. Затем сериализованные данные подаются в сдвиговый регистр для всех битов. Этот сдвиговый регистр служит в качестве линии задержки, хранящей битовые последовательные выборки данных.

Линия задержки подключается (на основе размера входного слова W), чтобы сформировать W-bit адрес, который индексирует в таблицу поиска (LUT). LUT хранит возможные суммы частичных произведений в пространстве коэффициентов фильтра. Сдвиг и сумматор (накопитель масштабирования) следуют за LUT. Эта логика последовательно добавляет значения, полученные из LUT.

Поиск таблицы выполняется последовательно для каждого бита (в порядке значимости, начиная с LSB). В каждом такте результат LUT добавляется к накопленному и сдвинутому результату предыдущего цикла. Для последнего бита (MSB) результат поиска в таблице вычитается с учетом знака операнда.

Эта базовая форма DA является полностью последовательной, работающей на один бит за раз. Если последовательность входных данных W bits wide, то структура FIR принимает W тактовых циклов для вычисления выходного сигнала. Симметричные и асимметричные структуры FIR являются исключением, требующим W+1 , поскольку для обработки бита переноса предварительных сумматоров требуется один дополнительный тактовый цикл.

По своей сути битовый последовательный характер DA может ограничивать пропускную способность. Чтобы повысить пропускную способность, основной алгоритм DA может быть модифицирован для вычисления более одной битовой суммы одновременно. Число одновременно вычисленных сумм битов выражается как степень двух, называемая радиусом DA. Например, радиус DA равен 2 (2^1) указывает, что за один раз вычисляется одна битовая сумма. Радиус DA 4 (2^2) указывает, что одновременно вычисляются две битовые суммы, и так далее.

Для вычисления более одной битовой суммы за один раз кодер воспроизводит LUT. Например, для выполнения DA над двумя битами одновременно (radix 4) нечетные биты подаются на один LUT, а четные биты одновременно подаются на идентичный LUT. Результаты LUT, соответствующие нечетным битам, сдвигаются влево перед их добавлением к результатам LUT, соответствующим четным битам. Этот результат затем подается в масштабный накопитель, который сдвигает свое значение обратной связи на два места.

Обработка более одного бита за один раз вносит в операцию определенную степень параллелизма, что может улучшить производительность за счет площади. DARadix позволяет указать количество битов, обрабатываемых одновременно в DA.

Размер LUT увеличивается экспоненциально с порядком фильтра. Для фильтра с N коэффициенты, LUT должен иметь 2^N значения. Для фильтров более высокого порядка размер LUT должен быть уменьшен до разумных уровней. Чтобы уменьшить размер, можно разделить LUT на несколько LUT, называемых разделами LUT. Каждый раздел LUT работает с различным набором отводов. Результаты, полученные из разделов, суммируются.

Например, для фильтра 160 отводов размер LUT равен (2^160)*W биты, где W - размер слова данных LUT. Можно значительно уменьшить размер LUT, разделив LUT на 16 разделов LUT, каждый из которых принимает 10 входов (отводов). Это деление уменьшает общий размер LUT до 16*(2^10)*W биты.

Хотя разбиение LUT уменьшает размер LUT, архитектура использует больше сумматоров для суммирования данных LUT.

DALUTPartition позволяет указать способ секционирования LUT в DA.

Кодер позволяет управлять формированием кода DA с помощью DALUTPartition и DARadix свойства (или эквивалентные опции диалогового окна «Создание HDL»). Перед использованием этих свойств ознакомьтесь со следующими общими требованиями, ограничениями и другими соображениями при создании кода DA.

Кодер поддерживает DA в коде HDL, генерируемом для следующих односкоростных и многоскоростных фильтров FIR:

прямая форма (dfilt.dffir или dsp.FIRFilter)

прямая форма симметричная (dfilt.dfsymfir или dsp.FIRFilter)

прямая форма асимметричная (dfilt.dfasymfir или dsp.FIRFilter)

dsp.FIRDecimator

dsp.FIRInterpolator

Генерация кода DA поддерживается только для конструкций фильтров с фиксированной точкой.

Тракт данных в коде HDL, генерируемом для архитектуры DA, оптимизирован для вычислений с полной точностью. Фильтр приводит результат к размеру выходных данных на заключительном этапе. Если для объекта фильтра задано использование типов данных полной точности, числовые результаты моделирования сгенерированного кода HDL будут иметь значение bit-true для вывода исходного объекта фильтра.

Если объект фильтра имеет настроенные длины слов или дробей, сгенерированный код DA может давать числовые результаты, отличные от выходных данных исходного объекта фильтра.

DA игнорирует отводы, которые имеют нулевые коэффициенты, и соответственно уменьшает размер DA LUT.

Для симметричных и асимметричных КИХ-фильтров:

Для добавления значений данных отводов, которые имеют коэффициенты равной величины и/или противоположный знак, требуется предварительный сумматор битового уровня или предварительный блок. Для вычисления результата требуется один дополнительный тактовый цикл из-за дополнительного бита переноса.

Кодер использует преимущества симметрии фильтра. Эта симметрия существенно уменьшает размер DA LUT, поскольку эффективная длина фильтра для этих типов фильтров уменьшается вдвое.

Разделенные распределенные арифметические архитектуры реализуют внутренние тактовые частоты, превышающие входную. В таких реализациях фильтра имеются N циклы (N >= 2) базового тактового сигнала для каждой входной выборки. Можно указать, сколько тактовых циклов тестовый стенд удерживает значения входных данных в допустимом состоянии.

При выборе параметра Hold input data between samples (hold input data between samples - удерживайте входные данные между выборками) тестовый стенд сохраняет значения входных данных в допустимом состоянии для N тактовых циклов.

При снятии флажка «Удерживать входные данные между выборками» испытательный стенд сохраняет значения входных данных в допустимом состоянии только в течение одного тактового цикла. Для следующего N-1 циклы, испытательный стенд переводит данные в неизвестное состояние (выражается как 'X') до тех пор, пока не будет синхронизирована следующая входная выборка. Принудительное приведение входных данных в неизвестное состояние проверяет, что сгенерированный код фильтра регистрирует входные данные только в первом цикле.

generatehdl СвойстваДва свойства задают распределенные арифметические параметры generatehdl функция:

DALUTPartition - Количество и размер разделов таблицы подстановки (LUT).

DARadix - Число битов, обрабатываемых параллельно.

Можно использовать функцию помощника hdlfilterdainfo чтобы изучить возможные разделы и настройки radix для фильтра.

Примеры см. в разделе

Диалоговое окно Генерация HDL (Generate HDL) предоставляет несколько опций, связанных с генерацией кода DA.

Всплывающее меню «Архитектура», в котором можно включить генерацию кода DA и отобразить соответствующие параметры.

Раскрывающееся меню Задать сворачивание (Specify folding), в котором можно непосредственно указать коэффициент сворачивания или задать значение DARadix собственность.

Раскрывающееся меню Указать LUT (Specify LUT), которое позволяет непосредственно задать значение для DALUTPartition собственность. Можно также выбрать ширину адреса для LUT. При указании ширины адреса кодер при необходимости использует входные LUT.

В диалоговом окне Генерировать ЛПВП (Generate HDL) первоначально отображаются значения опций, связанных с DA по умолчанию, которые соответствуют текущей конструкции фильтра. Требования к настройке этих параметров см. в разделе DALUTPartition и DARadix.

Чтобы задать создание кода DA с помощью диалогового окна Генерировать HDL (Generate HDL), выполните следующие действия.

Создайте фильтр FIR (с помощью команд Filter Designer, Filter Builder или MATLAB ®), который соответствует требованиям, описанным в разделе «Требования и соображения по созданию распределенного арифметического кода».

Откройте диалоговое окно Генерировать ЛПВП (Generate HDL).

Выбрать Distributed Arithmetic (DA) во всплывающем меню «Архитектура».

При выборе этой опции под меню «Архитектура» отображаются соответствующие опции «Указать складывание» и «Указать LUT». На следующем рисунке показаны параметры DA по умолчанию для фильтра FIR прямой формы.

Выберите одну из следующих опций в раскрывающемся меню Указать складывание (Specify folding).

Folding factor (по умолчанию) Выберите коэффициент сворачивания из раскрывающегося меню справа от пункта «Указать сворачивание». Меню содержит исчерпывающий список параметров коэффициента складывания для фильтра.

DA radix: Выберите число одновременно обработанных битов, выраженное как степень 2. Дефолт DA radix значение равно 2, указывая обработку одного бита за раз или полностью последовательного DA. При необходимости установите DA radix в значение, отличное от значения по умолчанию.

Выберите одну из следующих опций в раскрывающемся меню Указать ЛУТ (Specify LUT).

Address width (по умолчанию): Выберите в раскрывающемся меню справа от пункта «Указать ЛУТ». Меню содержит исчерпывающий список значений ширины адресов LUT для фильтра.

Partition: Выберите или введите вектор, определяющий количество и размер секций LUT.

При необходимости установите другие параметры HDL и создайте код. Недопустимые или недопустимые значения для раздела LUT или DA Radix сообщаются во время генерации кода.

При взаимодействии с опциями Задать складывание (Specify folding) и Указать ЛУТ (Specify LUT) можно увидеть результаты выбора в трех полях, доступных только для отображения: Folding factor, Address width, и Total LUT size (bits).

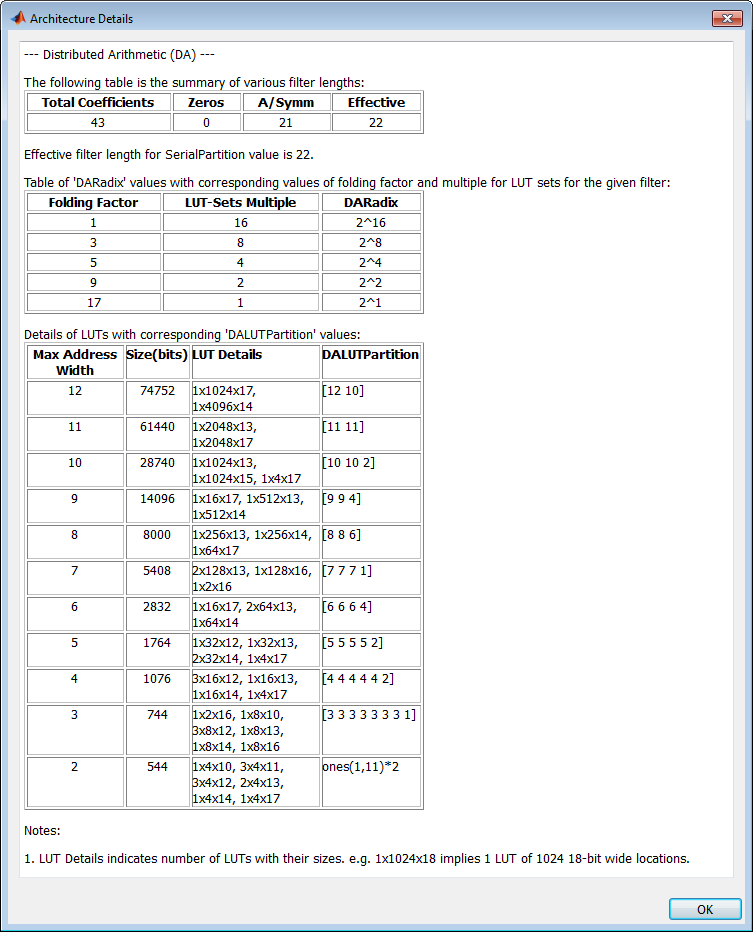

Кроме того, при щелчке на гиперссылке Показать сведения (View details) кодер отображает отчет, показывающий полные сведения об архитектуре DA для текущего фильтра, включая:

Длина фильтра

Полный список применимых коэффициентов складывания и их применение к наборам LUT

Таблица конфигураций LUT с общим размером LUT и подробностями LUT

На следующем рисунке показан типичный отчет.

Когда Distributed Arithmetic (DA) выбран в меню Architecture, некоторые другие опции HDL автоматически изменяются на настройки, соответствующие генерации кода DA:

Множители коэффициентов установлены в Multiplier и отключены.

Для стиля сумматора FIR установлено значение Tree и отключены.

Опция Add input register (Добавить входной регистр) (на панели Ports) выбрана и отключена. (Входной регистр, используемый как часть сдвигового регистра, используется в коде DA.)

Флажок Add output register (Добавить выходной регистр) (на панели Ports) установлен и отключен.