Используйте интерфейс HDL Coder™ UI или интерфейс командной строки для создания кода HDL для проектирования фильтра и тестового стенда. Пользовательский интерфейс генерирует файл тестового стенда VHDL или Verilog в зависимости от выбора языка для сгенерированного кода HDL. Можно указать другой язык испытательного стенда, выбрав опцию Язык испытательного стенда (Test stench language) на панели Испытательный стенд (Test Stench) диалогового окна Генерация HDL (Generate HDL). При использовании интерфейса командной строки нельзя указать другой язык тестового стенда.

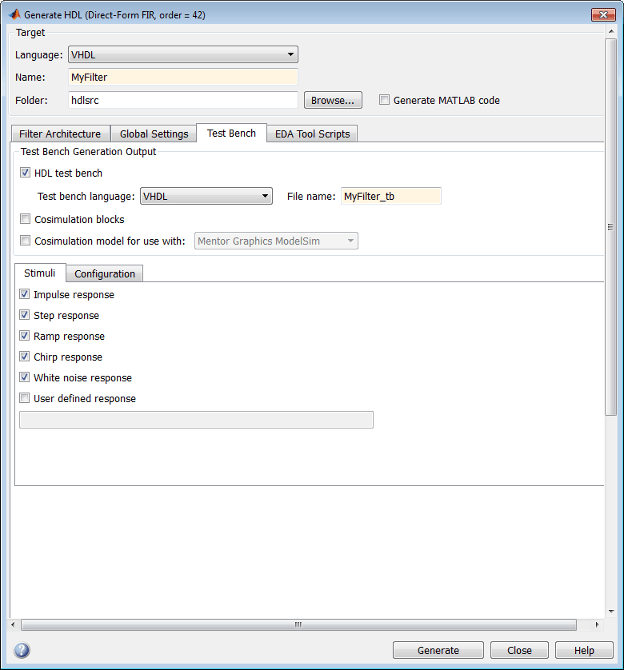

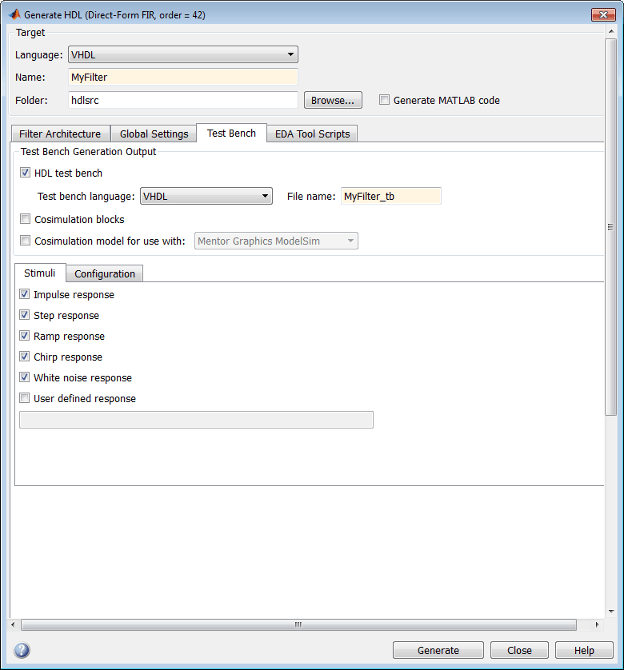

На следующем рисунке показаны настройки для создания файлов фильтра (VHDL) и тестового стенда (Verilog). MyFilter.vhd, и MyFilter_tb.v. В диалоговом окне также указывается расположение созданных файлов, в данном случае папка hdlsrc в текущей рабочей папке.

После нажатия кнопки Generate кодер отображает информацию о ходе выполнения, аналогичную следующей, в окне MATLAB ® Command Window:

### Starting VHDL code generation process for filter: MyFilter ### Generating: C:\Work\sl_hdlcoder_work\hdlsrc\MyFilter.vhd ### Starting generation of MyFilter VHDL entity ### Starting generation of MyFilter VHDL architecture ### HDL latency is 2 samples ### Successful completion of VHDL code generation process for filter: MyFilter ### Starting generation of VERILOG Test Bench ### Generating input stimulus ### Done generating input stimulus; length 3429 samples. ### Generating Test bench: C:\Work\sl_hdlcoder_work\hdlsrc\MyFilter_tb.v ### Please wait ... ### Done generating VERILOG Test Bench

Примечание

Длина входных выборок стимула варьируется от фильтра к фильтру. Например, значение 3429 в предшествующей последовательности сообщений не фиксирована; значение зависит от проверяемого фильтра.

Если вы вызываете generatehdl в интерфейсе командной строки задайте параметры создания кода и тестового стенда с парами имени и значения свойства. Также можно использовать функцию generatetbstimulus для возврата стимула тестового стенда к переменной рабочего пространства.

После создания фильтра и тестового стенда файлов HDL запустите симулятор. При запуске симулятора Mentor Graphics ® ModelSim ® появляется экран, подобный следующему :

После запуска симулятора установите текущую папку в папку, содержащую созданные файлы HDL.

Используя компилятор HDL, скомпилируйте созданный фильтр и протестируйте файлы HDL. В зависимости от языка созданного стенда тестирования и используемого симулятора, может потребоваться выполнить некоторые настройки предварительной компиляции. Например, в симуляторе Mentor Graphics ModelSim можно создать библиотеку конструкций для хранения скомпилированных объектов VHDL, пакетов, архитектур и конфигураций.

Следующая последовательность команд Mentor Graphics ModelSim изменяет текущую папку на hdlsrc, создает библиотеку проектирования workи компилирует код тестового стенда VHDL и фильтра. vlib создает работу библиотеки проекта и vcom команды инициируют компиляцию.

cd hdlsrc vlib work vcom MyFilter.vhd vcom MyFilter_tb.vhd

Примечание

Для кода стенда тестирования VHDL, имеющего реализацию с плавающей запятой (с двойной запятой), используйте компилятор, поддерживающий VHDL-93 или VHDL-02. Например, в симуляторе Mentor Graphics ModelSim укажите vcom с помощью команды -93 вариант. Не компилируйте созданный код тестового стенда с помощью компилятора VHDL-87. Испытательные стенды VHDL, использующие типы данных с двойной точностью, не поддерживают VHDL-87. В коде тестового стенда используется атрибут изображения, который доступен только в VHDL-93 или более поздних версиях.

На следующем экране отображается последовательность команд и информационные сообщения, отображаемые во время компиляции.

После компиляции созданных файлов HDL загрузите и запустите тестовый стенд. Процедура зависит от используемого симулятора. В симуляторе Mentor Graphics ModelSim загружается тестовый стенд для моделирования с помощью vsim команда. Например:

vsim work.MyFilter_tb

На следующем экране показаны результаты загрузки work.MyFilter_tb с vsim команда.

После загрузки проекта в симулятор рассмотрите возможность открытия окна отображения для мониторинга моделирования по мере запуска испытательного стенда. Например, в симуляторе Mentor Graphics ModelSim можно использовать add wave * команда для открытия окна волны для просмотра результатов моделирования в виде сигналов HDL.

Для запуска моделирования выполните команду start simulator. Например, в симуляторе Mentor Graphics ModelSim можно запустить моделирование с помощью run -all команда.

На следующем дисплее показаны add wave * используется для открытия окна волны и -run all используется для запуска моделирования.

Во время моделирования тестового стенда следите за сообщениями об ошибках. Если появляются сообщения об ошибках, интерпретируйте их как относящиеся к конструкции фильтра и применяемым опциям создания кода. Например, некоторые опции оптимизации HDL могут давать числовые результаты, которые отличаются от результатов, полученных исходным объектом фильтра. Для испытательных стендов ЛПВП сравниваются ожидаемые и фактические результаты. Если они отличаются (исключая указанное поле ошибки), возвращается сообщение об ошибке, аналогичное следующему:

Error in filter test: Expected xxxxxxxx Actual xxxxxxxx

Необходимо определить, ожидаются ли фактические результаты на основе настроек, указанных при создании кода HDL фильтра.

Примечание

Сообщение об ошибке, появляющееся на предыдущем экране, не помечает ошибку. Если сообщение содержит текст Test Complete, испытательный стенд был завершен без возникновения ошибки. Failure часть сообщения привязана к механизму, который кодер использует для завершения моделирования.

В следующем волновом окне показаны результаты моделирования в виде сигналов HDL.

Для создания тестового стенда ЛПВП:

Выберите панель Test Stench в диалоговом окне Generate HDL.

Выберите опцию испытательного стенда HDL, как показано на следующем рисунке.

Щелкните Генерировать (Generate), чтобы сгенерировать HDL и код тестового стенда.

Совет

По умолчанию выбран стенд HDL.

Альтернатива командной строки: generatehdl функция со свойством GenerateHDLTestBench для создания испытательного стенда ЛПВП.

Кодер получает имя файла тестового стенда, добавляя постфикс _tb к имени квантованного объекта фильтра. Расширение типа файла зависит от типа создаваемого стенда тестирования.

| Если испытательный стенд... | Расширение... |

|---|---|

| Файл Verilog | Определяется полем Расширение файла Verilog (Verilog file extension) в подпанели Общие (General) панели Глобальные настройки (Global Settings) диалогового окна Создание HDL (Generate HDL). |

| Файл VHDL | Определяется полем расширения файла VHDL на панели «Глобальные настройки» диалогового окна «Создание HDL» |

Файл помещается в папку, определенную опцией Папка (Folder) на панели Цель (Target) диалогового окна Создать HDL (Generate HDL).

Чтобы указать имя испытательного стенда, введите имя в поле Имя на панели Настройки испытательного стенда, как показано на следующем рисунке.

Примечание

При вводе символьного вектора, который является зарезервированным словом VHDL или Verilog, кодер корректирует идентификатор, добавляя зарезервированное слово postfix к символьному вектору.

Альтернатива командной строки: generatehdl собственность TestBenchName для указания имени испытательного стенда.

По умолчанию кодер генерирует один файл тестового стенда, содержащий вспомогательные функции тестового стенда, данные и код тестового стенда. Можно разбить эти элементы на отдельные файлы, выбрав опцию Многофайловый стенд тестирования (Multi-file test stench) в подменю Конфигурация (Configuration) панели Тестовый стенд (Test Bench) диалогового окна Генерировать HDL (Generate HDL).

При выборе параметра Multi-file test stench включается параметр Test stench data file name postfix. Имена файлов тестового стенда затем получаются из имени тестового стенда и настройки постфикса, TestBenchName_TestBenchDataPostfix.

Например, если тестовый стенд имеет имя my_fir_filt, а целевым языком является VHDL, имена файлов тестового стенда по умолчанию:

my_fir_filt_tb.vhd: код испытательного стенда

my_fir_filt_tb_pkg.vhd: пакет вспомогательных функций

my_fir_filt_tb_data.vhd: пакет данных

Если имя фильтра - my_fir_filt целевой язык - Verilog, имена файлов тестового стенда по умолчанию:

my_fir_filt_tb.v: код испытательного стенда

my_fir_filt_tb_pkg.v: пакет вспомогательных функций

my_fir_filt_tb_data.v: данные испытательного стенда

Альтернатива командной строки: generatehdl свойства MultifileTestBench, TestBenchDataPostfix, и TestBenchName для создания и присвоения имени отдельным функциям, данным и файлам кода тестового стенда.

На основе настроек по умолчанию кодер настраивает часы для тестового стенда фильтра таким образом, что:

Принудительное включение синхросигналов на активный высокий (1).

Устанавливает тактовый сигнал 1 после сброса сигнала сброса.

Заставляет входные сигналы синхронизации быть низкими (0) в течение 5 наносекунд и высокими (1) в течение 5 наносекунд.

Чтобы изменить эти параметры конфигурации часов:

Нажмите кнопку Configuration (Конфигурация) на панели Test stench (Испытательный стенд) диалогового окна Generate HDL (Генерировать ЛПВП).

На панели «Test Bench» (Испытательный стенд) выберите подпанель «Configuration» (Конфигурация).

Внесите следующие изменения в конфигурацию, как описано в следующей таблице:

| Если хочешь... | Тогда... |

|---|---|

| Деактивизация форсирования входных сигналов включения синхросигналов | Снимите флажок Force clock enable. |

| Деактивизация форсирования входных синхросигналов | Очистить часы силы. |

| Сброс количества наносекунд, в течение которых испытательный стенд обеспечивает низкий уровень входных синхросигналов (0) | Укажите положительное целое или двойное число (не более 6 значащих цифр после десятичной запятой) в поле Clock low time. |

| Сброс количества наносекунд, в течение которых испытательный стенд обеспечивает высокий уровень входных синхросигналов (1) | Укажите положительное целое или двойное число (не более 6 значащих цифр после десятичной запятой) в поле Время таймера. |

| Измените время задержки, прошедшее между сбросом сигнала сброса и установлением сигнала разрешения синхронизации. | Укажите положительное целое число в поле Clock enable delay. |

На следующем рисунке показаны применимые опции.

Альтернатива командной строки: generatehdl свойства ForceClock, ClockHighTime, ForceClockEnable, и TestBenchClockEnableDelay для изменения конфигурации часов испытательного стенда.

На основе настроек по умолчанию кодер настраивает сброс для тестового стенда фильтра таким образом, что:

Принудительно переводит входные сигналы в активное состояние (1). (Установите входные уровни сброса тестового стенда с помощью опции Reset asserted level).

Устанавливает сброс входных сигналов в течение 2 тактовых циклов.

Применяет время удержания 2 наносекунды для входных сигналов сброса.

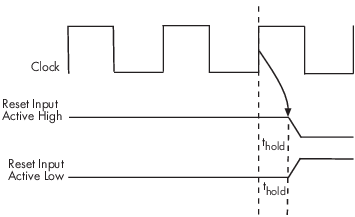

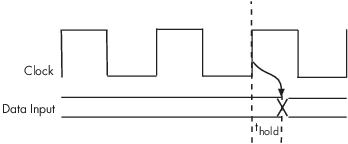

Время удержания - это время, в течение которого испытательный стенд удерживает входные сигналы сброса за фронтом нарастания тактового сигнала. На рисунке показано применение времени удержания (thold) для сброса входных сигналов в активном высоком и активном низких случаях. Испытательный стенд устанавливает сброс после некоторых начальных тактовых циклов, определенных опцией Reset length. По умолчанию отображается значение Reset length, равное 2 тактам.

Примечание

Время удержания применяется к входным сигналам сброса только в том случае, если активизировано форсирование входных сигналов сброса.

В следующей таблице представлены параметры конфигурации сброса.

| Если хочешь... | Тогда... |

|---|---|

| Деактивизация форсирования входных сигналов сброса | Снимите флажок Force reset на панели Test Stench диалогового окна Generate HDL (генерировать ЛПВП). |

| Изменение периода времени (в тактах), в течение которого инициируется сброс | Установите для параметра Reset length (в тактах) целое число, большее или равное 0. Эта опция расположена на панели «Испытательный стенд» диалогового окна «Создание ЛПВП». |

| Изменение значения сброса на активный низкий (0) | Выбрать Active-low из меню Reset asserted level на панели Global Settings диалогового окна Generate HDL (Создать HDL) (см. раздел Установка уровня Asserted Level для входного сигнала сброса) |

| Установка времени удержания | Укажите положительное целое или двойное число (максимум 6 значащих цифр после десятичной запятой), представляющее наносекунды, в поле Время удержания. При изменении времени удержания обновляется значение времени (ns) установки. Значение времени (ns) установки, вычисленное как (clock period - HoldTime) в наносекундах. Эти опции находятся на панели «Испытательный стенд» диалогового окна «Создание HDL». |

На следующих рисунках показаны применимые опции.

Примечание

Настройки времени удержания и времени установки также применяются к входным сигналам данных.

Альтернатива командной строки: generatehdl свойства ForceReset, ResetLength, и HoldTime для перенастройки сбросов стенда.

По умолчанию кодер применяет время удержания 2 наносекунды для входных сигналов данных фильтра. Время удержания - это время, в течение которого входные сигналы данных должны удерживаться за фронтом нарастания тактового сигнала. На следующем рисунке показано применение времени удержания (thold) для входных сигналов данных.

Чтобы изменить настройку времени удержания,

Перейдите на вкладку Test Stench (Испытательный стенд) в диалоговом окне Generate HDL (Генерировать ЛПВП).

На панели «Test Bench» (Испытательный стенд) выберите подпанель «Configuration» (Конфигурация).

Укажите положительное целое или двойное число (максимум 6 значащих цифр после десятичной запятой), представляющее наносекунды, в поле Время удержания. На следующем рисунке время удержания устанавливается равным 2 наносекундам.

При изменении времени удержания значение времени (ns) установки обновляется. Кодер вычисляет значение времени (ns) установки как (clock period - HoldTime) в наносекундах. Время настройки (ns) является полем только для отображения.

Примечание

При включении форсирования входных сигналов сброса настройки времени удержания и времени установки также применяются к сигналам сброса.

Альтернатива командной строки: generatehdl собственность HoldTime для настройки времени удержания.

Настройки, обеспечивающие оптимизацию, могут генерировать код тестового стенда, который дает числовые результаты, отличающиеся от результатов, полученных исходным объектом фильтра. Эти опции включают в себя:

Оптимизация для ЛПВП

Для стиля сумматора FIR установлено значение Tree

Добавление регистров трубопроводов для КИХ, асимметричных КИХ и симметричных КИХ-фильтров

Чтобы учесть различия в числовых результатах, рассмотрите возможность установки запаса ошибки для созданного стенда. Запас погрешности - это количество младших битов, игнорируемых тестовым стендом при сравнении результатов. Чтобы задать поле ошибки, выполните следующие действия.

Выберите панель Test Stench в диалоговом окне Generate HDL.

На панели «Test Bench» (Испытательный стенд) выберите подпанель «Configuration» (Конфигурация).

Для фильтров с фиксированной точкой начальное поле Error margin (bits) имеет значение по умолчанию 4. Чтобы изменить поле ошибки, введите целое число в поле Error margin (bits). На следующем рисунке для поля ошибки установлено значение 4 биты.

Альтернатива командной строки: generatehdl собственность ErrorMargin для указания количества битов допустимой ошибки.

По умолчанию начальное значение, управляемое на входах испытательного стенда, равно 'X' (неизвестно). Кроме того, можно указать, что начальное значение, управляемое входами испытательного стенда, равно 0, следующим образом:

Выберите панель Test Stench в диалоговом окне Generate HDL.

На панели «Test Bench» (Испытательный стенд) выберите подпанель «Configuration» (Конфигурация).

Установка начального входного значения стенда 0выберите опцию Initialize test stech input (Инициализация входных данных стенда для тестирования).

Установка начального входного значения стенда 'X', снимите флажок Initialize test stech input.

Альтернатива командной строки: generatehdl собственность InitializeTestBenchInputs установить начальное входное значение стенда.

По умолчанию кодер генерирует тестовый стенд фильтра, который включает в себя стимулы, соответствующие данному типу фильтра. Однако при необходимости можно настроить настройки стимулов или указать пользовательские стимулы.

Чтобы изменить стимулы, включенные в тестовый стенд, выберите один или несколько типов ответа в подпанели Стимулы (Stimuli) вкладки Тестовый стенд (Test stench) диалогового окна Генерировать ЛПВП (Generate HDL). На рисунке выделена эта панель диалогового окна.

Если выбран вариант Отклик пользователя (User defined response), укажите выражение или функцию, которая возвращает вектор значений, применяемых к фильтру. Значения, указанные в векторе, квантуются и масштабируются на основе настроек квантования фильтра.

Альтернатива командной строки: generatehdl свойства TestBenchStimulus и TestBenchUserStimulus чтобы настроить настройки стимулов.

Данные опорного сигнала представлены в виде массивов в сформированном коде испытательного стенда. К сгенерированным именам сигналов добавляется вектор символов, заданный постфиксом эталонного стенда. Значение по умолчанию: '_ref'.

Постфикс можно установить в значение, отличное от '_ref'. Чтобы изменить этот параметр:

Выберите панель Test Stench в диалоговом окне Generate HDL.

На панели «Test Bench» (Испытательный стенд) выберите подпанель «Configuration» (Конфигурация).

Введите новый вектор символов в поле Test stench reference postfix, как показано на следующем рисунке.

Альтернатива командной строки: generatehdl собственность TestBenchReferencePostfix для изменения вектора символов постфикса.