Создание и настройка стенда для тестирования ЛПВП

Свойства тестового стенда HDL позволяют включить и настроить создание тестового стенда.

Укажите эти свойства в качестве аргументов «имя-значение» для generatehdl функция. Name - имя свойства и Value - соответствующее значение. Можно указать несколько аргументов «имя-значение» в любом порядке как 'Name1',Value1,...,'NameN',ValueN.

Например:

fir = dsp.FIRFilter('Structure','Direct form antisymmetric'); generatehdl(fir,'InputDataType',numerictype(1,16,15), ... 'GenerateHDLTestBench','on','MultifileTestBench','on');

GenerateHDLTestBench - Создать стенд для испытаний ЛПВП'off' (по умолчанию) | 'on'Создание стенда для тестирования HDL для кода фильтра HDL, указанного как 'off' или 'on'. Стенд применяет сгенерированные входные стимулы к сгенерированному коду фильтра и сравнивает выходные данные с сохраненными результатами моделирования MATLAB ®.

TestBenchName - Наименование файла сформированного стендаfiltername_tbИмя файла сформированного стенда, указанное как filtername_tbfiltername - имя созданного объекта VHDL или модуля Verilog. Можно настроить это имя, установив Name собственность. Кодер добавляет расширение типа файла к имени тестового стенда, как указано в VerilogFileExtension или VHDLFileExtension свойства. Файл тестового стенда находится в папке, указанной TargetDirectory собственность.

Если в целевом языке указано значение, являющееся зарезервированным словом, кодер добавляет постфикс _rsvd к этому значению. Значение постфикса можно обновить с помощью ReservedWordPostfix собственность. Дополнительные сведения см. в разделе Разрешение конфликтов зарезервированных слов HDL.

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on'.

ErrorMargin - Запас погрешности для сравнения стенда в битах4 (по умолчанию) | положительное целое числоЗапас ошибки для сравнения стенда в битах, указанный как 4 или положительное целое число. Стенд сравнивает результаты с эталонными сигналами. Следующие оптимизации HDL могут генерировать код тестового стенда, который дает числовые результаты, отличающиеся от результатов, полученных с помощью исходной функции фильтра:

FIRAdderStyle установить в значение 'tree' или 'pipelined'

AddPipelineRegisters с помощью КИХ, асимметричных КИХ и симметричных КИХ-фильтров

Поле ошибки указывает допустимое минимальное количество битов, на которое числовые результаты могут отличаться перед выдачей предупреждения тестовым стендом.

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on'.

MultifileTestBench - Формирование многофайлового стенда'off' (по умолчанию) | 'on'Создание многофайлового испытательного стенда, указанного как 'off' или 'on'. Если для этого свойства установлено значение 'on'кодер генерирует отдельные файлы для кода тестового стенда, вспомогательных функций и данных тестового стенда вместо одного файла. Имена файлов получены из TestBenchName и TestBenchDataPostfix свойства. Например, если имя созданного объекта VHDL или модуля Verilog равно my_fir_filt, имена файлов тестового стенда по умолчанию:

my_fir_filt_tb - Код испытательного стенда

my_fir_filt_tb_pkg - Пакет вспомогательных функций

my_fir_filt_tb_data - Пакет данных тестового вектора

Кодер добавляет к этим именам файлов расширение типа файла, определенное VerilogFileExtension или VHDLFileExtension свойства.

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on'.

TestBenchDataPostfix - Постфикс к имени файла данных испытательного стенда'_data' (по умолчанию) | символьный вектор | строковый скалярПостфикс к имени файла данных испытательного стенда, указанный как '_data', символьный вектор или строковый скаляр. Кодер генерирует файл данных тестового стенда с именем файла, полученным путем добавления этого постфикса к TestBenchName значение свойства.

Это свойство применяется только в том случае, если GenerateHDLTestBench и MultifileTestBench свойства имеют значение 'on'.

TestBenchReferencePostfix - Postfix к именам опорных сигналов'_ref' (по умолчанию) | символьный вектор | строковый скалярPostfix to reference signal names, указано как '_ref', вектор символов или строковый скаляр. Кодер применяет этот постфикс к опорному выходному сигналу на испытательном стенде. Кодер представляет данные опорного сигнала в виде массивов.

CONSTANT filter_out_expected : filter_in_data_log_type :=

(

-2.4228738523269194E-03,

-2.0832449820793104E-03,

6.7703446401186345E-03,...SIGNAL filter_out_ref : real := 0.0; -- double ... filter_out_ref <= filter_out_expected(TO_INTEGER(filter_out_addr));

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on'.

ClockHighTime - Период, в течение которого стенд приводит в действие входные синхросигналы с высоким (1) в нс5 (по умолчанию) | положительный скалярПериод, в течение которого стенд приводит в действие входные синхросигналы высокого (1) значения в нс, указанные как 5 или положительный скаляр. Можно указать целое число или значение с плавающей запятой с двойной точностью, не более 6 значащих цифр после десятичной запятой.

Это свойство применяется только в том случае, если GenerateHDLTestBench и ForceClock свойства имеют значение 'on'.

ClockLowTime - Период, в течение которого испытательный стенд возбуждает входные синхросигналы с низким (0) в нс5 (по умолчанию) | положительный скалярПериод, в течение которого испытательный стенд приводит в действие входные синхросигналы с низким (0) в нс, указанные как 5 или положительный скаляр. Можно указать целое число или значение с плавающей запятой с двойной точностью, не более 6 значащих цифр после десятичной запятой.

Это свойство применяется только в том случае, если GenerateHDLTestBench и ForceClock свойства имеют значение 'on'.

ForceClock - Входные сигналы тактовых импульсов испытательного стенда'on' (по умолчанию) | 'off'Испытательный стенд воздействует на входные сигналы синхросигналов, определяемые одним из следующих параметров:

'on' - Испытательный стенд принудительно подает входные сигналы синхросигнала. Значения ClockHighTime и ClockLowTime свойства управляют формой тактового сигнала.

'off' - Необходимо управлять входными синхросигналами от внешнего источника.

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on'.

ForceClockEnable - Входные сигналы включения синхросигналов испытательного стенда'on' (по умолчанию) | 'off'Испытательный стенд обеспечивает включение входных сигналов синхросигналов, определяемых одним из следующих параметров:

'on' - Испытательный стенд принудительно подает входные сигналы включения синхронизации. Полярность активная высокая (1). Этот сигнал также подчиняется установке HoldTime собственность.

'off' - Необходимо управлять входными сигналами включения синхронизации от внешнего источника.

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on'.

TestBenchClockEnableDelay - Циклы синхронизации между отключением сброса и включением синхронизации1 (по умолчанию) | положительное целое числоЦиклы синхронизации между отменой сброса и включением синхронизации, указанные как 1 или положительное целое число. Испытательный стенд ожидает этого количества циклов между сбросом сигнала сброса и установлением сигнала разрешения синхронизации. HoldTime также применяется свойство.

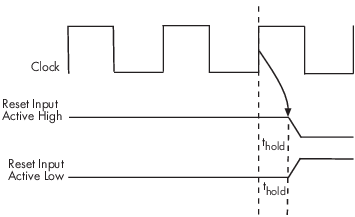

На рисунке испытательный стенд сбрасывает сигнал с высоким уровнем активности после интервала, обозначенного Hold Time. Затем испытательный стенд устанавливает включение тактового сигнала после дополнительного интервала с меткой Clock enable delay.

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on'.

ForceReset - Испытательный стенд форсирует входные сигналы сброса'on' (по умолчанию) | 'off'Испытательный стенд форсирует входные сигналы сброса, указанные как одно из следующих:

'on' - Испытательный стенд принудительно подает входные сигналы сброса. Можно также указать время удержания для управления временем сброса путем установки HoldTime собственность.

'off' - Необходимо управлять входными сигналами сброса от внешнего источника.

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on'.

HoldTime - Время удержания значений входных данных и сигналов принудительного сброса в нс2 (по умолчанию) | положительный скалярВремя удержания значений входных данных и сигналов принудительного сброса в нс, указанных как 2 или положительный скаляр. Испытательный стенд содержит входные сигналы данных фильтра и входные сигналы принудительного сброса в течение заданного интервала времени, прошедшего мимо нарастающего фронта синхронизации. Можно указать целое число или значение с плавающей запятой с двойной точностью, не более 6 значащих цифр после десятичной запятой.

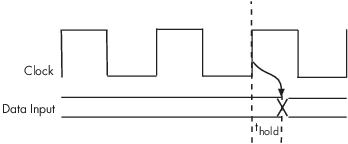

На следующих рисунках показано применение времени удержания, thold, для сигналов сброса и ввода данных. Сигналы принудительно активируются на высоком и активном низком уровне. ResetLength свойство имеет значение 2 цикла, и испытательный стенд выдает сигнал сброса в общей сложности на 2 цикла плюс пороговое значение.

Время удержания входных сигналов сброса

Время удержания сигналов ввода данных

Это свойство применяется только в том случае, если GenerateHDLTestBench и ForceReset свойства имеют значение 'on'.

ResetLength - количество тактовых циклов, в течение которых испытательный стенд подает сигнал сброса;2 (по умолчанию) | положительное целое числоКоличество тактовых циклов, в течение которых испытательный стенд подает сигнал сброса, указанный как 2 или положительное целое число.

Стенд тестирования по умолчанию устанавливает сигнал сброса с высоким уровнем активности в течение 2 тактовых циклов.

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on'.

HoldInputDataBetweenSamples - Испытательный стенд содержит входные данные сверхчасовых фильтров в допустимом состоянии'off' (по умолчанию) | 'on'Стенд содержит входные данные сверхчасовых фильтров в допустимом состоянии, указанном как 'off' или 'on'. Последовательные архитектуры и распределенные арифметические архитектуры реализуют внутренние тактовые частоты, превышающие входную. В таких реализациях фильтра базовый тактовый сигнал работает N циклы (N >= 2) для каждого входного образца. Это свойство относится к числу тактовых циклов, в которых испытательный стенд удерживает входные данные в допустимом состоянии.

'off' - Испытательный стенд сохраняет значения данных в допустимом состоянии в течение одного тактового цикла. Для следующего N-1 циклы, данные находятся в неизвестном состоянии (выражается как 'X'). Принудительное приведение входных данных в неизвестное состояние проверяет, что сгенерированный код фильтра регистрирует входные данные только в первом цикле.

'on' - Испытательный стенд содержит значения входных данных в действительном состоянии N тактовых циклов.

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on'.

InitializeTestBenchInputs - Инициализировать вход стенда'off' (по умолчанию) | 'on'Инициализируйте вход стенда, указанный как одно из следующих:

'off' - В начале моделирования испытательный стенд приводит в неизвестное состояние (выражается как 'X') к входным портам.

'on' - В начале моделирования испытательный стенд подает нули на входные порты.

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on'.

TestBenchStimulus - Входные стимулы, применяемые к формируемому фильтру{'impulse','step','ramp','chirp','noise'} (по умолчанию) | массив ячеек символьных векторов | строковый массивВходные стимулы, применяемые к формируемому фильтру, указанные как {'impulse','step','ramp','chirp','noise'}, массив ячеек символьных векторов или строковый массив. Ячейка или строковый массив должен быть подмножеством набора стимулов по умолчанию. Можно указать комбинации стимулов в любом порядке. Например:

generatehdl(filt,'InputDataType',numerictype(1,16,15), ... 'GenerateHDLTestbench','on', ... 'TestBenchStimulus',{'ramp','impulse','noise'})

TestBenchUserStimulus собственность. Когда TestBenchUserStimulus является непустым вектором, он имеет приоритет над TestBenchStimulus.

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on'.

TestBenchUserStimulus - Пользовательский входной стимул[] (пустой вектор) (по умолчанию) | вектор входных данныхПользовательский входной стимул, указанный как одно из следующих значений:

[] (пустой вектор) - испытательный стенд использует TestBenchStimulus для формирования входных данных.

Вектор входных данных - испытательный стенд применяет этот входной стимул к генерируемому фильтру. Можно указать вектор как вызов функции, возвращающий вектор.

Например, этот вызов функции генерирует квадратную волну с частотой выборки 8 бит в секунду (Fs/8).

repmat([1 1 1 1 0 0 0 0],1,10)

generatehdl.generatehdl(filt,'InputDataType',numerictype(1,16,15), ... 'GenerateHDLTestbench','on', ... 'TestBenchUserStimulus',repmat([1 1 1 1 0 0 0 0],1,10))

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on'.

TestBenchCoeffStimulus - Стимулирующий коэффициент для фильтров FIR или IIR[] (пустой вектор) (по умолчанию) | вектор коэффициентов (только фильтры FIR) | массив ячеек значений коэффициентов и шкалы (только фильтры IIR)Коэффициент стимула для КИХ или БИХ фильтров, определяемый как один из следующих:

[] (пустой вектор) - испытательный стенд использует коэффициенты объекта фильтра и форсирует входные стимулы. Эта последовательность показывает ответ на входные стимулы и проверяет, что интерфейс записывает один набор коэффициентов в память коэффициентов, как ожидалось.

Вектор коэффициентов (только FIR-фильтры) - Фильтр обрабатывает входные стимулы дважды: один раз с коэффициентами объекта фильтра и один раз с стимулом коэффициента. Тестовый стенд проверяет, что интерфейс записывает два различных набора коэффициентов в память коэффициентов. Дополнительные сведения см. в разделе Создание тестового стенда для программируемых коэффициентов КИХ.

Массив ячеек значений коэффициента и шкалы (только фильтры БИХ) - указывает стимул как вектор столбца значений шкалы и матрицу секции второго порядка (SOS). Фильтр обрабатывает входные стимулы дважды: один раз с коэффициентами объекта фильтра и один раз с стимулом коэффициента. Тестовый стенд проверяет, что интерфейс записывает два различных набора коэффициентов в память коэффициентов. Дополнительные сведения см. в разделе Создание тестового стенда для программируемых коэффициентов БИХ.

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on' и CoefficientSource свойство имеет значение 'ProcessorInterface'.

TestBenchFracDelayStimulus - Дробная задержка для односкоростных фильтров Фэрроу'RandSweep' | 'RampSweep'Дробный стимул задержки для односкоростных фильтров Фэрроу, указанный как один из следующих:

Постоянное числовое значение - испытательный стенд управляет входным сигналом дробной задержки с постоянным значением, полученным от объекта фильтра.

Вектор числовых значений - испытательный стенд управляет входным сигналом дробной задержки от этого вектора. Можно указать вектор как вызов функции, возвращающий вектор. Вектор должен иметь ту же длину, что и входной сигнал испытательного стенда.

'RandSweep' - Испытательный стенд управляет входным сигналом дробной задержки, используя вектор значений, постепенно увеличивающийся в диапазоне от 0 до 1. Этот стимулирующий сигнал имеет ту же длительность, что и входной сигнал к фильтру, но изменяется с более низкой скоростью. Каждое значение дробной задержки, полученное из вектора, сохраняется в течение 10% от общей длительности входного сигнала.

'RampSweep' - Испытательный стенд управляет входным сигналом дробной задержки с использованием вектора случайных значений от 0 до 1. Этот сигнал стимула имеет ту же длительность, что и входной сигнал к фильтру, но он изменяется с более медленной скоростью. Каждое значение дробной задержки, полученное из вектора, сохраняется в течение 10% от общей длительности входного сигнала.

См. раздел Свойства генерации кода для фильтров Farrow.

Это свойство применяется только в том случае, если GenerateHDLTestBench свойство имеет значение 'on'.

TestBenchRateStimulus - Входной стимул скорости для фильтров CICВходной стимул скорости для фильтров CIC (CIC), определяемый как максимальный коэффициент изменения скорости или целое число. Если не указать TestBenchRateStimulusкодер предполагает, что фильтр спроектирован с максимальной ожидаемой скоростью. Коэффициент прореживания (для прореживателей CIC) или коэффициент интерполяции (для интерполяторов CIC) устанавливается на этот максимальный коэффициент изменения скорости.

См. раздел Фильтры CIC с переменной скоростью.

Это свойство применяется только к фильтрам CIC переменной скорости, если GenerateHDLTestBench и AddRatePort свойства имеют значение 'on'.

GenerateCosimBlock - Создание модели Simulink ® блоков косимуляции ЛПВП'off' (по умолчанию) | 'on'Создание модели симулятора блоков косимуляции ЛПВП, указанной как 'off' или 'on'. Созданная модель Simulink содержит два блока косимуляции HDL: один для Mentor Graphics ® ModelSim ® и один для Cadence Incisive ®. Кодер настраивает эти блоки в соответствии с портом и интерфейсом типа данных выбранного фильтра. Используйте эти блоки для имитации конструкции с помощью требуемого имитатора ЛПВП в Simulink.

Для этой функции требуется лицензия HDL Verifier™.

GenerateCosimModel - Создание модели Simulink реализованного фильтра и блока косимуляции ЛПВП'none' (по умолчанию) | 'ModelSim' | 'Incisive'Создание модели Simulink реализованного фильтра и блока Cosimulation HDL, указанного как 'none', 'ModelSim', или 'Incisive'. При установке для этого свойства значения 'ModelSim' или 'Incisive', кодер генерирует и открывает модель Simulink. Модель содержит блок косимуляции ЛПВП для выбранного симулятора и поведенческую реализацию конструкции фильтра. Модель применяет сгенерированные входные стимулы и сравнивает выходные данные имитатора EDA с выходными данными подсистемы поведенческого фильтра. Можно настроить входной стимул и запас погрешности, используя те же свойства, что и для созданного стенда HDL.

См. раздел Создание модели симулятора для косимуляции с помощью имитатора ЛПВП.

Для этой функции требуется лицензия HDL Verifier.

При использовании функции fdhdltool для создания кода HDL можно задать соответствующие свойства на вкладке «Test Stench» в диалоговом окне «Generate HDL».

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.