Для FPGA-in-the-loop можно использовать собственную сертифицированную плату FPGA, даже если она отсутствует в списке предварительно зарегистрированных плат FPGA, поставляемых MathWorks ®. С помощью мастера создания платы FPGA можно создать файл определения платы, описывающий пользовательскую плату FPGA.

В этом примере можно выполнить процедуру создания файла определения платы для KC705 оценочной платы Xilinx ® для использования с моделированием FIL.

Проверьте спецификацию платы, чтобы получить следующую информацию:

Интерфейс FPGA с микросхемой Ethernet PHY

Имена и номера контактов синхросигналов

Сброс имен и номеров выводов

В этом примере вам предоставляется необходимая информация. Как правило, этот тип информации содержится в файле спецификации платы. В этом примере используется KC705 Evaluation Board для руководства пользователя Kintex-7 FPGA, опубликованного компанией Xilinx.

Для проверки необходимо использовать Xilinx или Altera ®. Используйте hdlsetuptoolpath (HDL Coder) для настройки инструмента для использования с MATLAB ®.

Для проверки программирования платы FPGA после добавления файла ее определения подключите пользовательскую плату к компьютеру. Однако подключение платы не требуется для создания файла определения платы.

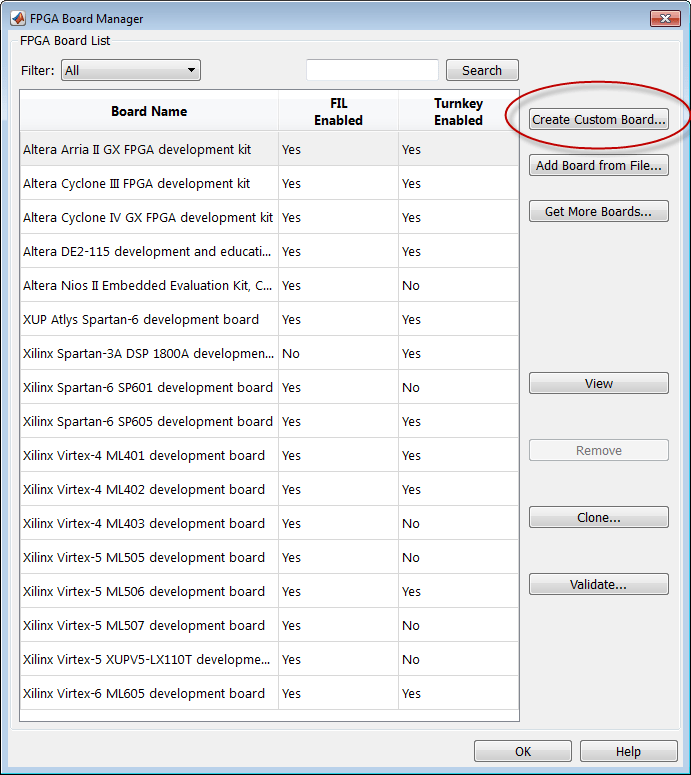

Запустите диспетчер плат FPGA путем ввода следующей команды в подсказке MATLAB:

>>fpgaBoardManager

Нажмите кнопку Create Custom Board (Создать пользовательскую плату), чтобы открыть мастер создания платы FPGA.

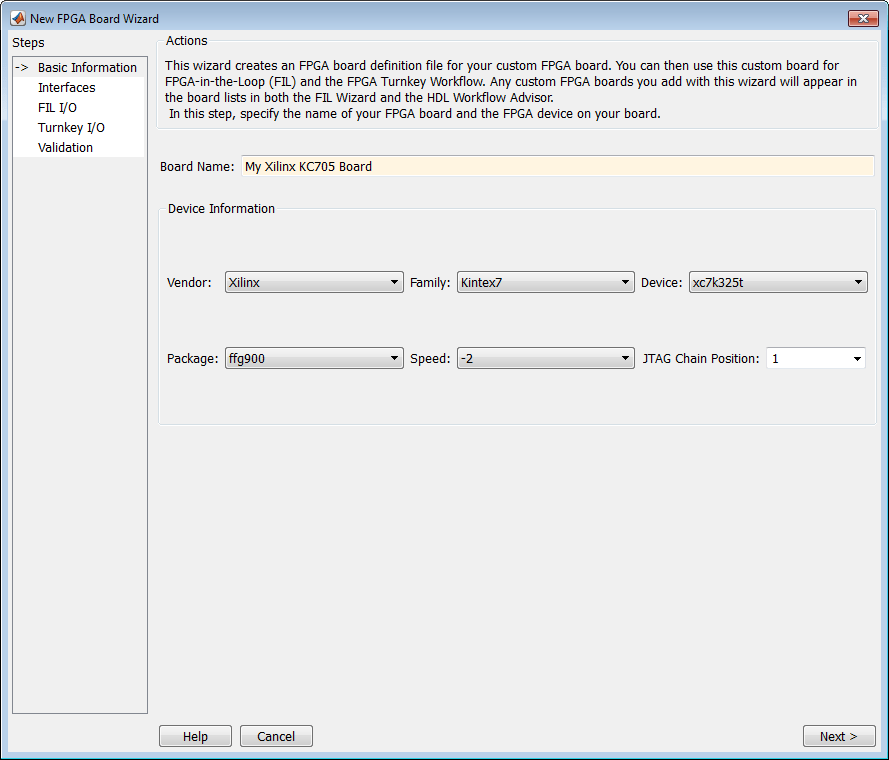

На панели «Основные сведения» введите следующую информацию:

Имя платы: Введите «My Xilinx KC705 Board»

Поставщик: Выбор Xilinx

Семейство: Выбрать Kintex7

Устройство: Выбрать xc7k325t

Пакет: Выбрать ffg900

Скорость: Выбрать -2

Положение цепи JTAG: Выбрать 1

Информация, в которую Вы просто вошли, может быть найдена в Управлении Оценки KC705 по Руководству пользователя Kintex-7 FPGA.

Нажмите кнопку Далее.

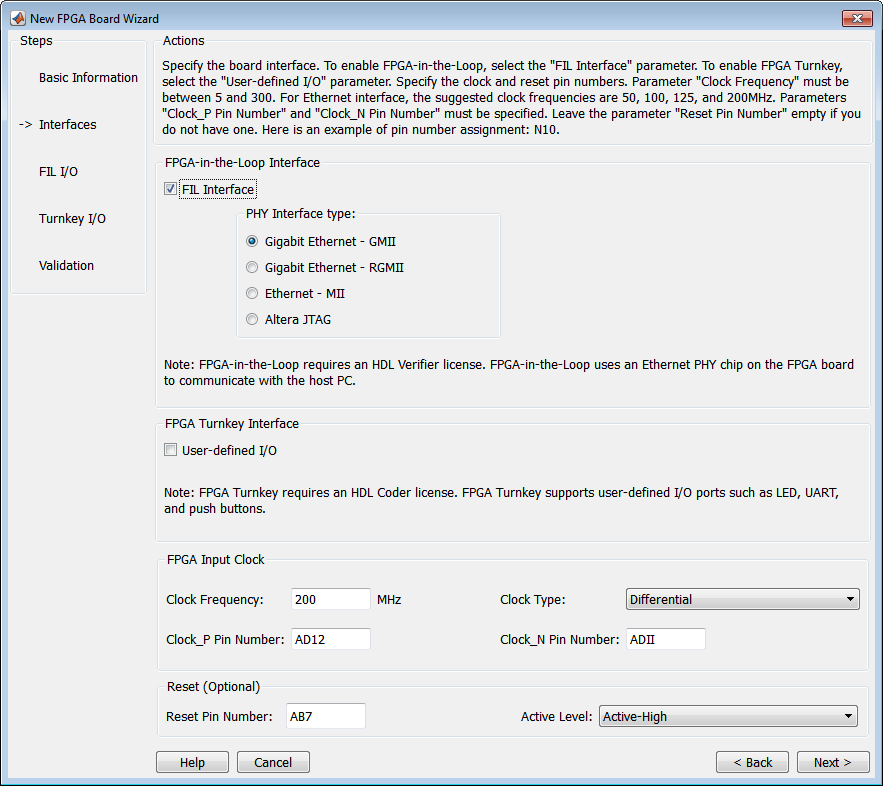

На панели Интерфейсы (Interfaces) выполните следующие задачи.

Выберите FIL Interface. Эта опция необходима для использования платы с FPGA-in-the-loop.

Выберите GMII в поле Тип интерфейса PHY. Эта опция указывает, что встроенный FPGA подключен к микросхеме Ethernet PHY через интерфейс GMII.

Снимите флажок Пользовательский ввод-вывод в разделе Интерфейс FPGA под ключ. Поток операций FPGA «под ключ» не является основным в этом примере.

Тактовая частота: введите 200. Эта плата Xilinx KC705 имеет несколько источников синхросигналов. Тактовая частота 200 МГц является одной из рекомендуемых тактовых частот для использования с интерфейсом Ethernet (50, 100, 125 и 200 МГц).

Тип часов: Выбрать Differential.

Clock_P Номер контакта: Введите AD12.

Clock_N Номер контакта: Введите AD11.

Clock IO Standard (стандарт ввода-вывода часов) - оставьте пустым.

Сбросить номер вывода: Введите AB7. Это значение обеспечивает глобальный сброс FPGA.

Активный уровень: Выбрать Active-High.

Сбросить стандарт ввода-вывода - оставить пустым.

Всю необходимую информацию можно получить из спецификации конструкции платы.

Нажмите кнопку Далее.

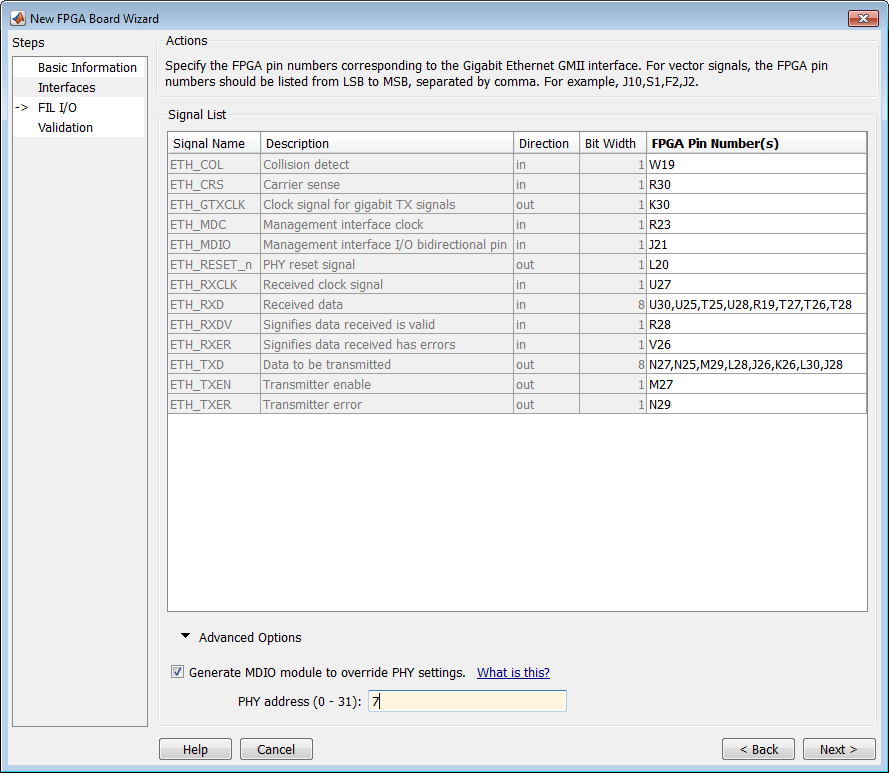

На панели FILI/O введите номера для каждого контакта FPGA. Эта информация является обязательной.

Номера контактов для сигналов RXD и TXD вводятся от наименьшей значащей цифры (LSD) до самой значащей цифры (MSB), разделенной запятой.

| Для имени сигнала... | Введите номер контакта FPGA... |

|---|---|

| ETH_COL | W19 |

| ETH_CRS | R30 |

| ETH_GTXCLK | K30 |

| ETH_MDC | R23 |

| ETH_MDIO | J21 |

| ETH_RESET_n | L20 |

| ETH_RXCLK | U27 |

| ETH_RXD | U30, U25, T25, U28, R19, T27, T26, T28 |

| ETH_RXDV | R28 |

| ETH_RXER | V26 |

| ETH_TXD | N27, N25, M29, L28, J26, K26, L30, J28 |

| ETH_TXEN | M27 |

| ETH_TXER | N29 |

Щелкните Дополнительные параметры, чтобы развернуть раздел.

Установите флажок Generate MDIO module to override PHY settings (Создать модуль MDIO).

Эта опция выбрана по следующим причинам:

На плате Xilinx KC705 имеются перемычки, которые настраивают устройство Ethernet PHY на режим MII, GMII, RGMII или SGMII. Поскольку в этом примере используются интерфейсы GMII, плата FPGA не работает, если устройства PHY установлены в неправильный режим. При выборе опции Generate MDIO module to override PHY settings FPGA использует шину ввода/вывода данных управления (MDIO) для переопределения настроек перемычек и настройки микросхемы PHY в правильном режиме GMII.

В настоящее время эта опция применяется только к PHY-устройству Marvell Alaska 88E1111 и эта KC705 плата использует устройство Marvel.

Физический адрес (0 - 31): Введите 7.

Нажмите кнопку Далее.

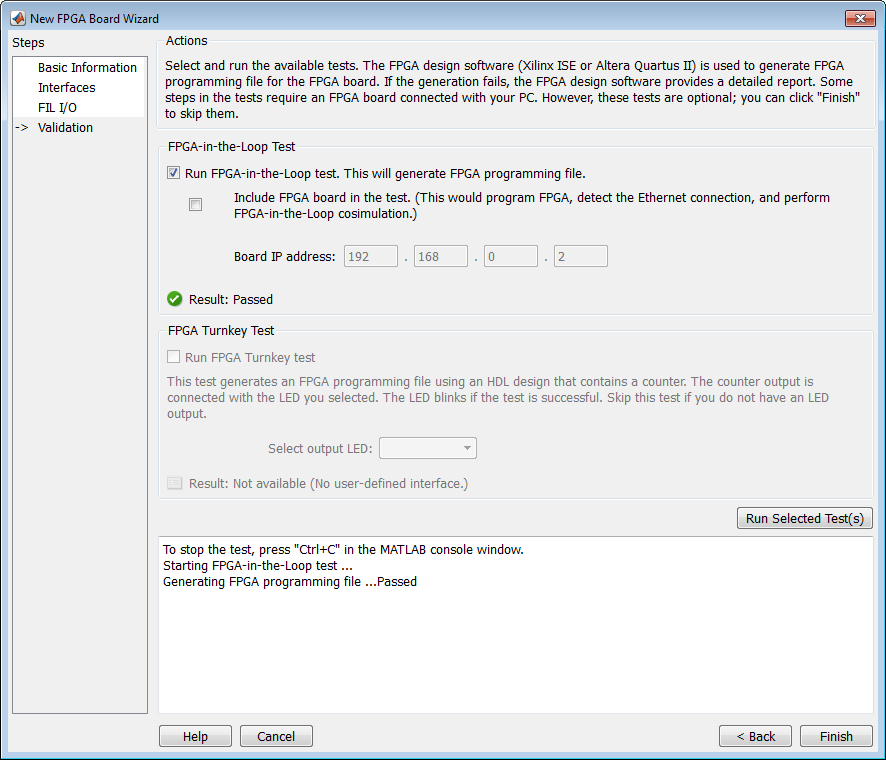

На этом шаге выполняется проверка правильности введенной информации путем выполнения косимуляции FPGA-in-the-loop. На одном компьютере должны быть установлены версии Xilinx ISE 13.4 или выше. Этот шаг является необязательным, и при желании его можно пропустить.

Примечание

Для проверки необходимо использовать Xilinx или Altera. Используйте hdlsetuptoolpath (Кодер HDL) для конфигурирования инструмента для использования с MATLAB.

Чтобы запустить этот тест, выполните следующие действия.

Проверьте опцию Run FPGA-in-the-Loop test.

Если плата подключена, установите флажок Include FPGA в опции test (Включить плату FPGA). Необходимо указать IP-адрес платы FPGA. В этом примере предполагается, что плата Xilinx KC705 подключена к компьютеру и имеет IP-адрес 192.168.0.2.

Щелкните Выполнить выбранные тесты. Для выполнения тестов требуется около 10 минут.

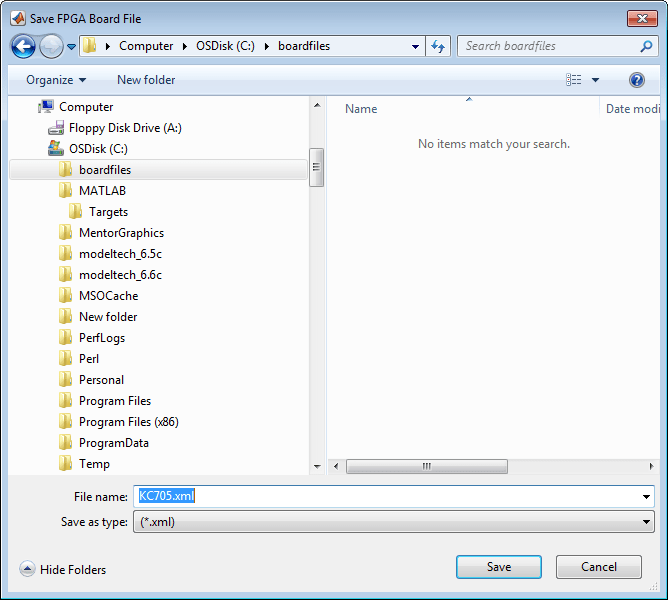

Нажмите Finish для выхода из мастера создания платы FPGA. Появится диалоговое окно Save As (сохранить как) с запросом местоположения файла определения платы FPGA. Для этого примера сохраните как C:\boardfiles\KC705.xml.

Нажмите кнопку Сохранить, чтобы сохранить файл и выйти.

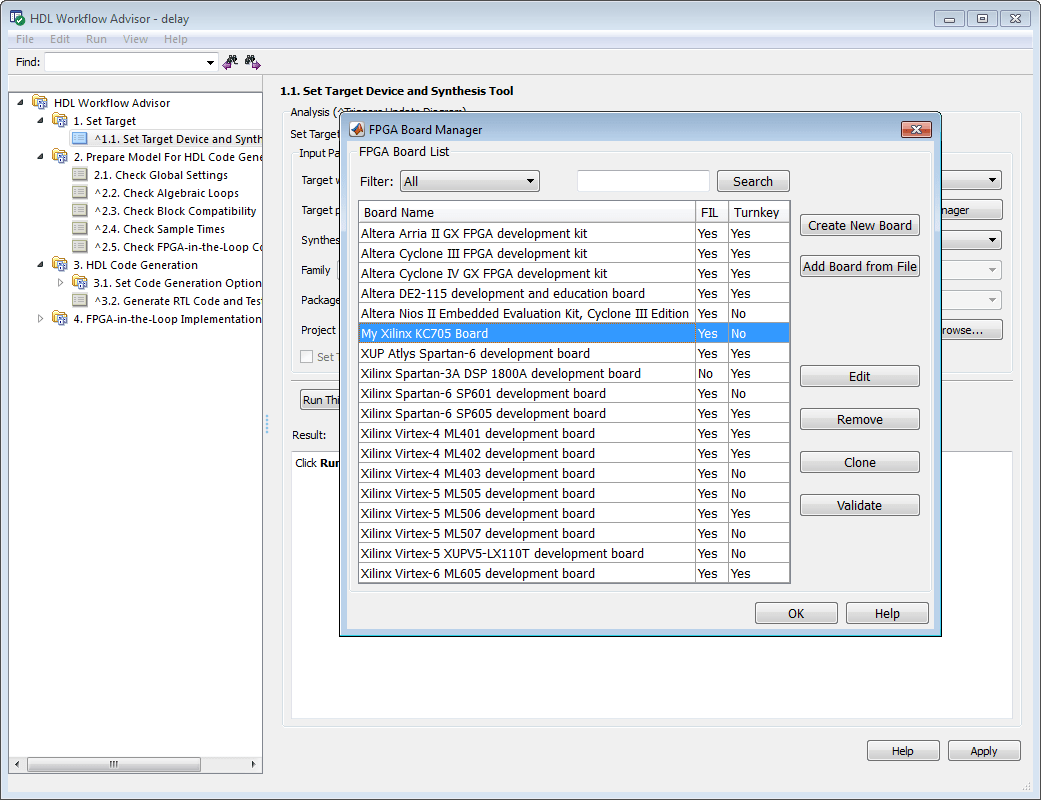

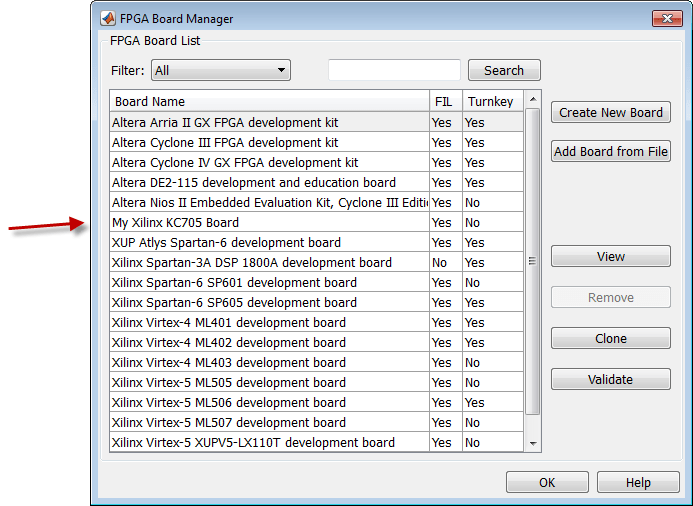

После сохранения файла определения платы выполняется возврат в FPGA Board Manager. Теперь в списке плат FPGA отображается новая определенная плата.

Нажмите OK для закрытия диспетчера плат FPGA.

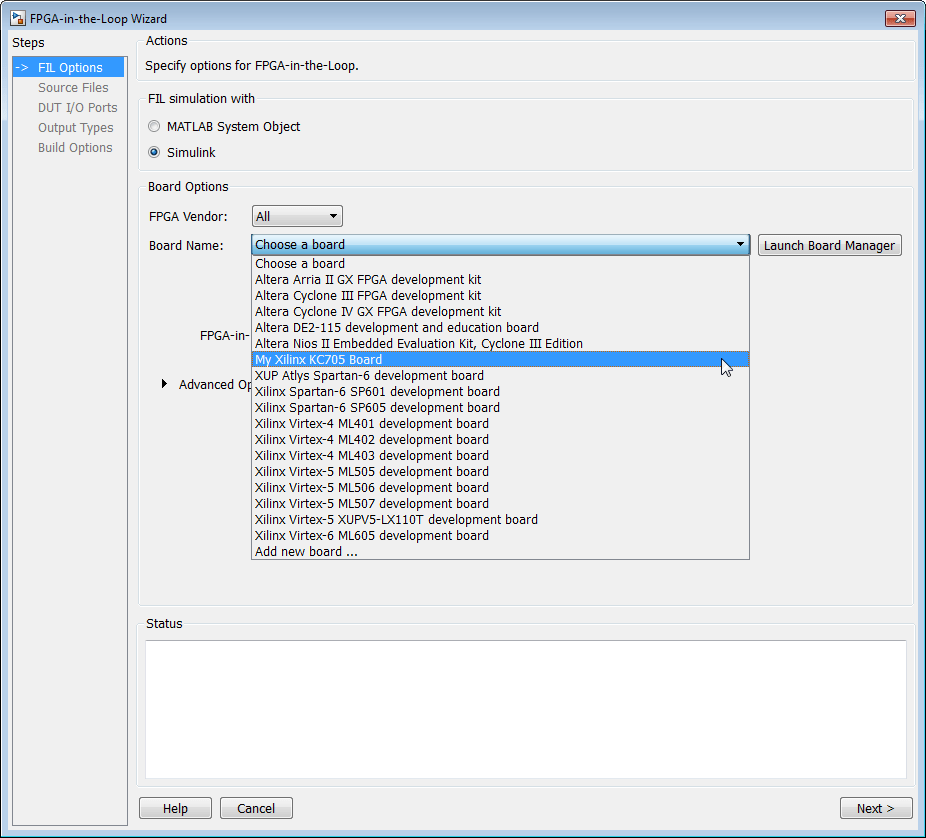

Новую плату можно просмотреть в списке плат с помощью мастера FIL или помощника по рабочим процессам HDL.

Запустите мастер FIL из подсказки MATLAB.

>>filWizard

В списке плат появится плата Xilinx KC705, которую можно выбрать для моделирования FPGA-in-the-loop.

Запуск помощника по рабочим процессам HDL.

На шаге 1.1 выберите FPGA-in-the-Loop и нажмите Launch Board Manager.

В списке плат появится плата Xilinx KC705, которую можно выбрать для моделирования FPGA-in-the-loop.