Блок подтверждения DPI проверяет, равен ли его входной сигнал нулю. Этот блок используется для проверки того, что тестовый стенд Simulink ® ведет себя так, как ожидалось, путем создания логического выражения и подключения его к блоку. Создание SystemVerilog создает немедленное утверждение в созданном модуле. Используйте этот блок для проверки того, что стимул работает так, как ожидалось в средах Simulink и SystemVerilog.

В этом примере показано, как создать модель с блоком утверждения, который выдает предупреждение, когда выходной сигнал блока усиления равен нулю. Затем используйте счетчик для отображения выходных данных модели.

Создание модели Simulink

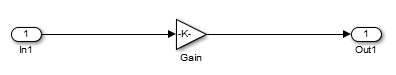

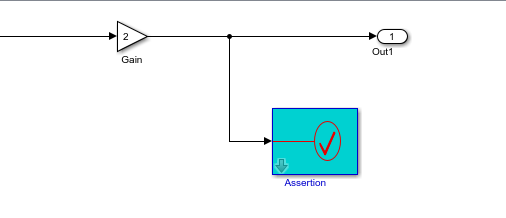

Примерная модель имеет один блок усиления. В этом примере создается предупреждение каждый раз, когда выходной коэффициент усиления равен нулю.

Откройте библиотеку блоков Simulink > Часто используемые блоки.

Добавление блока Inport.

Дважды щелкните этот блок, чтобы открыть его параметры. Установить значение коэффициента усиления в 2.

Добавление блока исходящего порта.

Подключите все блоки, как показано на предыдущей схеме.

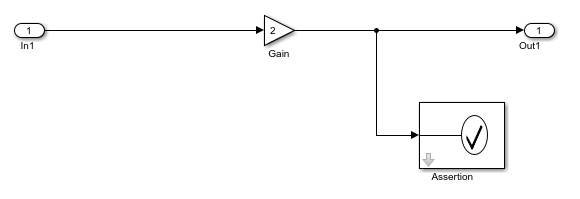

Добавление и настройка блока подтверждения

Найдите блок Assertion в дереве Libraries, выбрав HDL Verifier > For Use with DPI-C SystemVerilog. Добавьте этот блок в модель, а затем подключите выход блока усиления к входу блока подтверждения.

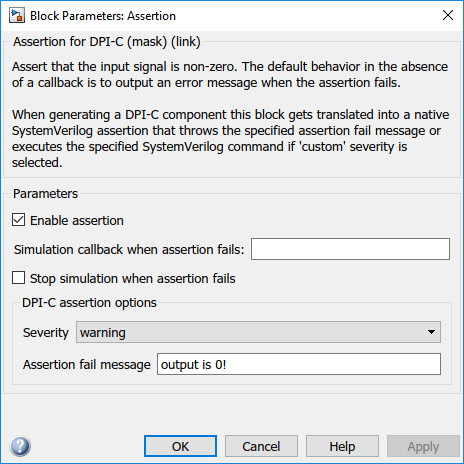

В этом примере используется блок Assertion, чтобы контролировать выходной сигнал Gain и возвращать предупреждение, когда сигнал равен нулю. Дважды щелкните блок Assertion, чтобы настроить его параметры. Установить степень серьезности как warning и сообщение Assertion fail для "output is 0!". Убедитесь, что выбран параметр Включить утверждение.

Примечание

Раздел «Параметры» управляет выполнением Simulink, и они идентичны параметрам в блоке Simulink Assertion (Simulink). Параметры утверждения DPI-C управляют поведением утверждения только в созданном SystemVerilog.

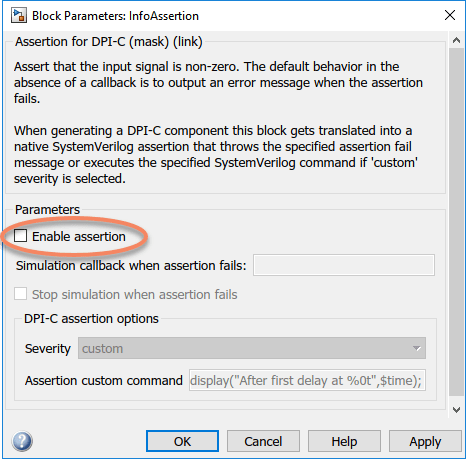

Настройка утверждения

Настройте утверждение, установив для параметра Серьезность значение custom и введите пользовательскую команду SystemVerilog в поле пользовательской команды Assertion. Эта команда может включать системные задачи, такие как $display или $time.

Дополнительно можно настроить поведение утверждения с помощью созданного DPI_getAssertionInfo(obj) Функция SystemVerilog. Эта функция проверяет выполнение утверждений и возвращает всю информацию, записанную для этого утверждения в массиве структуры SystemVerilog. Для каждого утверждения, выполненного в этом такте, функция возвращает Status, Message, и Severity утверждения.

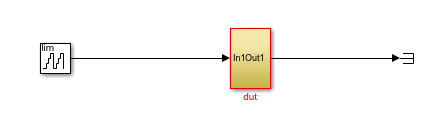

Запустить моделирование в Simulink

Перед моделированием подключите источник стимула и раковину к подсистеме. В этом примере используется счетчик, генерирующий 0-1-2-3 последовательности.

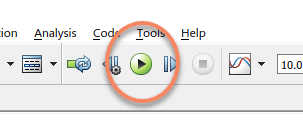

Для построения и выполнения моделирования нажмите кнопку «Выполнить» на панели инструментов.

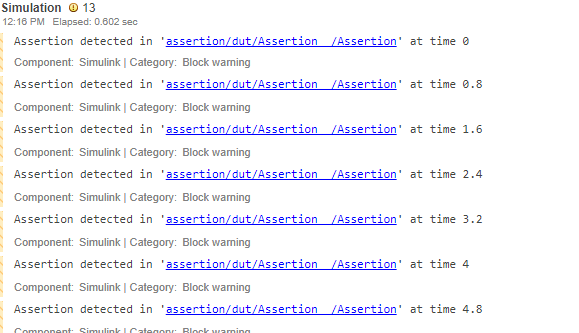

Обратите внимание на предупреждения блока утверждения в выходных данных.

Создать компонент DPI SystemVerilog

На вкладке Приложения Simulink щелкните Верификатор HDL. Затем на вкладке HDL Verifier щелкните C Code Settings. Откроется диалоговое окно Параметры конфигурации (Configuration Parameters) в окне Создание кода (Code Generation).

В системном целевом файле нажмите кнопку Обзор и выберите systemverilog_dpi_grt.tlc.

Если у вас есть лицензия на Embedded Coder ®, вы можете выбрать целевойsystemverilog_dpi_ert.tlc. Этот целевой объект позволяет получить доступ к дополнительным параметрам создания кода (на панели Создание кода (Code Generation) в окне Параметры конфигурации модели (Model Configuration Parameters)).

В группе Создание кода выберите SystemVerilog DPI.

Чтобы включить автоматическое создание тестового стенда, установите флажок Generate test stench.

Нажмите кнопку ОК, чтобы принять эти настройки и закрыть диалоговое окно Параметры конфигурации (Configuration Parameters).

На вкладке Проверка HDL (HDL Verifier) щелкните Создать компонент DPI (Generate DPI Component).

В диалоговом окне «Build code for subsystem» нажмите кнопку «Build».

Компонент SystemVerilog создается как dut_build/dut_dpi.sv в текущей рабочей папке. Кроме того, файл пакета, включающий объявления функций, генерируется как dut_build/dut_dpi_pkg.sv в текущей рабочей папке.

Запуск моделирования SystemVerilog

На вкладке Проверка HDL (HDL Verifier) щелкните Выбрать симулятор (Select Simulator), чтобы открыть окно Параметры конфигурации (Configuration Parameters) на панели SystemVerilog DPI. Затем выберите симулятор из списка имитаторов ЛПВП. Нажмите кнопку ОК.

Чтобы запустить симулятор в режиме GUI, разверните кнопку Run Testbench и выберите Launch Simulator в режиме GUI.

Для ModelSim ® или Questa ® введите следующую команду для запуска моделирования.

do run_tb_mq.do

Обратите внимание на предупреждения моделирования, отображаемые утверждением:

run -all # ** Warning: assertion:14:output is 0! # Time: 40 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 80 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 120 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 160 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 200 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 240 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 280 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 320 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 360 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 400 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 440 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 480 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 520 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # **************TEST COMPLETED (PASSED)************** # ** Note: $finish : ./dut_dpi_tb.sv(62) # Time: 542 ns Iteration: 0 Instance: /dut_dpi_tb # End time: 14:16:43 on Dec 29,2017, Elapsed time: 0:00:04 # Errors: 0, Warnings: 13

После выполнения моделирования SystemVerilog с сгенерированным утверждением в файле журнала отображаются предупреждения и ошибки. Чтобы определить, какой блок утверждения вызвал определенное предупреждение или вывод ошибки, используйте hilite_system (Simulink) функция.

Каждое предупреждение отображает номер, идентифицирующий конкретный блок утверждения, который создал это предупреждение. Это число является идентификатором Simulink (SID) этого блока. Например, ниже показано предупреждение, генерируемое блоком утверждения с номером SID 14.

# ** Warning: assertion:14:output is 0!

Чтобы выделить блок, сгенерировавший это предупреждение, выполните следующий код в окне команд MATLAB ®.

hilite_system('assertion:14')

Дополнительные сведения об идентификаторах Simulink см. в разделе Идентификаторы Simulink (Simulink).

Можно отключить выполнение любого блока утверждения в среде Simulink или в среде SystemVerilog. Отключите утверждение в Simulink, если требуется, чтобы утверждение игнорировалось как в Simulink, так и в SystemVerilog. Отключите утверждение в SystemVerilog, если не требуется регенерировать код из Simulink, но требуется возможность отключить утверждения во время моделирования SystemVerilog.

Отключение утверждений в Simulink. Чтобы отключить проверку входного сигнала блока утверждения DPI-C или выдачу предупреждений или ошибок, снимите флажок Включить утверждение в параметрах блока утверждения.

При снятии этого флажка утверждение отключается от выдачи предупреждений или ошибок и создания утверждения SystemVerilog.

Отключение утверждений в SystemVerilog. В среде SystemVerilog можно отключить утверждение, предоставив Simulink Identifier в качестве аргумента командной строки в симулятор HDL. Например, при использовании ModelSim и предположении, что SID равен 14, можно отключить вывод любых предупреждений, сообщений об ошибках или пользовательских команд, создаваемых блоком Assertion со следующим аргументом plus:

vsim -c -voptargs=+acc -sv_lib ../dut_win64 work.dut_dpi_tb +assertion:14