HDL Verifier™ предоставляет два типа тестовых стендов, которые генерируют компонент языка C и интегрируют его в тестовый стенд SystemVerilog с прямым интерфейсом программирования (DPI). Один стенд проверяет сформированный компонент C на соответствие сохраненным векторам данных из подсистемы Simulink ®. Другой стенд проверяет сгенерированный код HDL на соответствие компоненту C, сгенерированному из всей модели Simulink.

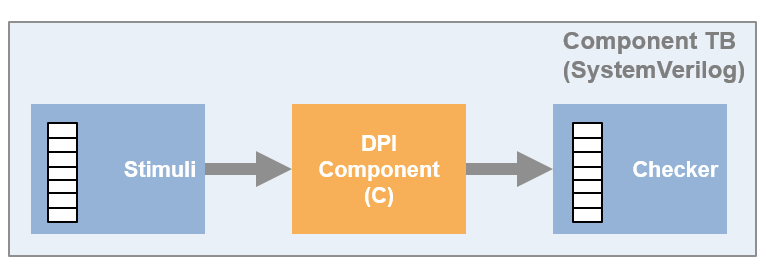

Стенд тестирования компонентов - при генерации компонента C из подсистемы Simulink для использования в качестве компонента DPI можно дополнительно создать стенд тестирования SystemVerilog. Тестовый стенд проверяет сгенерированный компонент DPI по векторам данных из модели Simulink. Эта функция доступна в диалоговом окне Параметры конфигурации модели (Model Configuration Parameters) в разделе Создание кода (Code Generation). См. раздел Создание компонента SystemVerilog DPI.

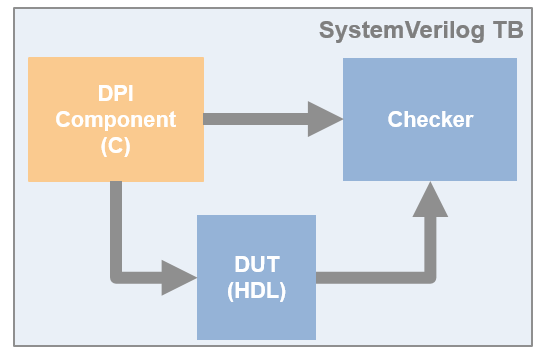

Стенд тестирования кода HDL - при генерации кода HDL из подсистемы с помощью Coder™ HDL можно дополнительно создать стенд тестирования SystemVerilog. Этот стенд сравнивает выходные данные реализации ЛПВП с результатами модели Simulink. Доступ к этой функции можно получить в мастере рабочего процесса HDL по пути Создание кода HDL (HDL Code Generation) > Задать параметры тестирования (Set Testbench Options) или в диалоговом окне Параметры конфигурации модели (Model Configuration Parameters) по пути Создание кода HDL (HDL Code Generation) > Испытательный стенд (Test Stench). Либо для доступа в командной строке установите значение GenerateSVDPITestBench имущество makehdltb (Кодер ЛПВП). См. раздел Проверка конструкции ЛПВП с помощью испытательного стенда с DPI SystemVerilog (кодер ЛПВП).

Для обоих типов испытательных стендов требуется лицензия Simulink Coder™.

Ограничения

HDL Verifier преобразует матрицы и векторы в одномерные массивы в SystemVerilog. Например, матрица 4 на 2 в Simulink преобразуется в одномерный массив из восьми элементов в SystemVerilog.

Эти подсистемы не поддерживают формирование тестового стенда DPI:

Срабатывающая подсистема

Включенная подсистема

Подсистема с портом действия

Генератор компонентов SystemVerilog DPI также создает испытательный стенд. Этот стенд можно использовать для проверки того, что созданный компонент SystemVerilog функционально эквивалентен исходной подсистеме Simulink. Стенд сохраняет векторы данных из моделирования Simulink для применения в качестве стимулов и для проверки по выходному сигналу компонента. Этот испытательный стенд не предназначен для замены системного испытательного стенда для собственного применения. Однако созданный стенд тестирования можно использовать в качестве начального примера для собственного стенда системного тестирования.

При включении регистрации контрольных точек в модели созданный стенд также сравнивает их значения сигналов в компоненте SystemVerilog с записанными значениями из Simulink.

Примечание

HDL Verifier не поддерживает создание тестового стенда для пользовательского сгенерированного кода SystemVerilog. См. раздел Адаптация.

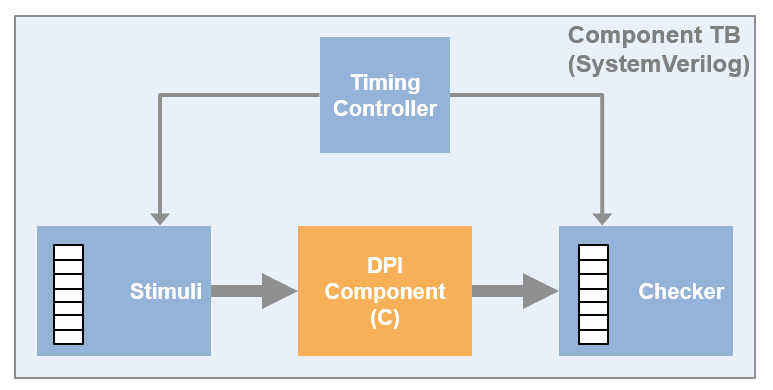

Если подсистема содержит сигналы с более чем одной частотой дискретизации, созданный стенд включает в себя модуль контроллера синхронизации. Контроллер синхронизации генерирует входные тактовые сигналы на соответствующих скоростях. Входные стимулы и ожидаемые выходные данные применяются и проверяются в соответствии с их частотой выборки.

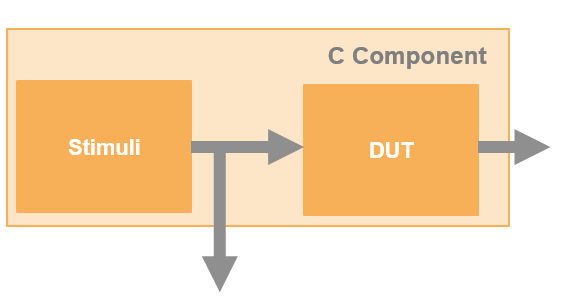

При создании кода HDL из подсистемы с помощью кодера HDL можно также создать тестовый стенд SystemVerilog DPI. Этот стенд сравнивает выходные данные реализации ЛПВП с результатами модели Simulink. В дополнение к коду C для подсистемы DUT кодер также генерирует код C для части модели, которая генерирует входные стимулы. Создание этого тестового стенда выполняется быстрее, чем тестовое стенд HDL по умолчанию для больших наборов данных. Это преимущество связано с тем, что кодер не запускает модель Simulink для получения векторов входных и выходных данных. Сгенерированный компонент C вычисляет входные стимулы и выходные результаты для сравнения с реализацией HDL.

Созданный тестовый стенд SystemVerilog включает в себя:

Сгенерированный код Verilog ® или VHDL ® для вашей подсистемы

Сгенерированный компонент C

Код для сравнения выходных данных кода HDL с выходными данными компонента C.

Запустите этот стенд для проверки того, что сгенерированный код HDL реализует тот же алгоритм, что и модель Simulink.