Перед моделированием модели используйте обнаружение неработающей логики для анализа модели на неработоспособность. В Simulink ® Design Verifier™ обнаружение ошибок конструкции для неработающей логики состоит из двух вариантов анализа:

Мертвая логика (частичная): при выборе этой опции Simulink Design Verifier анализирует модель без каких-либо аппроксимаций, таких как рациональное приближение для плавающих точек или при аппроксимации цикла. Дополнительные сведения см. в разделе Аппроксимации. При использовании этой опции Simulink Design Verifier не сообщает об активной логике или неопределившихся целях и может не идентифицировать некоторую неработоспособную логику в модели.

Эта опция доступна в:

Консультант по модели. См. раздел Проверка на наличие ошибок конструкции с помощью Model Advisor.

Диалоговое окно «Параметры конфигурации» на панели Design Verifier > Design Error Detection.

Выполните исчерпывающий анализ: С помощью этой опции Simulink Design Verifier сообщает активную логику в дополнение к неработающей логике, а также неопределившимся целям. Эта опция может в некоторых случаях идентифицировать или найти дополнительную мертвую логику. Анализ может использовать аппроксимации и сообщается соответствующим образом.

Эта опция доступна в диалоговом окне Параметры конфигурации (Configuration Parameters) на панели Проверка конструкции (Design Verifier) > Обнаружение ошибок конструкции (Design Error Detection).

Если мастер модели не используется, для обнаружения неработающей логики выполните следующие действия.

На вкладке Design Verifier в разделе Mode выберите Design Error Detection.

Щелкните Параметры обнаружения ошибок.

В диалоговом окне «Параметры конфигурации» на панели «Design Verifier > Design Error Detection» выполните следующие действия.

Включите опцию Dead logic (частичная).

Снимите флажок Выполнить исчерпывающий анализ, если он выбран.

Чтобы применить эти настройки, нажмите кнопку ОК и закройте диалоговое окно Параметры конфигурации (Configuration Parameters).

Щелкните Обнаружить ошибки конструкции (Detect Design Errors).

На вкладке Design Verifier в разделе Mode выберите Design Error Detection.

Щелкните Параметры обнаружения ошибок.

В диалоговом окне «Параметры конфигурации» на панели Design Verifier > Design Error Detection включите опции Dead logic (частичный) и Run исчерпывающий анализ.

Чтобы применить эти настройки, нажмите кнопку ОК и закройте диалоговое окно Параметры конфигурации (Configuration Parameters).

Щелкните Обнаружить ошибки конструкции (Detect Design Errors).

В этом примере показано, как обнаружить мертвую логику в sldvSlicerdemo_dead_logic пример модели. При обнаружении неактивной логики в модели обнаруживаются недостижимые цели, которые приводят к тому, что элемент модели остается неактивным.

Откройте окно sldvSlicerdemo_dead_logic модель.

open_system('sldvSlicerdemo_dead_logic');На вкладке Design Verifier в разделе Mode выберите Design Error Detection.

Щелкните Параметры обнаружения ошибок.

В диалоговом окне «Параметры конфигурации» на панели Design Verifier > Design Error Detection включите параметр Dead logic (частичный) и снимите флажок Run исчерпывающий анализ.

Щелкните Обнаружить ошибки конструкции (Detect Design Errors).

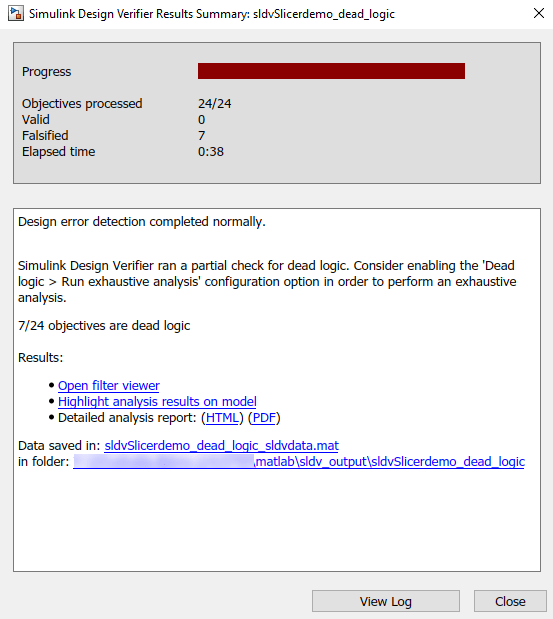

Программа анализирует модель на наличие неработающей логики и отображает результаты в окне Сводка результатов (Results Summary). Результат показывает, что семь из 24 цели были признаны мертвой логикой.

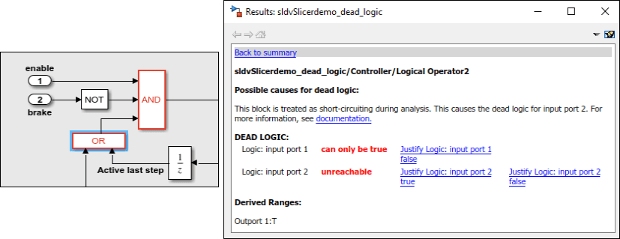

Щелкните Подсветить результаты анализа на модели (Highlight analysis results on model). Элементы модели неработоспособной логики выделены красным цветом.

Откройте окно Controller

и щелкните на блоке ИЛИ, выделенном красным цветом. Инспектор результатов отображает сводку неработающей логики.

set вход равен 1, так что input port 1 блока OR может быть только true. Статус подразумевает, что input port 1 ложное состояние - неработоспособная логика. Аналогично, input port 2 является unreachable, поскольку цель никогда не выполняется и является мертвой логикой.

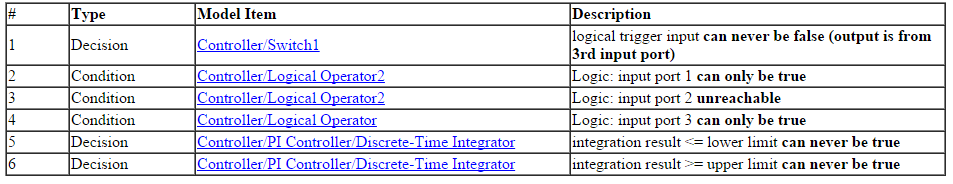

Чтобы просмотреть подробный отчет об анализе, в окне Сводка результатов (Results Summary) щелкните HTML.

В отчете отображается сводка всех результатов, являющихся неработоспособными в модели.

Неработающая логика

Программное обеспечение хранит подробные результаты анализа в DeadLogic field в файлах данных Simulink Design Verifier. Для дальнейшего анализа результатов можно использовать файл данных.