SoC Blockset™ позволяет проводить постсимуляционный анализ диагностических данных памяти. Эти графики обеспечивают высокоуровневую диагностику производительности системы памяти модели. Эти графики являются расчетными измерениями на основе моделирования модели. Он учитывает тип данных, время выборки и тактовую частоту для расчета пропускной способности модели памяти и количество пакетов, выполняемых на порт памяти.

Для включения регистрации сигнала при моделировании выберите Hardware Implementation в диалоговом окне Configuration Parameters. В разделе Hardware Board Settings > Target Hardware Resources > FPGA design (debug) выберите требуемый уровень диагностики канала памяти.

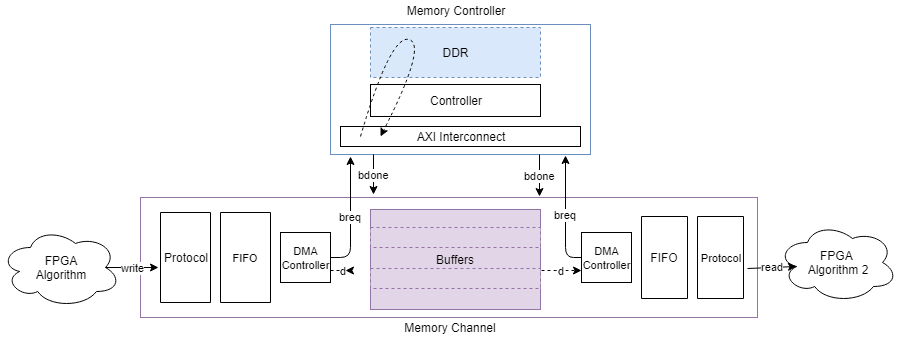

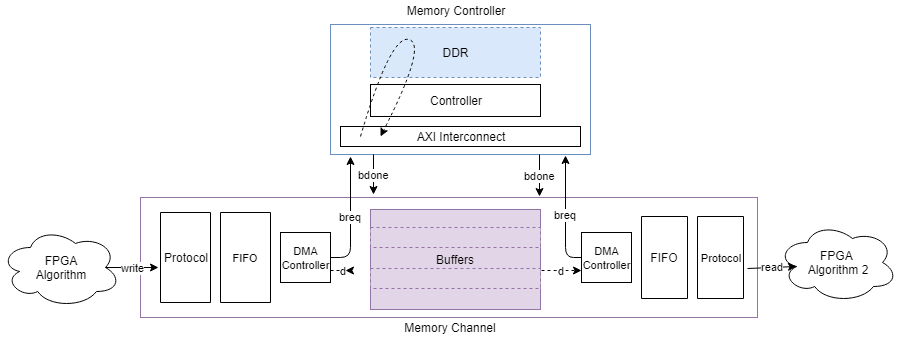

На этом рисунке показан путь передачи данных от одного алгоритма FPGA к другому алгоритму FPGA через канал памяти.

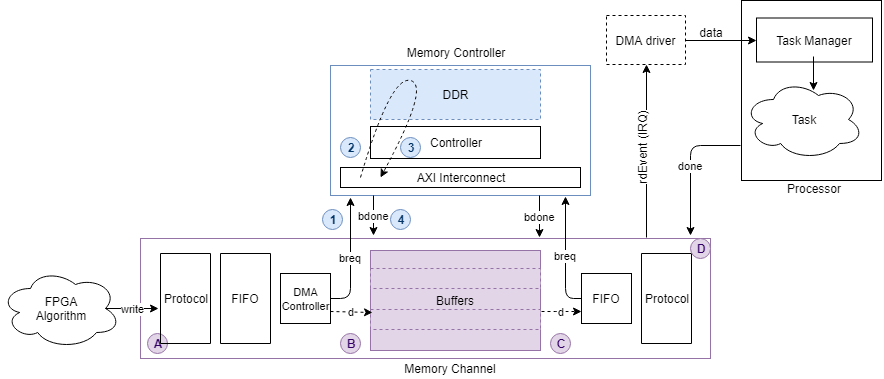

С помощью маски блока «Канал памяти» можно просматривать графики задержки канала для канала передачи данных (представленные A, B, C и D в изображении). С помощью маски блока контроллера памяти можно просматривать данные о пропускной способности памяти, количестве пакетов и задержке управления (представленные 1, 2, 3 и 4 в изображении).

Путь передачи данных от алгоритма FPGA к процессору обслуживается через драйвер DMA и процессор задач и иллюстрируется на этом изображении.

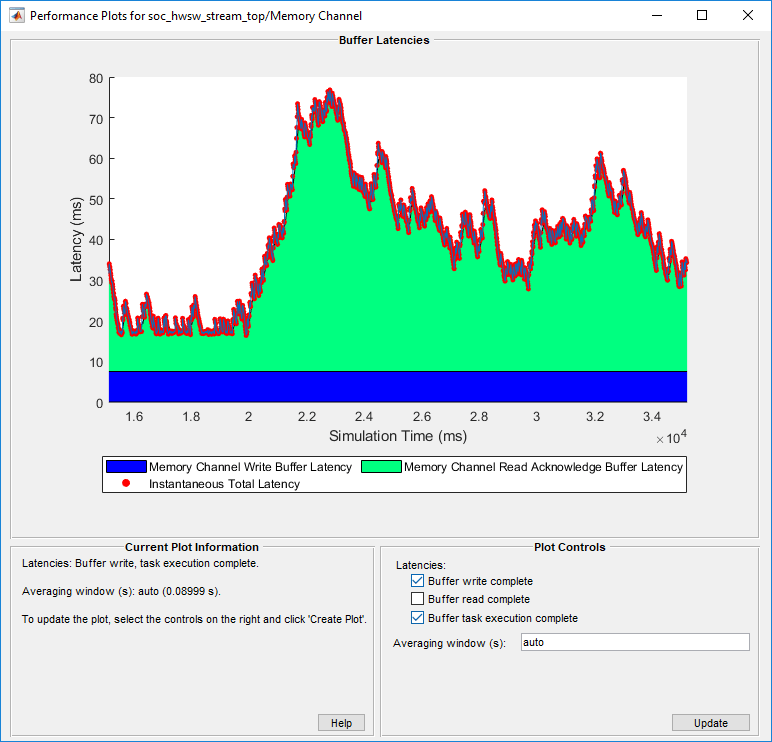

Информация о задержке канала памяти доступна после моделирования для каждого канала. После моделирования модели откройте блоковую маску канала памяти. На вкладке Производительность (Performance) щелкните Запуск графиков производительности (Launch performance plots). Это действие открывает новое окно с несколькими параметрами управления для отображения этих различных задержек:

Buffer write complete - этот параметр показывает время между выдачей запроса на запись до момента полной записи буфера. Это путь между A и B на рисунке.

Buffer read complete (чтение буфера завершено) - этот параметр показывает время между выдачей запроса на чтение до момента чтения буфера, которое снова доступно для записи. Это путь между C и D на рисунке. Эта опция доступна только в том случае, если считыватель является алгоритмом FPGA (а не алгоритмом процессора). Если считыватель является алгоритмом процессора, это время отображается как ноль.

Выполнение задачи буфера завершено - этот параметр показывает время, необходимое между выдачей запроса на чтение и моментом, когда буфер считывается и снова доступен для записи. Это путь между C и D на рисунке. Эта опция доступна только в том случае, если считыватель является алгоритмом процессора (а не алгоритмом FPGA). Если считыватель является алгоритмом FPGA, это время отображается как ноль.

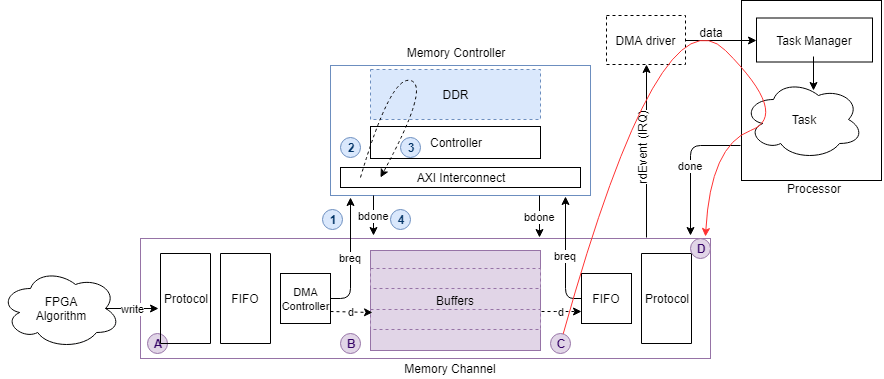

Выполнение задачи Buffer завершено показывает время, необходимое для возникновения следующих событий:

Буфер записи заполнен.

Канал выдал запрос прерывания (IRQ) процессору.

Выполняется подпрограмма обслуживания прерываний (ISR).

Задача запланирована.

Задача запущена.

Задача считывает данные.

При необходимости задача обработала данные.

Задача отправляет done сигнал обратно в канал.

На следующем рисунке показан путь задержки для выполнения задачи в виде красной стрелки от C до D.

Окно (и) усреднения - укажите время (в секундах) для ширины окна усреднения. График строится как скользящее среднее с использованием временного окна с заданной шириной. Можно также указать min, max, или auto.

min - используйте это значение для просмотра данных без усреднения. График суммарной задержки выравнивается с метками Мгновенная суммарная задержка (Instantaneous Total Latency).

max - используйте это значение для просмотра общего среднего значения для всего моделирования.

auto - Используйте это значение для просмотра усреднения по количеству буферов в канале.

Мгновенная суммарная задержка - показывает дискретные измерения суммарной задержки на буфер.

Если добавить команду Буфер завершения записи в команду Буфер завершения чтения или выполнение задачи Буфер завершения, график отобразит полную задержку от устройства записи к устройству чтения. На этом рисунке показан график общей задержки для примера потоковой передачи данных с оборудования на программное обеспечение.

Следует отметить, что задержки отображаются через окно усреднения, равное одной секунде. Мгновенная общая задержка показывает пик задержки как 76,8267 ms. Используйте эту информацию для проверки модели в соответствии с требованиями.

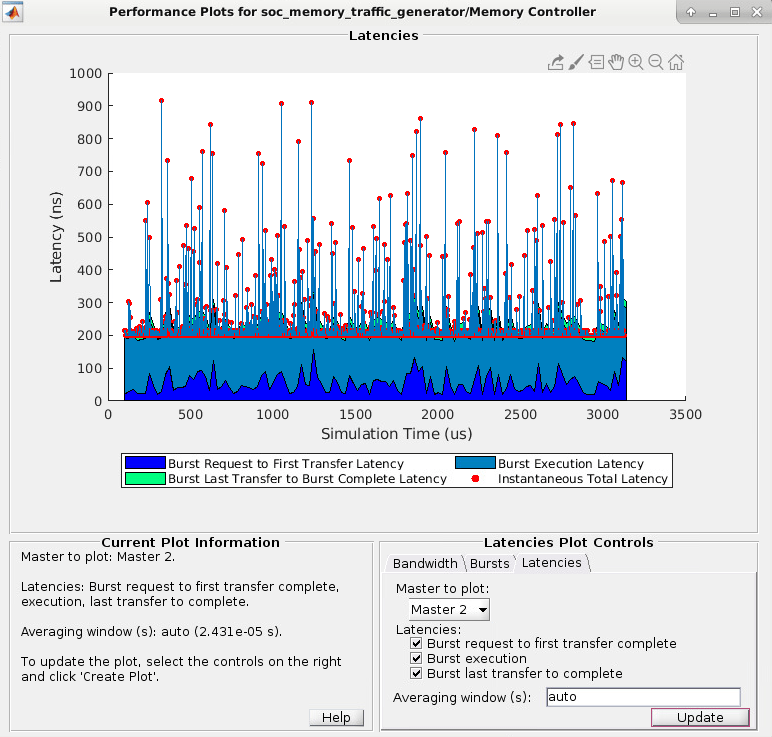

Информация о задержке контроллера памяти доступна после моделирования. После моделирования модели откройте маску блока контроллера памяти. На вкладке Производительность (Performance) щелкните Запуск графиков производительности (Launch performance plots). Это действие открывает новое окно с несколькими параметрами управления для отображения метрик производительности.

На этом рисунке показан путь передачи данных от одного алгоритма FPGA к другому алгоритму FPGA через канал памяти.

На вкладке Задержки выберите шаблон, для которого требуется построить график задержек. Выберите один из следующих вариантов:

Burst request to first transfer complete - этот параметр показывает время, которое требуется с момента выдачи блоком канала памяти запроса burst-write на первую передачу данных. Эта задержка приводит к задержкам арбитража или межсоединений. Это путь между 1 и 2 на рисунке.

Задержка выполнения пакета - этот параметр показывает время, которое требуется от первой передачи данных до момента записи пакета в память. Это путь между 2 и 3 на рисунке.

Last transfer to complete latency - этот параметр показывает время, необходимое с момента завершения пакета до момента выдачи блоком контроллера памяти burst-done сигнал в блок канала памяти. Это путь между 3 и 4 на рисунке.

Окно (и) усреднения - укажите время (в секундах) для ширины окна усреднения. График строится как скользящее среднее с использованием временного окна с заданной шириной. Можно также указать min, max, или auto.

min - используйте это значение для просмотра данных без усреднения. График суммарной задержки выравнивается с метками Мгновенная суммарная задержка (Instantaneous Total Latency).

max - используйте это значение для просмотра общего среднего значения для всего моделирования.

auto - Используйте это значение для просмотра усреднения более 1% пакетов во время моделирования.

Мгновенная суммарная задержка - этот параметр показывает дискретные измерения суммарной задержки на пакет.

Щелкните Создать график (Create Plot), чтобы увидеть задержку для выбранных основных объектов в течение времени моделирования. На этом рисунке показана общая задержка для Master 2 в примере Анализ пропускной способности памяти с использованием генераторов трафика.

Примечание

Графики задержек контроллера памяти недоступны, когда ведущим является процессор.

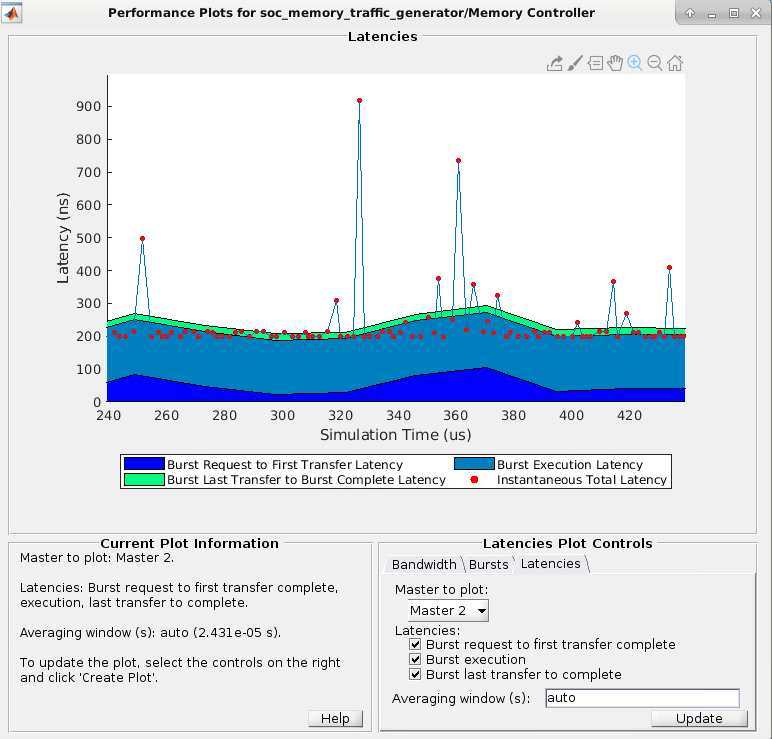

Затем можно увеличить масштаб изображения для анализа максимальной мгновенной задержки:

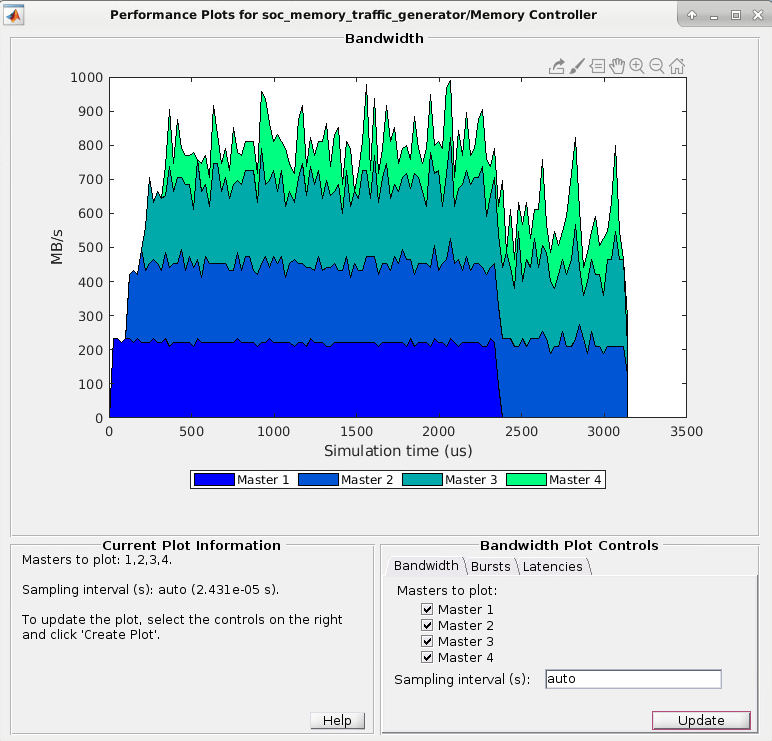

На вкладке Пропускная способность выберите основные параметры, для которых требуется построить график пропускной способности. Щелкните Создать график (Create Plot), чтобы увидеть полосу пропускания в мегабайтах в секунду для выбранных основных объектов в течение времени моделирования. На этом рисунке показана полоса пропускания для примера «Анализ полосы пропускания памяти с использованием генераторов трафика».

Примечание

Информация о пропускной способности не отображается, если основной процессор является процессором.

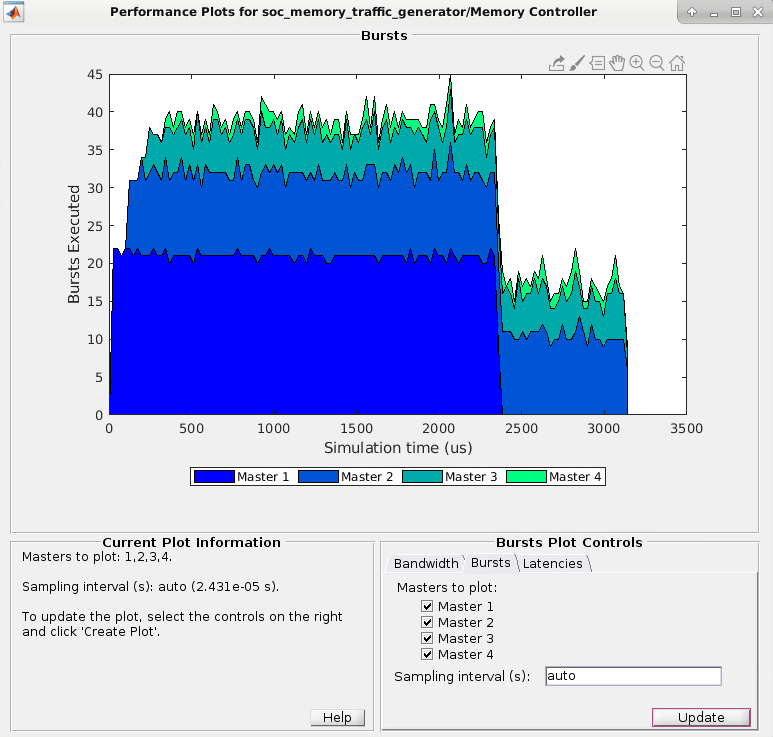

На вкладке Пакеты выберите шаблоны, для которых требуется построить график пакетов. Щелкните Создать график (Create Plot), чтобы просмотреть количество пакетов, выполненных для выбранного шаблона за время моделирования. На этом рисунке показано число пакетов для примера «Анализ пропускной способности памяти с использованием генераторов трафика».

Примечание

Информация о пропускной способности не отображается, если основной процессор является процессором.

Канал памяти | Контроллер памяти