Арбитражное разбирательство транзакций памяти для одного или нескольких блоков канала памяти

Блоксеть/память SoC

Блок контроллера памяти выполняет арбитраж между хозяевами и предоставляет им уникальный доступ к общей памяти. Настройте этот блок для поддержки нескольких каналов с различными протоколами арбитража. Блок контроллера памяти также предназначен для регистрации и отображения данных о производительности, что позволяет отладить и понять производительность системы во время моделирования.

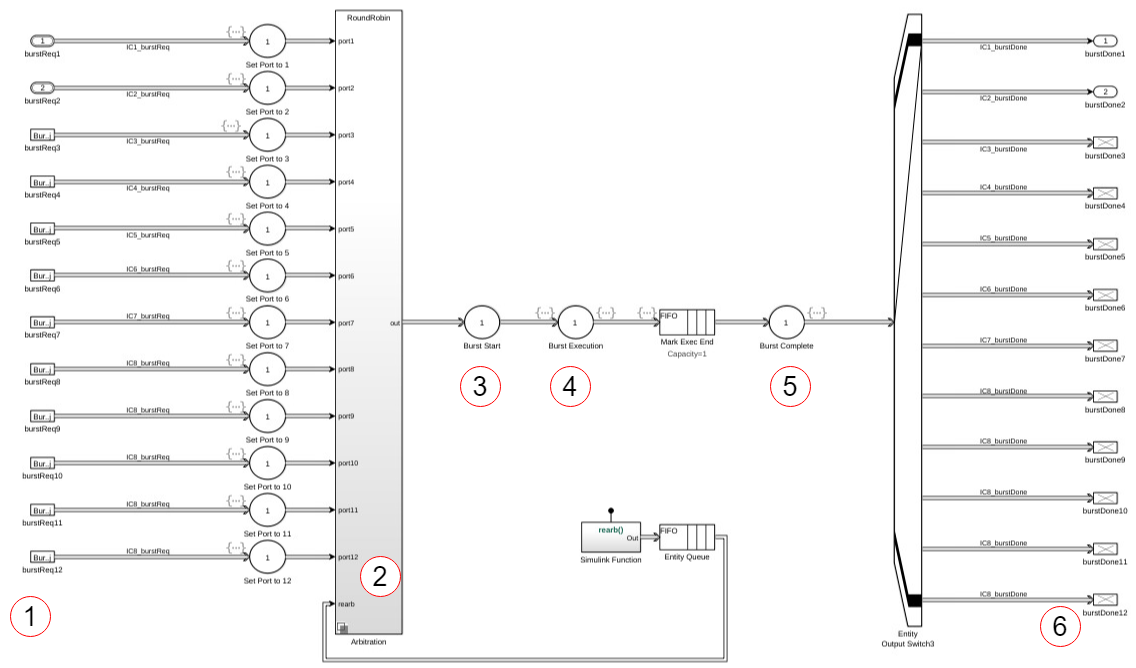

На следующем рисунке показана реализация блока контроллера памяти.

Числа в изображении представляют различные стадии задержки блока.

Запрос пакета поступает в блок.

Запрос может быть отложен арбитражем до тех пор, пока ему не будет предоставлен доступ к шине.

Если для модели требуется дополнительная задержка перед началом первого переноса, установите это значение в поле Запрос для первого переноса (в часах).

Задержка выполнения пакета вычисляется по размеру пакета, ширине данных, тактовой частоте и значению снижения полосы пропускания (%).

Если в модели требуется задержка от завершения пакета до выдачи ответа пакета каналу, установите это значение в поле Last transfer to transaction complete (в часах).

Контроллер памяти имеет внутреннее состояние, которое отображается при использовании Logic Analyzer для просмотра метрик моделирования и выполнения. Значения состояния:

BurstRequest: Запрос пакета поступает в блок.

BurstExecuting: Выполняется пакет.

BurstDone: Выполняется пакет.

BurstComplete: Пакет завершен, и сигнал burstDone посылается ведущему устройству.

Сведения о визуализации задержек контроллера памяти см. в разделе Графики задержек контроллера памяти.

Если арбитраж Interconnect установлен в Round Robinмодель не поддерживает пошаговое моделирование. Дополнительные сведения о степпинге моделирования см. в разделе Степпер моделирования.

Канал памяти | Генератор трафика памяти | Зарегистрировать канал