Подобно графикам производительности памяти, сгенерированным при моделировании, можно собирать информацию о трафике межсоединений памяти из проекта, запущенного в FPGA. Затем можно создать аналогичные графики производительности. Можно также записать информацию о транзакциях памяти для просмотра в инструменте Logic Analyzer аналогично транзакциям пакета от контроллера памяти при моделировании. Эти графики используются для мониторинга реальной производительности памяти, отладки и улучшения конструкции и сравнения их с производительностью памяти, полученной при моделировании.

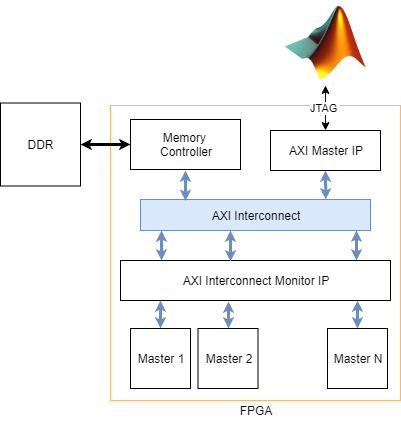

Чтобы включить IP-адрес AXI interconnect monitor (AIM) в проект, в параметрах конфигурации модели выберите параметр Include AXI interconnect monitor в разделе Hardware Implementation > Target hardware resources > FPGA design (debug). Во время работы на FPGA монитор межсоединений AXI собирает информацию из проекта. Эту информацию можно запросить в MATLAB ® с помощью соединения JTAG. Все хозяева памяти в FPGA подключены к IP-адресу монитора межсоединений AXI. Эти шаблоны могут включать блоки «Канал памяти» и «Генератор трафика памяти», для которых был создан код HDL, или любые другие шаблоны в вашей конструкции.

Инструмент SoC Builder создает скрипт тестового стенда JTAG для проекта. Сценарий собирает метрики производительности с монитора межсоединений AXI и запускает приложение графика производительности, которое строит графики производительности памяти для полосы пропускания, количества пакетов и задержек транзакций. Эти графики похожи на графики производительности памяти при моделировании. Можно также изменить сценарий для сбора и отображения сигналов транзакций памяти, аналогичных пакетным сигналам контроллера памяти при моделировании. Сведения о производительности памяти моделирования см. в разделе Графики производительности моделирования и буферные и пакетные формы сигналов.

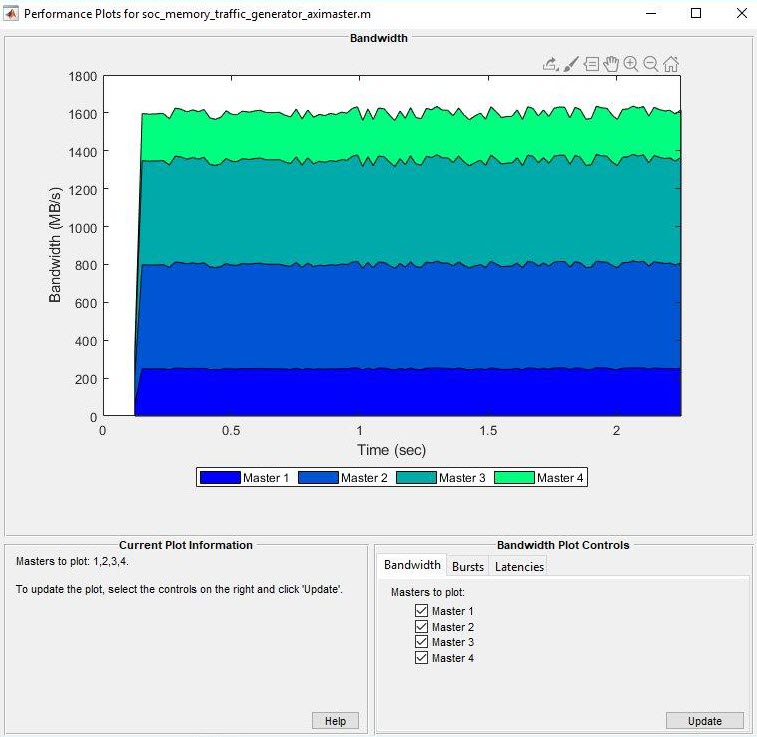

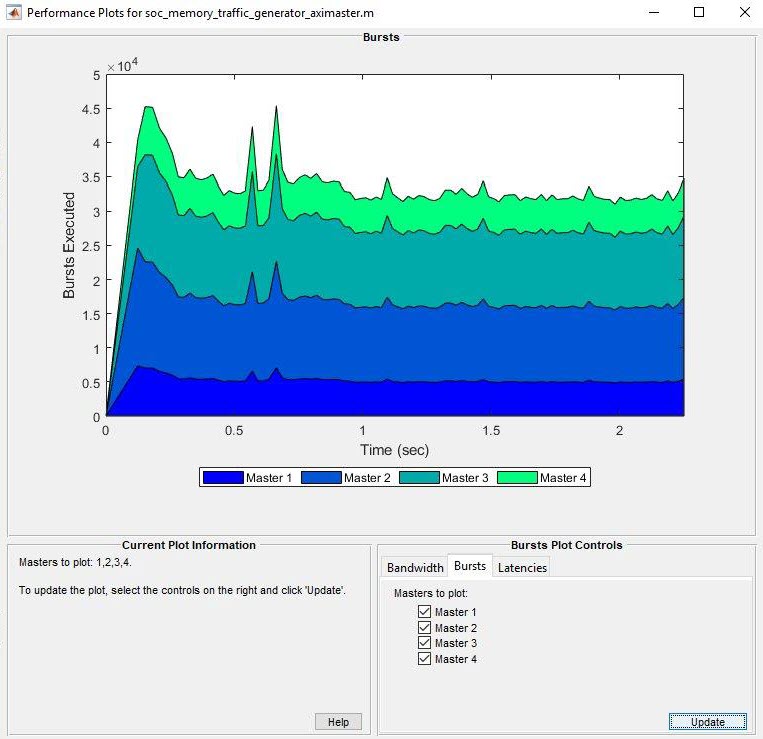

Пример см. в разделе Анализ пропускной способности памяти с использованием генераторов трафика, в котором показано, как контролировать производительность памяти как при моделировании, так и при работе на FPGA. Сценарий, созданный инструментом SoC Builder, использует соединение JTAG для включения любых генераторов трафика в вашей конструкции, а затем выполняет выборку информации о производительности памяти из IP-адреса монитора межсоединений AXI как можно быстрее. Интервал выборки зависит от задержки JTAG, которая обычно составляет от 10 мс до 20 мс. Затем сценарий отображает графики, аналогичные графикам производительности из блока контроллера памяти в моделировании. График отображает полосу пропускания, количество пакетов и задержку транзакций для каждого хозяина.

Примечание

Сам ведущий модуль AXI не подключен к монитору межсоединений AXI. Следовательно, аппаратная диагностика не включает в себя графики использования памяти только для мастеров тестового стенда, которые инициализируют память с заранее определенными данными.

Сценарий собирает метрики производительности с монитора межсоединений AXI и запускает приложение графика производительности.

На вкладке Пропускная способность выберите основные параметры, для которых требуется построить график пропускной способности. Щелкните Создать график (Create Plot), чтобы просмотреть пропускную способность в мегабайтах в секунду для выбранных шаблонов в течение времени выполнения. На этом рисунке показана полоса пропускания для примера «Анализ полосы пропускания памяти с использованием генераторов трафика».

На вкладке Пакеты выберите шаблоны, для которых требуется построить график пакетов. Щелкните Создать график (Create Plot), чтобы просмотреть количество пакетов, выполненных для выбранного шаблона в течение времени выполнения. На этом рисунке показано число пакетов для примера анализа пропускной способности памяти с использованием генераторов трафика.

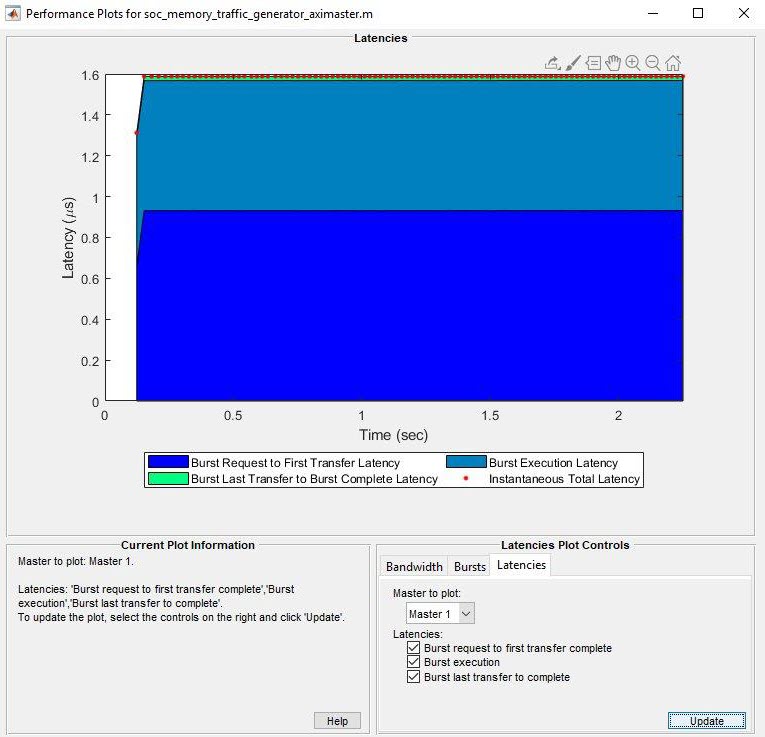

На вкладке Задержки выберите шаблон, для которого требуется построить график задержек. Щелкните Создать график (Create Plot), чтобы увидеть задержку для выбранных основных объектов в течение времени выполнения. На этом рисунке показана общая задержка для Master 1 в примере Анализ пропускной способности памяти с использованием генераторов трафика. Затем можно увеличить масштаб изображения для анализа максимальной мгновенной задержки.

Можно выбрать один из следующих вариантов:

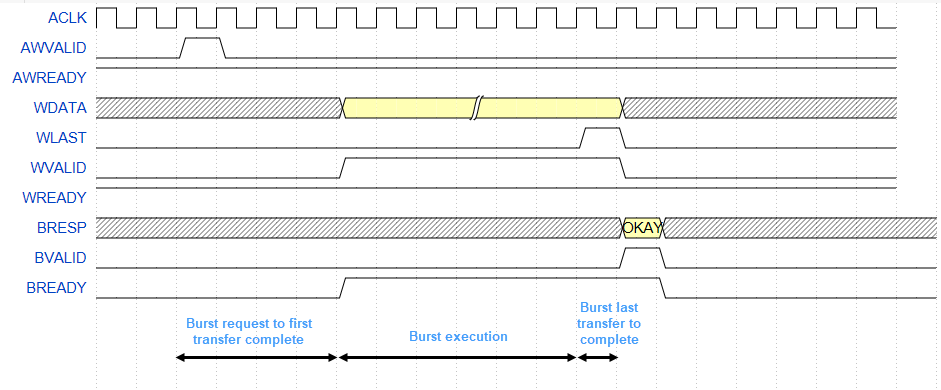

Burst request to first transfer complete - этот параметр показывает время, которое требуется от момента выдачи мастером запроса на транзакцию до первой передачи данных. Эта задержка приводит к задержкам арбитража или межсоединений.

Выполнение пакета - этот параметр показывает время, необходимое от первой передачи данных до последней передачи пакета.

Burst last transfer to complete - этот параметр показывает время, необходимое от последнего переноса до завершения транзакции. В случае транзакции чтения значение равно 0.

Мгновенная суммарная задержка - этот параметр показывает дискретные измерения суммарной задержки на пакет.

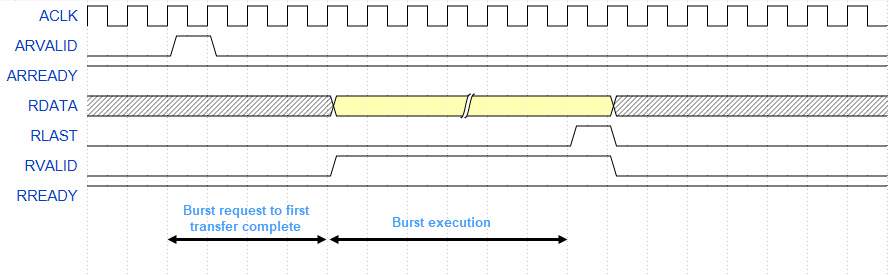

Каждое записанное на график значение задержки представляет собой среднее значение соответствующей задержки, измеренной из транзакций памяти в течение интервала выборки. На следующем рисунке показана транзакция записи и чтения протокола AXI4 Master на оборудовании, показывающая каждую из этих задержек.

Запись транзакции

Прочитать транзакцию

В транзакции чтения время последней передачи пакета до полной задержки равно нулю.

В Profile режим, collectMemoryStatistics дискретизирует метрики памяти: значения пропускной способности, пакетов и задержек от аппаратных средств после каждой выборки. После этого функция сбрасывает счетчики метрик, а затем снова запускает счетчики для следующей выборки. Если какой-либо из метрических счетчиков превышает предел 232-1 в пределах интервала выборки, счетчик переполняется, и соответствующая выборка обозначается * на графике.

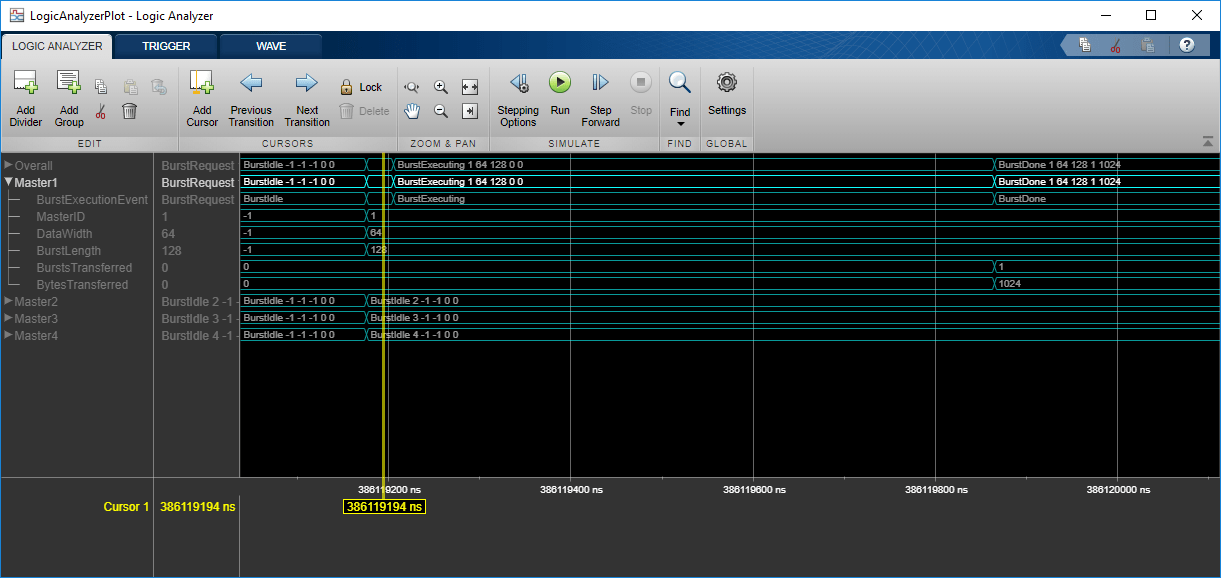

Можно также изменить сгенерированный сценарий, чтобы настроить монитор межсоединений AXI для сбора данных о событиях для каждой пакетной транзакции. Эти события можно просмотреть в средстве просмотра формы сигнала Logic Analyzer для проверки поведения арбитража. Укажите количество транзакций для захвата, глубину отслеживания в параметрах конфигурации модели по пути Аппаратная реализация > Целевые аппаратные ресурсы > FPGA design (debug).

Формы сигналов показывают тип события (BurstIdle, BurstRequest, BurstExecuting, или BurstDone) и эти параметры пакетной транзакции:

MasterID -- идентификационный номер хозяина памяти, который сделал запрос

DataWidth - Ширина данных в битах

BurstLength - Количество слов данных в запросе пакета

BurstsTransferred - Количество пакетов в этом запросе (действительно только с BurstDone событие)

BytesTransferred -- Количество байт в этом запросе (допустимо только с BurstDone событие)

Эти формы сигналов можно сравнить с формами сигналов, полученными из блока контроллера памяти при моделировании.

Монитор межсоединений AXI (AIM) - это ядро IP, которое собирает метрики производительности для конструкции FPGA на основе AXI. Создание socIPCore для настройки и конфигурирования AIM IP и использования socMemoryProfiler для извлечения и отображения данных.

Пример настройки и запроса AIM IP в конструкции с использованием MATLAB в качестве AXI Master см. в разделе Анализ пропускной способности памяти с использованием генераторов трафика. В частности, просмотрите soc_memory_traffic_generator_axi_master.m сценарий, который настраивает и контролирует конструкцию на устройстве.

Монитор межсоединений AXI может собирать данные двух типов. Выбирать Profile режим сбора данных о средней задержке транзакций и счетчиках байтов и пакетов. В этом режиме можно открыть инструмент графика производительности, а затем настроить его для графика пропускной способности, количества пакетов и задержки транзакций. Выбирать Trace режим для сбора подробных данных о событиях транзакций в памяти и просмотра данных в виде сигналов.

perfMonMode = 'Profile'; % or 'Trace'

Чтобы получить показатели производительности диагностики из созданной конструкции FPGA, необходимо настроить соединение JTAG с устройством из MATLAB. Загрузить a .mat файл, содержащий структуры, полученные из параметров конфигурации платы. Этот файл был создан инструментом SoC Builder. Эти структуры описывают межсоединение памяти и основные конфигурации, такие как размеры буфера и адреса. Используйте socHardwareBoard объект для настройки соединения JTAG.

load('soc_memory_traffic_generator_zc706_aximaster.mat'); hwObj = socHardwareBoard('Xilinx Zynq ZC706 evaluation kit','Connect',false); AXIMasterObj = socAXIMaster(hwObj);

socIPCore объект предоставляет функцию, выполняющую эту инициализацию. Затем настройте socMemoryProfiler объект для сбора метрик.apmCoreObj = socIPCore(AXIMasterObj,perf_mon,'PerformanceMonitor','Mode',perfMonMode); initialize(apmCoreObj); profilerObj = socMemoryProfiler(hwObj,apmCoreObj);

Для извлечения показателей производительности или данных сигналов из конструкции, запущенной в FPGA, используйте socMemoryProfiler функции объекта.

Для Profile режим, вызовите collectMemoryStatistics функция в цикле.

NumRuns = 100; for n = 1:NumRuns collectMemoryStatistics(profilerObj); end

Для Trace режим, вызовите collectMemoryStatistics функция один раз. Эта функция останавливает IP от записи транзакций в FIFO в мониторе межсоединений AXI IP, хотя транзакции продолжаются на межсоединении. Задайте размер транзакции FIFO, глубину отслеживания в параметрах конфигурации модели по пути Аппаратная реализация > Целевые аппаратные ресурсы > FPGA design (debug).

collectMemoryStatistics(profilerObj);

Визуализация данных о производительности с помощью plotMemoryStatistics функция. В Profile эта функция открывает инструмент графика производительности, который можно настроить для построения графика пропускной способности, количества пакетов и средней задержки транзакций. В Trace эта функция открывает инструмент Logic Analyzer для просмотра данных о событиях пакетной транзакции.

plotMemoryStatistics(profilerObj);

collectMemoryStatistics | Контроллер памяти | plotMemoryStatistics | socMemoryProfiler