Шаблон RASEoC предоставляет модель моделирования для эталонной конструкции SoC, доступной из пакета поддержки SoC Blockset™ для устройств Xilinx ®. Этот шаблон используется для моделирования всей ссылочной конструкции. Анализ влияния внутренних и внешних соединений на алгоритмы передачи и приема, такие как поведение памяти и радиочастотное (RF) поведение ввода-вывода (I/O).

Чтобы начать работу с моделью SoC Blockset для проектирования системы беспроводной связи с поддержкой RASEoC, выполните действия в разделе Создание модели SoC с помощью шаблона SoC Blockset. Затем добавьте алгоритмы передатчика и приемника в подсистему FPGA и алгоритм процессора в подсистему процессора.

Toolbox™ системы DSP

Пакет поддержки пакетов SoC для устройств Xilinx

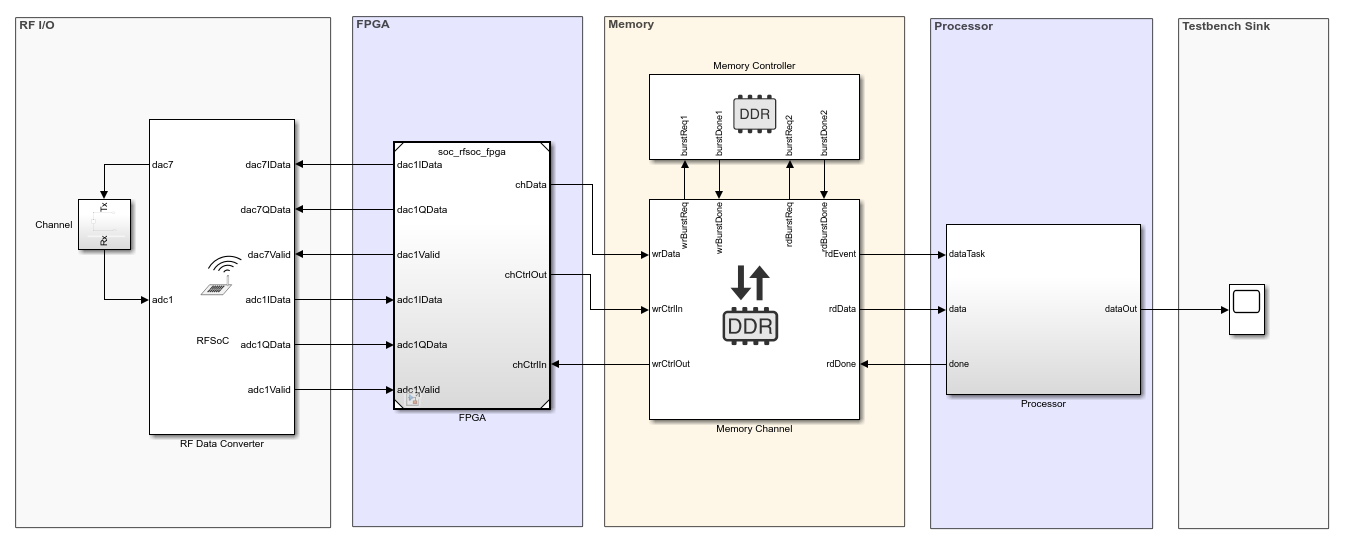

Шаблон RFSoC включает три модели: модель Top, модель FPGA и модель Processor. В модели Top блок RF Data Converter подключается к блоку FPGA и обеспечивает интерфейс RF-ввода/вывода. Блок FPGA реализует алгоритмы приемника и передатчика. Алгоритм FPGA включает в себя блок тестового источника, который генерирует синусоидальный сигнал и подает его на цифроаналоговый преобразователь (ЦАП) через подсистему алгоритма передатчика. Подсистема алгоритма передатчика реализована как простые проходные провода, а подсистема алгоритма приемника реализована с использованием логики понижающего дискретизации. Регистр конфигурации SrcSelReg моделируется в FPGA для выбора источника данных для подсистемы алгоритма приемника. Процессор записывает регистр SrcSelReg для выбора либо тестового источника из FPGA, либо радиочастотных данных из аналого-цифрового преобразователя (АЦП) в блоке RF Data Converter. Данные из подсистемы FPGA передаются в подсистему процессора через блок канала памяти. Параметр Channel Type в блоке Memory Channel имеет значение AXI4-Stream to software via DMA, которая моделирует передачу данных прямого доступа к памяти (DMA) через общую внешнюю память.

Используйте этот шаблон в качестве руководства, заменив подсистемы алгоритма приемника и алгоритма передатчика в модели FPGA и подсистемы алгоритма процессора в модели процессора собственными функциональными возможностями. В этом шаблоне блок RF Data Converter конфигурируется с пользовательским RF-интерфейсом, который имеет один DAC (DAC7) и один ADC (ADC1) и цифровой интерфейс I/Q. Количество выборок за тактовый цикл устанавливается равным 2. Радиочастотный тракт в этом шаблоне закольцовывается. Если требуется использовать различные данные для передатчика и приемника, можно снять закольцовывание и предоставить требуемые входные данные в АЦП.

Процессор считывает вычисленные данные из памяти и выполняет дополнительные вычисления (реализованные в шаблоне как проходной провод). Для просмотра результатов моделирования дважды щелкните по блоку «Time Scope» в подсистеме приемников Testbench.

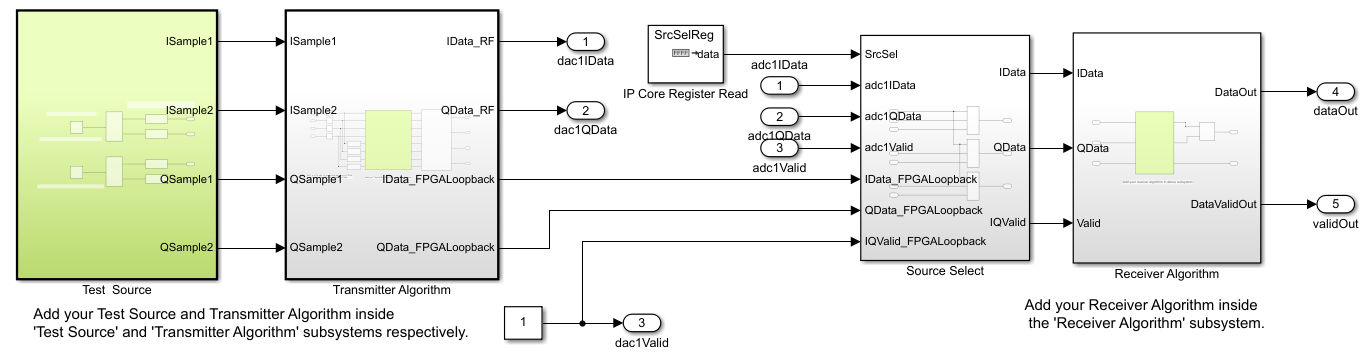

На панели инструментов MATLAB ® на вкладке «Ярлыки проекта» выберите «Открыть модель FPGA». Затем откройте подсистему оболочки FPGA Tx-Rx Alg. Три области выделены зеленым цветом, как показано на этом рисунке. Эти области представляют код пользователя и расположены в блоке тестового источника, подсистеме алгоритма передатчика и подсистеме алгоритма приемника.

Модель FPGA включает эти разделы (выделены зеленым цветом) для изменения.

Блок тестового источника - этот блок генерирует синусоидальный сигнал 500 кГц и передает его в подсистему алгоритма передатчика. Измените тестовый источник на необходимый или замените его альтернативным исходным блоком.

Подсистема алгоритма передатчика - содержит подсистему алгоритма передачи, выделенную зеленым цветом. Замените подсистему Tx Algorithm собственным алгоритмом передатчика.

Подсистема алгоритма приемника - содержит подсистему алгоритма приема, подсвеченную зеленым цветом. Замените подсистему Rx Algorithm собственным алгоритмом приемника.

IP Core Register Read blocks - в тестируемом проекте (DUT) добавьте эти блоки, чтобы добавить регистры в IP-адреса вашего алгоритма. Инициализируйте этот блок с помощью соответствующего блока записи регистра в модели процессора.

Чтобы включить согласованное поведение моделирования, на вкладке Ярлыки проекта (Project Shortcuts) щелкните Открыть модель FPGA (Open FPGA model) и повторите этот шаг.

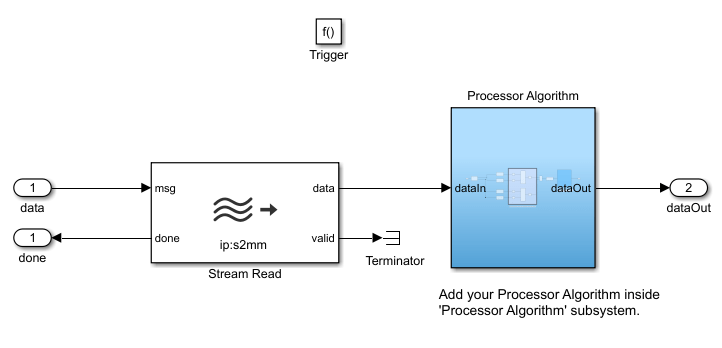

На панели инструментов MATLAB на вкладке Ярлыки проекта (Project Shortcuts) щелкните Открыть модель процессора (Open Processor model). Модель процессора содержит оболочку алгоритма процессора и подсистемы инициализации функции. Подсистема оболочки алгоритма процессора выделена синим цветом, который представляет код пользователя для алгоритма процессора. Откройте подсистему оболочки алгоритма процессора и замените внутреннюю подсистему алгоритма процессора (также выделенную синим цветом) требуемым алгоритмом. Откройте подсистему Initialize Function и добавьте блок записи регистров для каждого блока чтения регистров ядра IP, добавленного в модель FPGA.

Использование шаблона для создания модели SoC