Шаблоны моделей SoC Blockset™ предоставляют шаблоны проектирования и передовые практики для моделей, предназначенных для моделирования, генерации кода HDL или развертывания SoC. Модели, созданные из любого из шаблонов моделей SoC Blockset, имеют свои параметры конфигурации, настроенные для моделирования и генерации кода.

Чтобы эффективно моделировать оборудование для проектирования SoC, создайте проект с помощью шаблона набора блоков SoC.

На вкладке Главная страница MATLAB ® нажмите кнопку Simulink. Либо в командной строке введите:

simulink

На начальной странице Simulink ® прокрутите вниз до раздела «Набор блоков SoC», который содержит ссылки на шаблоны SoC для общих рабочих процессов. Выберите шаблон и сохраните проект. В рабочей области откроется папка проекта, содержащая:

Модель с именем soc_*_top.slx - модель верхнего уровня для проекта SoC.

referencedmodels - папка, содержащая модели, на которые ссылается верхняя модель. Некоторые шаблоны включают модель FPGA и модель процессора. Другие шаблоны включают только одну ссылочную модель: модель FPGA или модель процессора.

utilities - папка, содержащая служебные функции или данные testbench, используемые моделью.

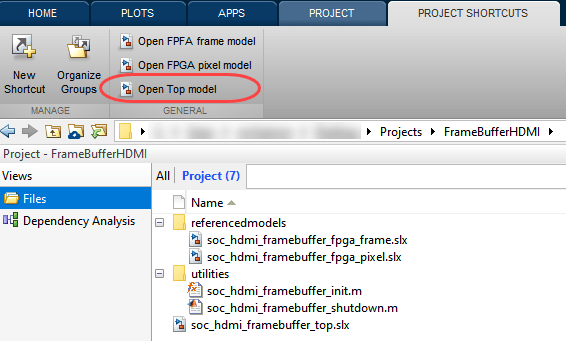

Чтобы открыть модель верхнего уровня в Simulink, на вкладке «Ярлыки проекта» нажмите «Открыть модель верхнего уровня».

В каждом шаблоне перейдите к блокам, помеченным как Алгоритм FPGA в модели FPGA, или Алгоритм процессора в модели процессора. Эти блоки подсвечиваются для упрощения обнаружения. Замените блоки шаблонов собственной моделью алгоритма.

Совет

Чтобы легко найти блоки алгоритмов, следуйте аннотациям в иерархии модели.

Чтобы открыть библиотеку блоков SoC, нажмите кнопку «Обозреватель библиотек», а затем выберите «SoC Blockset» на левой панели. Либо в командной строке введите:

soclib

Верхняя модель в шаблоне SoC Blockset включает в себя подсистему FPGA, которая представляет логику, предназначенную для программирования FPGA. Подсистема FPGA включает два варианта модели Simulink:

Модель FPGA на основе кадров - для повышения производительности моделирования

Модель FPGA на основе образцов - для точности цикла и генерации кода

Верхняя модель также включает в себя процессорную подсистему, которая представляет программную программу, предназначенную для работы на процессоре SoC. И FPGA, и верхние подсистемы содержат блоки, помеченные как алгоритм FPGA или алгоритм процессора. Замените эти алгоритмы собственной логикой. Верхняя модель шаблона также включает в себя систему памяти, с контроллером памяти и каналами памяти. Эти блоки представляют систему физической памяти на плате. Модель часто включает в себя канал регистрации (для обеспечения связи между процессором и FPGA), средства тестирования или блоки ввода-вывода.

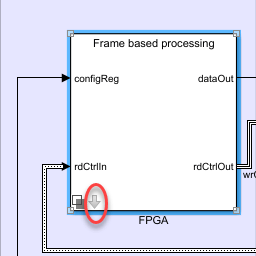

В верхней модели откройте модель FPGA, щелкнув стрелку внизу слева от блока FPGA:

Модель FPGA содержит два варианта модели: вариант на основе кадра и вариант на основе образца. Дважды щелкните вариант модели, который требуется изменить. Модель FPGA обычно включает две основные подсистемы для изменения:

Обертка алгоритма FPGA - дважды щелкните, чтобы открыть модель. Оболочка алгоритма содержит подсистему, выделенную зеленым цветом, с именем FPGA Algorithm. Этот блок имеет два входа и один выход и реализован как множитель. Замените этот блок собственным алгоритмом FPGA. При необходимости добавьте входные и выходные данные.

Оболочка тестового источника - этот блок включает тестовый источник и предназначен для генерации стимула в качестве входных данных алгоритма FPGA. Измените тестовый источник в соответствии с вашими потребностями или замените его альтернативным исходным блоком. Если вход в алгоритм FPGA направляется из блока ввода-вывода, такого как HDMI или SDR, рассмотрите возможность использования определенного шаблона приложения.

Примечание

Не все шаблоны включают блок тестового источника в модель FPGA.

Модель процессора включает в себя блок диспетчера задач и оболочку процессора. Шаблон реализует алгоритм процессора как провод «прохождения». Откройте оболочку алгоритма процессора и замените блок «Алгоритм процессора» (выделен синим цветом) требуемым алгоритмом.

Верхняя модель шаблона также включает в себя канал регистрации для связи между процессором и моделью FPGA. Используйте канал регистра для конфигурирования режима FPGA, l или для считывания и проверки регистров состояния. Блок канала регистрации в шаблоне включает в себя один регистр. Для добавления дополнительных регистров необходимо изменить параметры блока каналов регистров, алгоритм FPGA и алгоритм процессора :

Добавить регистры в канал регистров - дважды щелкните блок канала регистров, чтобы открыть маску блока и при необходимости добавить дополнительные регистры. Добавление регистров создает дополнительные порты в блоке канала регистрации. Дополнительные сведения см. в разделе Регистрация канала.

Добавление портов в модель процессора - переход к модели оболочки алгоритма процессора. Чтобы перейти к модели процессора, щелкните Открыть модель процессора (Open Processor model) на вкладке Ярлыки проекта (Project Shortcuts). Дважды щелкните обертку алгоритма процессора, чтобы изменить ее.

Для регистров записи добавьте выходной порт в модуль и добавьте логику для управления значением добавленного выходного порта. Для регистров считывания добавьте входной порт и логику для обработки информации, возвращаемой из регистра считывания. Из верхней модели подключите порт к блоку Register Channel.

Добавление портов в модель FPGA - переход к модели оболочки алгоритма FPGA. Для перехода к модели обработки FPGA/Frame щелкните Открыть образец модели FPGA (Open FPGA sample model) на вкладке Быстрые ссылки на проект (Project Shortcuts). Дважды щелкните обертку алгоритма FPGA, чтобы изменить ее.

Для регистров записи добавьте входной порт к модулю и логику для обработки информации, возвращаемой из регистра считывания. Для чтения регистров добавьте выходной порт и логику для управления значением добавленного выходного порта.

Для эквивалентного поведения при использовании варианта на основе образца Simulink повторите этот шаг для модели обработки на основе образца в оболочке FPGA.

Из верхней модели подключите новый порт к блоку Register Channel.

Канал памяти | Контроллер памяти | Зарегистрировать канал | Диспетчер задач