Вы можете использовать пакет поддержки Vision HDL Toolbox™ для аппаратного обеспечения на базе Xilinx ® Zynq ® для прототипирования алгоритмов зрения на оборудовании на базе Zynq, подключенном к реальным устройствам ввода и вывода видео. Используйте пакет поддержки для:

Записывайте входное или выходное видео с платы и импортируйте его в Simulink ® для разработки и проверки алгоритма.

Создание и развертывание IP-ядер vision на плате FPGA. (требуется HDL Coder™)

Создание и развертывание кода C для процессора ARM ® на системной плате. Вы можете направлять видеоданные из FPGA в процессор ARM ® для разработки алгоритмов обработки видео, предназначенных для процессора ARM. (требуется встроенный кодер ®)

Просмотрите выходные данные алгоритма на устройстве HDMI.

С помощью этого пакета поддержки можно записывать живое видео с устройства Zynq и импортировать его в Simulink. Источником видеосигнала может быть видеосигнал HDMI, поступающий на плату, встроенный генератор тестовой последовательности, включенный в эталонную конструкцию, или вывод пользовательского алгоритма на плате. Можно выбрать цветовое пространство и разрешение входных кадров. Разрешение записи должно совпадать с разрешением входной камеры.

После установки видеокадров в Simulink можно:

Разработка алгоритмов обработки видео на основе кадров, которые работают на вводе данных в реальном времени. Используйте блоки из библиотек Computer Vision Toolbox™ для быстрой разработки алгоритмов с плавающей запятой на основе кадров.

Блок «От кадра до пикселей» панели инструментов Vision HDL используется для преобразования входных данных в поток пикселей. Разработка и проверка алгоритмов потоковой передачи пикселей с использованием других блоков из библиотек Vision HDL Toolbox.

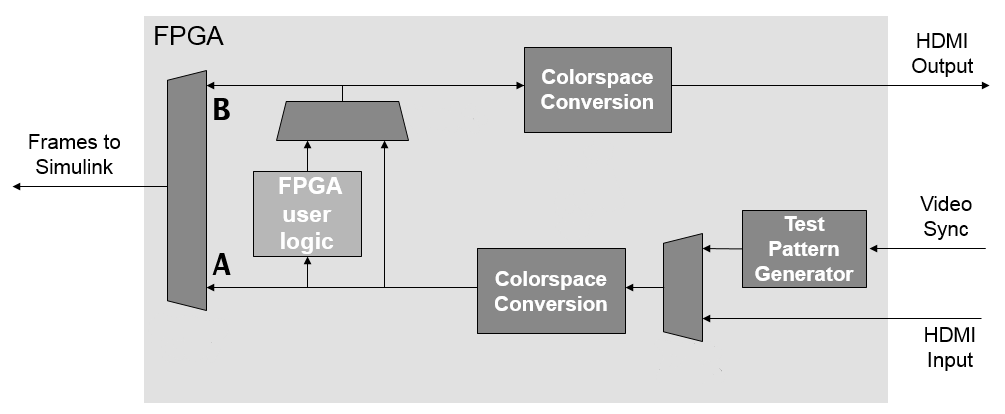

Пакет поддержки инструментов Vision HDL Toolbox для аппаратных средств на базе Xilinx Zynq предоставляет эталонную конструкцию для прототипирования алгоритмов видео на платах Zynq.

При создании IP-ядра HDL для проекта потоковой передачи пикселей с помощью HDL Workflow Advisor ядро включается в эту справочную конструкцию в качестве раздела пользовательской логики FPGA. Пункты A и B на схеме показаны опции для записи видео в Simulink.

Логика пользователя FPGA может также содержать дополнительный интерфейс к буферной памяти внешнего кадра, который не показан на схеме.

Примечание

Эталонная конструкция устройства Zynq требует одинакового разрешения видео и цветового формата для всего пути передачи данных. Выбранное разрешение должно совпадать с разрешением камеры. Конструкция, предназначенная для раздела логики пользователя FPGA, не должна изменять размер кадра или цветовое пространство видеопотока.

Эталонная конструкция не поддерживает многопиксельную потоковую передачу.

Запуская на оборудовании весь или часть проекта потоковой передачи пикселей, вы ускоряете моделирование системы обработки видео и можете проверить ее поведение на реальном оборудовании. Для создания кода HDL и развертывания проекта в FPGA необходимо иметь кодер HDL и пакет поддержки кодера HDL для платформы Xilinx Zynq, а также Xilinx Vivado ® и Xilinx SDK.

После таргетинга FPGA можно записать кадры вывода в реальном времени из логики пользователя FPGA обратно в Simulink для дальнейшей обработки и анализа. Выходные данные также можно просмотреть на выходе HDMI, подключенном к плате. С помощью созданной модели аппаратного интерфейса можно управлять параметрами захвата видео и считывать и записывать порты AXI-Lite в логике пользователя FPGA от Simulink во время моделирования.

Этап нацеливания FPGA также генерирует модель интерфейса программного обеспечения. Эта модель поддерживает таргетинг программного обеспечения на оборудование Zynq, включая внешний режим, процессор в цикле и полное развертывание. Он обеспечивает управление трактом данных и интерфейс с любыми портами AXI-Lite, определенными в целевой подсистеме FPGA. В этой модели можно создать код ARM, который управляет портами AXI-Lite или отвечает на них в логике пользователя FPGA. Затем можно развернуть код на плате для запуска вместе с логикой пользователя FPGA. Для развертывания программного обеспечения на процессоре ARM необходимо иметь встроенный кодер и пакет поддержки встроенного кодера для платформы Xilinx Zynq.