Декодирование турбокодированных выборок

Беспроводная панель инструментов HDL/обнаружение и исправление ошибок

Блок турбодекодера LTE реализует турбодекодер, требуемый стандартом TS 36.212 [1] LTE, и обеспечивает интерфейс и архитектуру, оптимизированные для генерации кода HDL и развертывания аппаратного обеспечения. Блок выполняет итерацию в двух декодерах MAX. Можно указать количество итераций. Скорость кодирования составляет 1/3. Блок принимает кодированные биты как вектор мягкого кодирования 3 на 1, [S P1 P2]. В этом векторе S является систематическим битом, и P1 и P2 - биты четности из двух кодеров.

Этот блок использует интерфейс потоковой выборки с шиной для соответствующих управляющих сигналов. Этот интерфейс позволяет блоку работать независимо от размера кадра и легко соединяться с другими беспроводными блоками HDL Toolbox™. Блок принимает и возвращает значение, представляющее одну выборку, и шину, содержащую три управляющих сигнала. Эти сигналы указывают на достоверность каждого образца и границы кадра. Чтобы преобразовать матрицу в поток выборок и эти управляющие сигналы, используйте блок Frame To Samples или whdlFramesToSamples функция. Полное описание интерфейса см. в разделе Потоковый пример интерфейса.

Блок может принять следующий кадр только после того, как он завершит декодирование предыдущего кадра. Необходимо оставить Iterations * 2 * IterationLatency + BlockSize + 4 циклов простоя между входными кадрами. Задержка полуитерации описана в разделе Алгоритмы. Кроме того, можно использовать функцию ctrl выходного сигнала.end чтобы определить, когда блок готов к новому вводу.

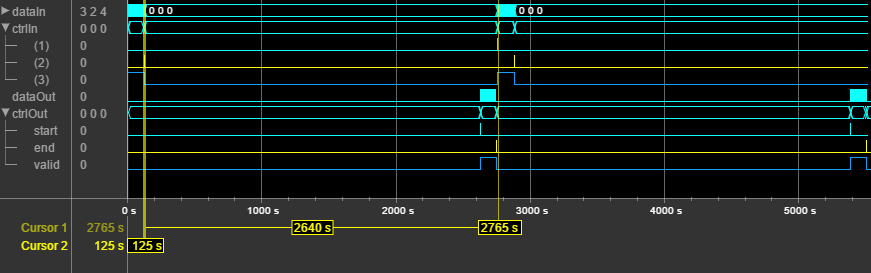

Этот сигнал показывает входной кадр из 120 выборок (+ 4 концевых бита) и 2632 циклов простоя между кадрами. Каждая входная выборка представляет собой вектор из трех фиксированных значений мягкого решения. Входные и выходные шины ctrl расширяются для отображения управляющих сигналов. start и end показать границы кадра, и valid квалифицирует образцы данных.

[1] 3GPP TS 36.212. «Мультиплексирование и канальное кодирование». Проект партнерства 3-го поколения; техническая спецификация на сеть радиодоступа группы; Усовершенствованный универсальный наземный радиодоступа (E-UTRA). URL: https://www.3gpp.org.

[2] Bahl, L.R., J. Cocke, F. Jelinek и J. Raviv. «Оптимальное декодирование линейных кодов для минимизации частоты ошибок символов». Транзакции IEEE по теории информации. Том 1T-20, март 1974, стр. 284-287.

[3] Витерби, Эндрю Дж. «Интуитивное обоснование и упрощенная реализация декодера MAP для сверточных кодов». Журнал IEEE по выбранным областям в коммуникациях. Том 16, № 2, февраль 1998 года.

lteTurboDecode(Панель инструментов LTE) | lteTurboEncode(Панель инструментов LTE)