Декодировать сверточно закодированные данные с помощью алгоритма Витерби

Беспроводная панель инструментов HDL/обнаружение и исправление ошибок

Блок декодера Витерби декодирует сверточно закодированные данные, используя реализацию отслеживания на основе ОЗУ. Декодирование Витерби широко используется в стандарте LTE TS 36.212 [1] и других приложениях с прямой коррекцией ошибок (FEC), таких как беспроводные сети (802.11a/b/g/n/ac), цифровая спутниковая связь, цифровое видеовещание (DVB), IEEE 802.16 и HiperLAN. Для поддержки любого из этих стандартов блок принимает коды свертки с длинами ограничений от 3 до 9, кодовыми скоростями от 1/2 до 1/7 и предоставляет непрерывные, завершенные и усеченные режимы. Блок обеспечивает архитектуру и интерфейс, подходящие для генерации кода HDL.

Блок поддерживает декодирование проколотых кодов, предоставляя дополнительный входной порт стирания. Блок Depuncturer можно использовать для вставки нейтральных значений в поток проколотых образцов и генерации сигнала стирания.

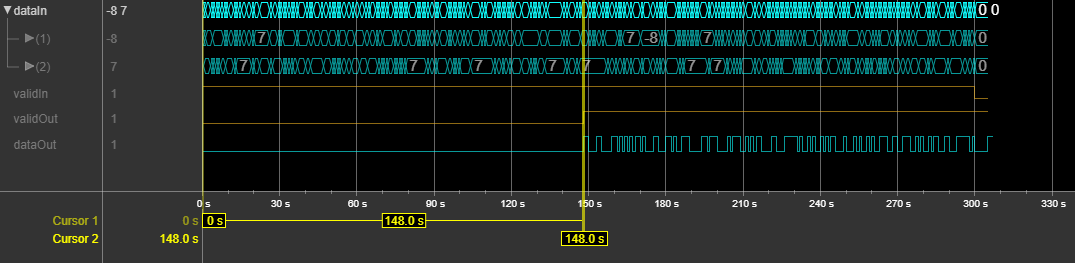

Блок декодера Витерби принимает входные выборки как двоичные значения жесткого решения или логарифмические отношения правдоподобия мягкого решения (LLR). Каждый образец представляет собой вектор-столбец, длина которого зависит от схемы кодирования. Первый сигнал показывает непрерывный режим работы с входными выборками знаковых 4-битовых данных, используя параметры блока по умолчанию. Глубина отслеживания составляет 32. Блок возвращает первую выборку декодированных выходных данных после 148 тактовых циклов. Задержка декодирования равна 4 × Глубина отслеживания + Длина ограничения + 13 допустимых входных циклов.

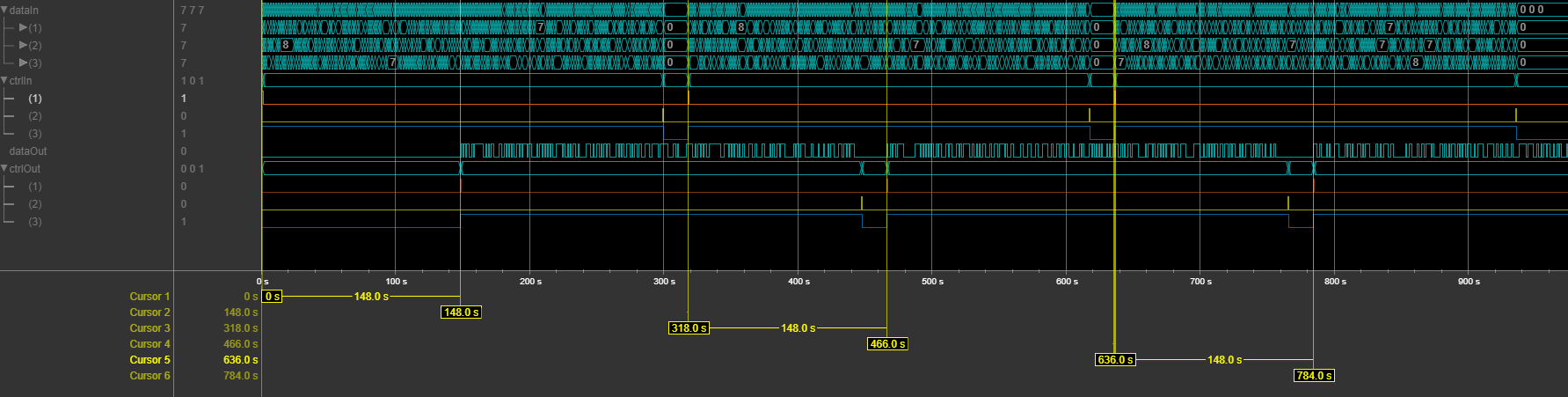

Вторая форма сигнала показывает три кадра в режиме завершенной работы. Вход - это неподписанные 4-битовые выборки, а блок использует решетку (7, [171 133 112]). Глубина отслеживания составляет32. Входные и выходные шины ctrl расширяются для отображения их трех управляющих сигналов. Задержка от каждого ввода ctrl.start для вывода ctrl.start также составляет 148 тактовых циклов.

Управляющие сигналы в шине указывают на достоверность каждого образца и границы кадра. Чтобы преобразовать матрицу в поток выборок и соответствующие управляющие сигналы, используйте блок Frame To Samples или whdlFramesToSamples функция. Полное описание потокового интерфейса примеров см. в разделе Потоковый интерфейс примеров.

[1] 3GPP TS 36.212. «Мультиплексирование и канальное кодирование». Проект партнерства 3-го поколения; техническая спецификация на сеть радиодоступа группы; Усовершенствованный универсальный наземный радиодоступа (E-UTRA). URL: https://www.3gpp.org.

[2] Horwitz, M. и Р. Браун. «Обобщенная методика проектирования для управления памятью выживших Traceback в декодерах Витерби». Материалы Южноафриканского симпозиума по коммуникациям и обработке сигналов 1997 года: 63-68. Пискатауэй, Нью-Джерси: IEEE, 1997.

[3] Шунг, С.б., П.х. Сигел, Г. Унгербек и Х.К. Тапар. «Архитектуры VLSI для метрической нормализации в алгоритме Витерби». IEEE Международная конференция по коммуникациям, включая технические сессии Supercomm: том 4. 1726-728. Нью-Йорк, Нью-Йорк: IEEE, 1990.