FPGA-in-the-loop (FIL) позволяет выполнять моделирование Simulink ®, синхронизированное с конструкцией HDL на плате Intel ® или Xilinx ® FPGA. Эта связь между симулятором и платой позволяет проверить реализацию HDL непосредственно по алгоритмам Simulink или MATLAB ®. Можно применить реальные данные и тестовые сценарии из этих алгоритмов к конструкции ЛПВП на FPGA.

При моделировании беспроводных блоков HDL Toolbox™ необходимо использовать потоковый интерфейс-образец. Потоковая выборка данных, хотя и требуется для аппаратных реализаций систем связи, занимает много времени на интерфейсе FPGA-in-the-loop с Simulink.

Можно преобразовать кадры в образцы и образцы в кадры в Simulink или MATLAB. В зависимости от рабочего процесса можно оптимизировать моделирование FPGA-in-the-loop одним из двух способов.

Одним из рабочих процессов является модель Simulink, которая импортирует кадрированные данные из MATLAB. Этот тип модели затем использует блоки Frame To Samples и Samples To Frame для преобразования формата данных. Для FPGA-in-the-loop замените эти блоки преобразования блоками FIL Frame To Samples и FIL Samples To Frame.

Другим рабочим процессом является модель Simulink, которая импортирует потоковые данные из MATLAB. Этот тип модели включает сценарий MATLAB, в котором используется ltehdlFrameToSamples и ltehdlSamplesToFrames функции. Для FPGA-in-the-loop измените сценарий и модель Simulink так, чтобы они передавали векторы данных в интерфейс FPGA-in-the-loop.

При создании файла программирования для цели FIL в Simulink инструмент создает модель для сравнения моделирования FIL с конструкцией Simulink. Для моделей Wireless HDL Toolbox блок FIL в этой модели воспроизводит интерфейс потоковой передачи образцов и отправляет по одному образцу за раз в FPGA. Обе эти модификации создают векторы, которые обеспечивают более эффективное использование интерфейса между моделью Simulink и платой FPGA.

В следующих инструкциях показано, как изменить модели FPGA-in-the-loop для верифицирующего турбодекодера с потоковыми данными из MATLAB и верифицировать турбодекодер с кадрированными данными из примеров рабочего процесса MATLAB.

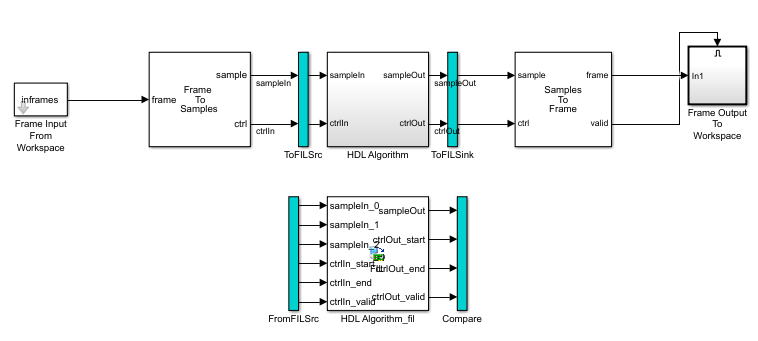

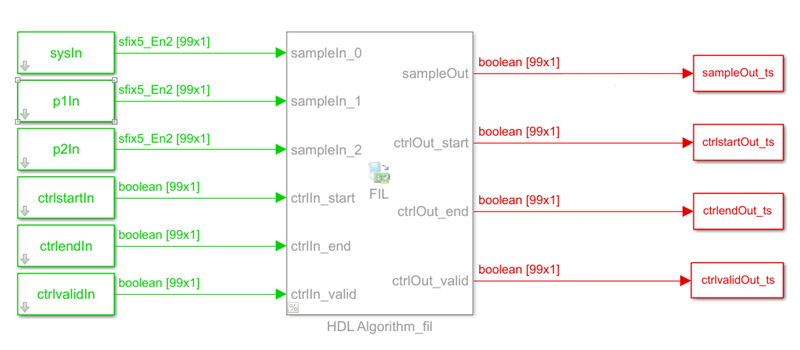

Сгенерированная модель, включая блок FIL, который взаимодействует с платой FPGA, показана для модели, которая преобразуется в потоковые выборки в Simulink. Если каждый образец представлен несколькими значениями, то эти значения сплющиваются в отдельные порты для FIL.

Синяя подсистема ToFILSrc ответвляет вход потока выборок блока алгоритма HDL в подсистему StartFILSrc. Синяя подсистема ToFILSink ответвляет выходной сигнал потока выборки блока алгоритма HDL в подсистему сравнения, где он сравнивается с выходным сигналом блока Algorithm_fil HDL. Эта настройка выполняется медленно, поскольку модель посылает только один образец и связанные с ним управляющие сигналы в каждом пакете на плату FPGA и с нее.

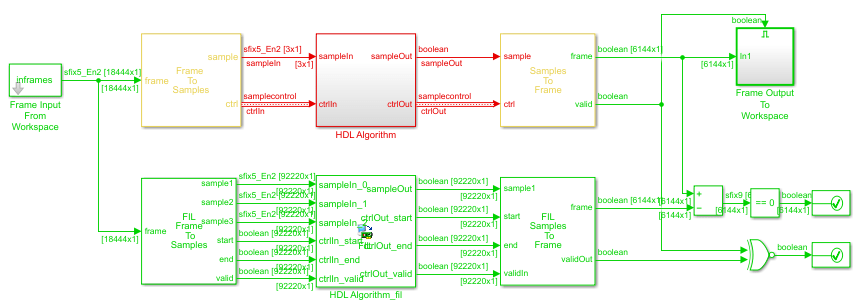

Для улучшения полосы пропускания связи с платой FPGA измените автоматически созданную модель. Модифицированная модель использует блоки FIL Frame To Samples и FIL Samples To Frame для отправки одного кадра за раз.

Чтобы создать эту измененную модель FIL, выполните следующие действия.

Удалите синие подсистемы и создайте ветвь на входном порту кадра блока Frame To Samples.

Вставьте блок FIL Frame To Samples перед блоком Algorithm_fil HDL. Вставьте блок FIL Samples To Frame после блока HDL Algorithm_fil.

Установите размер выходного кадра в блоке FIL равным размеру входного кадра.

В блоках FIL Frame To Samples и FIL Samples To Frame задайте параметры, соответствующие настройкам блоков Frame To Samples и Samples To Frame.

Ответвление выходного кадра блока Samples To Frame для сравнения. Можно сравнить весь кадр сразу с блоком Diff. Сравните validOut сигналы с использованием блока исключающее ИЛИ.

Входной размер в блоке FIL представляет собой размер кадра из входных кадров данных. Размер вектора портов блока FIL не изменяет сгенерированный код HDL. Это влияет только на размер пакета связи между симулятором и платой FPGA. Эта модифицированная модель посылает весь кадр на плату FPGA в каждом пакете, значительно повышая эффективность линии связи.

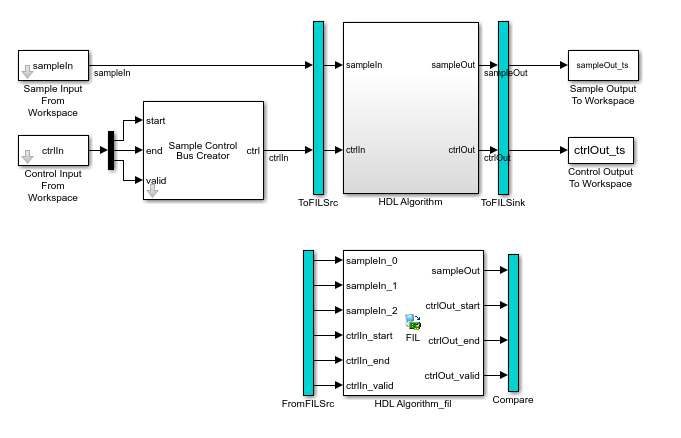

Сгенерированная модель, включая блок FIL, который взаимодействует с платой FPGA, показана для модели, которая преобразуется в потоковые выборки в MATLAB. Если каждый образец представлен несколькими значениями, то эти значения сплющиваются в отдельные порты для FIL.

Синяя подсистема ToFILSrc ответвляет вход потока выборок блока алгоритма HDL в подсистему StartFILSrc. Синяя подсистема ToFILSink ответвляет выходной сигнал потока выборки блока алгоритма HDL в подсистему сравнения, где он сравнивается с выходным сигналом блока Algorithm_fil HDL. Эта настройка выполняется медленно, поскольку модель посылает только один образец и связанные с ним управляющие сигналы в каждом пакете на плату FPGA и с нее.

Для улучшения пропускной способности связи с платой FPGA используйте сгенерированный блок FIL в другой модели. Альтернативная модель импортирует и экспортирует векторы сведенных данных. Сопровождающий сценарий MATLAB изменяет форму входных и выходных данных и проверяет выходные данные FIL на соответствие поведенческой модели. Изменение формы данных в MATLAB проще, и моделирование выполняется быстрее, чем изменение формы в Simulink.

Сначала измените сопутствующий скрипт MATLAB:

Выберите размер кадра для моделирования FIL. Этот размер не обязательно должен соответствовать фактическим размерам кадра в сгенерированных данных. Он может содержать весь набор данных. Блок FIL разделяет данные на пакеты максимального размера для связи с платой FPGA.

filframesize = 99;

Объединение массива ячеек входных кадров в одну матрицу.

allframes = [inframes{:}];

Выровняйте выборки и управляющие сигналы, чтобы создать по одному вектору для каждого входного порта в блоке FIL. Эта модель включает блок турбодекодера LTE, поэтому входные выборки состоят из трех значений.

sysIn = allframes(1:3:end); p1In = allframes(2:3:end); p2In = allframes(3:3:end); ctrlstartIn = ctrlIn(1:3:end); ctrlendIn = ctrlIn(2:3:end); ctrlvalidIn = ctrlIn(3:3:end);

Вызовите модель FIL.

simTime = size(allframes,1);

modelname = 'TurboDecoderStreamingFILVectortoSL';

open_system(modelname);

sim(modelname);

Изменение формы выходных переменных для ввода в whdlSamplesToFrames функция. Воссоздайте матрицу N-by-3 управляющего сигнала и вектор данных выборки. В этом примере выходной образец является единственным значением. Если выходная выборка имеет несколько значений, создайте матрицу выборки N-by-SampleSize.

sampleOut = squeeze(sampleOut_ts.Data); ctrlOut = [squeeze(ctrlstartOut_ts.Data) ... squeeze(ctrlendOut_ts.Data) ... squeeze(ctrlvalidOut_ts.Data)];

Затем создайте модель Simulink:

Скопируйте созданный блок FIL в новую модель.

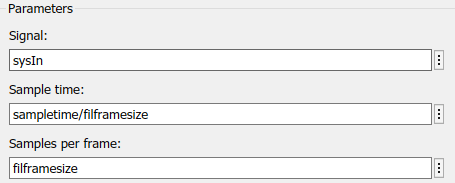

Сконфигурируйте и подключите блок Signal From Workspace для каждого входного порта в блоке FIL. В качестве значений параметров используйте переменные из сценария MATLAB.

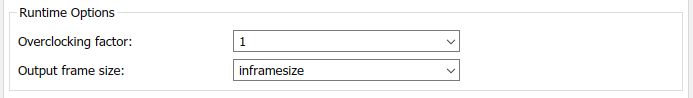

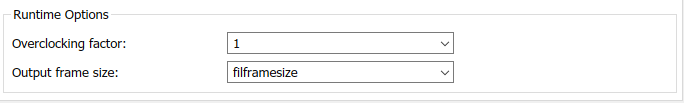

Установите размер выходного кадра в блоке FIL на требуемый размер кадра FIL.

Настройте и подключите блок To Workspace для каждого выходного порта блока FIL.

Размер входного сигнала в блоке FIL - это размер кадра, заданный в блоках «Сигнал в рабочее пространство». Размер вектора портов блока FIL не изменяет сгенерированный код HDL. Это влияет только на размер пакета связи между симулятором и платой FPGA. Эта модифицированная модель посылает весь кадр на плату FPGA в каждом пакете, значительно повышая эффективность линии связи.