Цикл фазовой автоподстройки объединяет управляемый напряжением генератор и фазовый компаратор в качестве системы обратной связи для регулировки частоты или фазы генератора для отслеживания приложенного частотно-модулированного или фазно-модулированного сигнала.

Управляемый напряжением осциллятор является одной из частей цикла фазовой автоподстройки. Блоки Continuous-Time VCO и Discrete-Time VCO реализуют управляемые управляемыми напряжением генераторами. Эти блоки формируют выходные сигналы в непрерывном времени и в дискретном времени, соответственно. Выходной сигнал каждого блока синусоидален и изменяет свою частоту в ответ на изменения амплитуды входного сигнала.

Цикл фазовой автоподстройки (ФАП), при использовании в сочетании с другими компонентами, помогает синхронизировать приемник. ФАПЧ является системой автоматического управления, которая регулирует фазу локального сигнала, чтобы соответствовать фазе принимаемого сигнала. Проект ФАПЛ лучше всего работает для узкополосных сигналов.

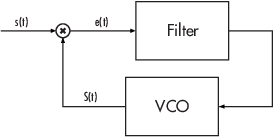

Простая ФАП состоит из детектора фазы, цикла фильтра и управляемого напряжением генератора (VCO). Например, следующий рисунок показывает, как эти компоненты расположены для аналоговой полосы пропускания PLL. В этом случае детектор фазы является всего лишь умножителем. Сигнал e (t) часто называют сигналом ошибки.

В этой таблице указаны поддерживаемые типы PLL и блоки, которые их реализуют.

Поддерживаемые LL в библиотеке компонентов

| Тип ФАПЛ | Блок |

|---|---|

| Аналоговый диапазон пропускания PLL | Phase-Locked Loop |

| Аналоговая модульная полоса PLL | Baseband PLL |

| Linearized analog baseband PLL | Linearized Baseband PLL |

| Цифровая ФАПЛ с использованием зарядного насоса | Charge Pump PLL |

Различные PLL используют различные детекторы фазы, фильтры и характеристики VCO. Некоторые из этих атрибутов встроены в блоки PLL в этом продукте, в то время как другие зависят от параметров, которые вы устанавливаете в маске блока:

Вы задаете передаточную функцию фильтра в маске блока, используя параметры Lowpass filter numerator и Lowpass filter denominator. Каждый из этих параметров является вектором, который перечисляет коэффициенты соответствующего полинома в порядке убывания экспонент переменной s. Для разработки фильтра можно использовать такие функции, как butter, cheby1, и cheby2 в Signal Processing Toolbox.

Вы задаете ключевые характеристики VCO в маске блока. Все четыре блока ФАПЛ используют параметр VCO input sensitivity. Некоторые блоки также используют VCO quiescent frequency, VCO initial phase и VCO output amplitude параметры.

Детектор фазы для каждого из блоков PLL является функцией, которую вы не можете изменить из маски блока.

В отличие от моделей полосы пропускания для фазовой автоподстройки, модель основной полосы не зависит от несущей частоты. Это позволяет вам использовать более низкую частоту дискретизации в симуляции. Два блока реализуют аналоговые PLL основной полосы:

Линеаризированная модель и нелинейная модель отличаются тем, что линеаризированная модель использует приближение

для упрощения расчетов. Это приближение близко, когда И (т) близко к нулю. Таким образом, вместо непосредственного использования входного сигнала и выходного сигнала VCO, линеаризированная модель PLL использует только их фазы.

Накачка заряда ФАПЛ является классическим цифровым ФАПЛ. В отличие от упомянутых выше аналоговых ФАП, накачка заряда ФАП использует последовательный логический детектор фазы, который также известен как цифровой детектор фазы или детектор фазы/частоты.

[1] Gardner, F.M., «Charge-Pump Phase-Lock Loops», IEEE Trans. on Communications, Vol. 28, November 1980, pp. 1849-1858.

[2] Gardner, F.M., «Phase Accuracy of Charge Pump PLLs», IEEE Trans. on Communications, Vol. 30, October 1982, pp. 2362-2363.

[3] Гупта, С.К., «Фаза Locked Циклов», материалы IEEE, том 63, февраль 1975 года, стр. 291-306.

[4] Lindsay, W.C. and C.M. Chie, «A Survey on Digital Phase-Locked Loops», Processions of the IEEE, Vol. 69, April 1981, pp. 410-431.

[5] Mengali, Umberto, and Aldo N 'Andrea, Synchronization Technologies for Digital Receivers, New York, Plenum Press, 1997.

[6] Meyr, Heinrich, and Gerd Ascheid, Synchronization in Digital Communications, Vol. 1, New York, John Wiley & Sons, 1990.

[7] Moeneclaey, Marc, and Geert de Jonghe, «ML-ориентированная NDA-несущая синхронизация для общих вращательно симметричных сигнальных созвездий», Транзакции IEEE по коммуникациям, Vol. 42, No. 8, Aug. 1994, pp. 2531-2533.

[8] Райс, Майкл. Цифровые коммуникации: подход в дискретном времени. Верхняя Седл-Ривер, Нью-Джерси: Prentice Hall, 2009.