Примечание

Для настройки плат не требуется кабель Ethernet или плата SD.

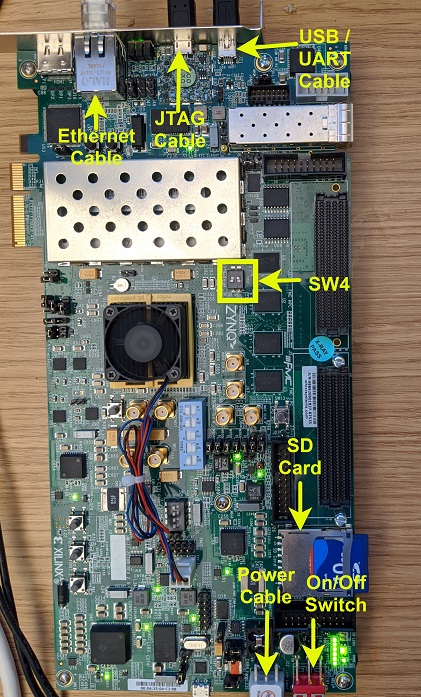

Этот рисунок показывает, как настроить Xilinx® Zynq®-7000 ZC706 оценочной доски. Для настройки платы:

Сконфигурируйте SW4 показано на изображении ниже, и использовать интерфейс Digilent USB-TO-JTAG с помощью следующей таблицы строения:

| Источник строения | SW4 переключатель 1 | SW4 переключатель 2 |

| Ничего | 0 | 0 |

| Коннектор кабеля J3 | 1 | 0 |

| Цифровой интерфейс USB-TO-JTAG | 0 | 1 |

| JTAG (flying lead) Заголовок J62 | 1 | 1 |

Подключите степень шнур и соедините хост-компьютер с платой FPGA с помощью кабеля JTAG, как показано на изображении ниже:

Для использования Ethernet см. Раздел «Создание целевого объекта с интерфейсом Ethernet» и «Установка IP-адреса».

Дополнительные сведения о строении платы см. в Руководстве пользователя Xilinx ZC706 Evaluation Board.

После настройки соединения с платой, чтобы запустить рабочий процесс:

Создайте объект рабочего процесса с помощью имени битового потока, которое предусмотрено для платы, как упомянуто в Use Deep Learning Bitstreams (Пакет поддержки Deep Learning HDL Toolbox для Xilinx FPGA и SoC Devices).

Чтобы узнать больше о рабочем процессе, смотрите Prototype Deep Learning Networks на FPGA и SoCs Workflow.

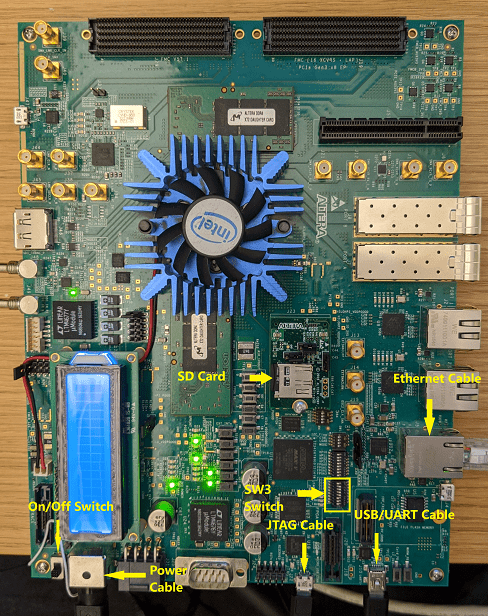

Этот рисунок показывает, как настроить Intel® Arria® 10 Комплект для разработки SoC. Для настройки платы:

Подключите степень шнур и соедините хост-компьютер с платой FPGA с помощью кабеля JTAG.

Задайте SW3 настройки коммутатора:

| Бит 1 | Бит 2 | Бит 3 | Бит 4 | Бит 5 | Бит 6 | Бит 7 | Бит 8 |

| Прочь | На | На | На | На | Прочь | Прочь | Прочь |

Подключите две DDR4 платы плагинов к пазу плагина памяти.

Для использования Ethernet см. Раздел «Создание целевого объекта с интерфейсом Ethernet» и «Установка IP-адреса».

Этот рисунок показывает настройки строения комплекта для разработки Intel Arria 10.

Дополнительные сведения о строении платы см. в Руководстве пользователя по набору для разработки Arria 10.

После настройки соединения с платой, чтобы запустить рабочий процесс:

Создайте объект рабочего процесса с помощью имени битового потока, которое предусмотрено для платы, как указано в разделе Использование Глубоком обучении Bitstreams (Deep Learning HDL Toolbox пакет поддержки для устройств Intel FPGA и SoC).

Чтобы узнать больше о рабочем процессе, смотрите Prototype Deep Learning Networks на FPGA и SoCs Workflow.

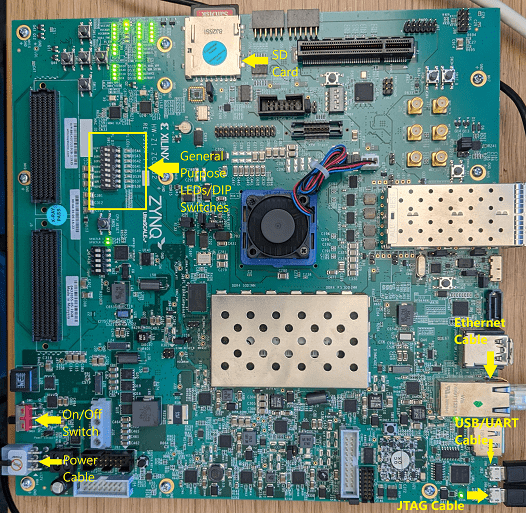

1. Настройте комплект для оценки ZCU102 Xilinx Zynq UltraScale + MPSoC, как показано на рисунке ниже :

Для настройки платы:

Подключите шнур степени. При использовании JTAG подключите плату FPGA к хосту-компьютеру с помощью кабеля JTAG. При использовании Ethernet подключите плату FPGA к хосту-компьютеру с помощью кабеля Ethernet.

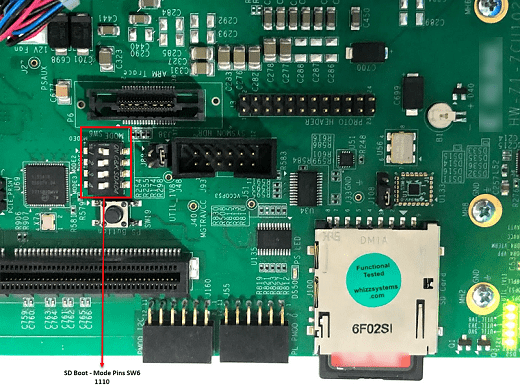

Сконфигурируйте SW6 переключатель, который показан на изображении ниже:

Используйте таблицу строения ниже, чтобы сконфигурировать параметры коммутатора:

| Загрузочный режим | Контакты режима [3:0] | SW6 Положение переключателя [3:0] |

JTAG | 0, 0, 0, 0 | on, on, on, on |

QSPI32 | 0, 0, 1, 0 | on, on, off, on |

SD | 1, 1, 1, 0 | off, off, off, on |

The SW6 положение по умолчанию является QSPI32. Для SW6 DIP-переключатель, перемещающий переключатель к ON метка имеет значение 0.

Для использования Ethernet см. Раздел «Создание целевого объекта с интерфейсом Ethernet» и «Установка IP-адреса».

Для получения дополнительной информации о настройке ZCU102 оборудования см. документацию Xilinx

После настройки соединения с платой, чтобы запустить рабочий процесс:

Создайте объект рабочего процесса с помощью имени битового потока, которое предусмотрено для платы, как упомянуто в Use Deep Learning Bitstreams (Пакет поддержки Deep Learning HDL Toolbox для Xilinx FPGA и SoC Devices).

Чтобы узнать больше о рабочем процессе, смотрите Prototype Deep Learning Networks на FPGA и SoCs Workflow.