Deep Learning HDL Toolbox™ поддерживает режим нескольких кадров, который позволяет записывать несколько изображений в память Double Data Rate (DDR) и одновременно считывать несколько результатов. Чтобы улучшить эффективность развернутых нейронных сетей для глубокого обучения, используйте режим нескольких кадров.

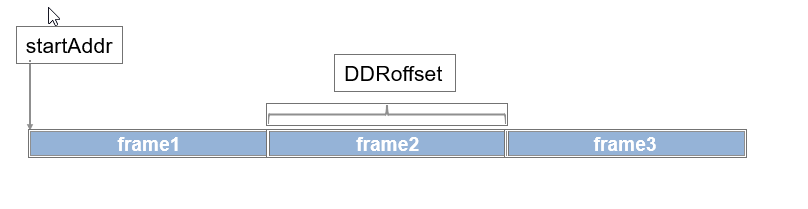

Для форматирования входа изображений в соответствии с форматом DDR входа нескольких кадров требуется:

Начальный адрес входных данных для DDR

Смещение DDR для одинарной входной системы координат изображения

Эта информация автоматически генерируется compile способ. Для получения дополнительной информации о сгенерированных смещениях адресов DDR, смотрите Использование выхода компилятора для системного интегрирования.

Можно также задать максимальное количество входных кадров в качестве необязательного аргумента в compile способ. Для получения дополнительной информации смотрите Сгенерировать смещения памяти DDR на основе количества входных кадров.

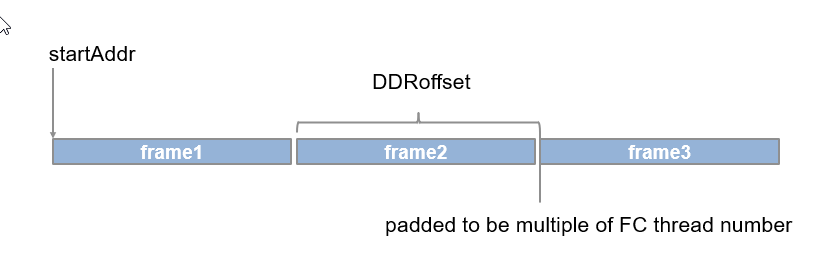

Получение результатов для нескольких входов изображения из выходной области DDR требует:

Начальный адрес выходной области DDR

Смещение DDR одного результата

Результаты выхода должны быть отформатированы, чтобы быть кратными размеру выхода функции FC. Информация и форматирование автоматически генерируются compile способ. Для получения дополнительной информации о сгенерированных смещениях адресов DDR, смотрите Использование выхода компилятора для системного интегрирования.

После развертывания нейронной сети для глубокого обучения можно вручную включить режим нескольких кадров путем записи количества систем координат через порт сетевого строения (NC). Чтобы вручную войти в режим нескольких кадров в MATLAB® в командной строке введите:

dnnfpga.hwutils.writeSignal(1, dnnfpga.hwutils.numTo8Hex(addrMap('nc_op_image_count')),15,hT);Функция addrMap('nc_op_image_count') возвращает адрес регистра AXI для nc_op_image_count, 15 - количество изображений, а hT представляет dlhdl.Target класс, содержащий определение платы и определение интерфейса платы. Для получения дополнительной информации об адресах регистров AXI смотрите Карту регистров процессоров глубокого обучения.

compile | dlhdl.Target | dlhdl.Workflow