(Удалено) БПФ - оптимизировано для генерации HDL-кода с использованием минимальных аппаратных ресурсов

Блок HDL Minimum Resource FFT удален. Используйте БПФ HDL Optimized блок с Architecture набора параметров для Burst Radix 2, вместо этого. Для получения дополнительной информации смотрите Реализация БПФ для FPGA Использование Оптимизированного блока FFT HDL.

Устаревший

dspobs

Блок HDL Minimum Resource БПФ реализует архитектуру БПФ, которая использует минимальное оборудование ресурсы. Блок HDL Minimum Resource БПФ поддерживает Radix-2 с алгоритмом децимации во времени (DIT) для БПФ расчета. Смотрите блок FFT для получения дополнительной информации об этом алгоритме.

Результаты, возвращенные блоком HDL Minimum Resource БПФ, совместимы с результатами, возвращенными блоком БПФ. Операция блока HDL Minimum Resource БПФ отличается от блока БПФ, из-за требований оборудования реализации. Блок Минимальный БПФ ресурса HDL:

Требует последовательного входа

Генерирует последовательный выход

Работает в пакетном режиме ввода-вывода

Блок HDL Minimum Resource БПФ обеспечивает сигналы квитирования для поддержки этих функций.

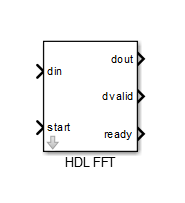

Входные порты:

din: Сигнал входных данных. Требуется комплексный сигнал.

start: Логический сигнал управления. Когда этот сигнал утверждается true (1), блок HDL Minimum Resource БПФ инициирует обработку системы координат данных.

Портами выхода являются:

dout: Выходной сигнал данных. Алгоритм Radix-2 с DIT производит выход с линейным упорядоченным расположением.

dvalid: Логический сигнал управления. Блок HDL Minimum Resource БПФ утверждает этот сигнал true (1), когда пакет действительных выходов данных доступен в dout порт.

ready: Логический сигнал управления. Блок HDL Minimum Resource БПФ утверждает этот сигнал true (1), чтобы указать, что он готов обработать новую систему координат.

Для эффективного оборудования развертывания блока HDL Minimum Resource БПФ необходимо тщательно изучить время входных и выходных потоков данных блока. Следующий рисунок показывает временные отношения между системными часами и start, ready, и dvalid сигналы.

Когда ready задано, start сигнал (активный высокий) запускает блок. Высокий период цикла start сигнал не влияет на поведение блока.

Один тактовый цикл после start триггер, блок начинает загружать данные и ready сигнал отключается. Во время интервала, когда блок загружает, обрабатывает и выводит данные, ready является низким, и start сигнал игнорируется.

The dvalid сигнал утверждается высоким для N тактов (где N - длина БПФ) после завершения обработки. ready возвращается после отправки выходов N значений.

Выражение Tcycle обозначает общее количество тактовых импульсов, требуемых блоком FFT Минимального ресурса HDL для завершения БПФ длины N. Tcycle определяется следующим образом:

Где N > 8

Tcycle = 3N/2-2 + log2(N)*(N/2+3);

Где N = 8

Tcycle = 3N/2-1 +log2(N)*(N/2+3);

Заданные Tcycleзатем можно определить период между утверждениями Минимального ресурсного БПФ HDL start сигнал таким образом, который подходит для вашего приложения. Для примера:

if (N<=8)

startLen = (ceil(Tcycle/N)+1)*N;

else

startLen = ceil(Tcycle/N)*N;

endИспользуйте эту startLen переменная как период генератора импульсов, который управляет БПФ блока минимального ресурса HDL start вход.

Блок HDL Minimum Resource БПФ утверждает и отключает ready и dvalid автоматически. Направьте эти сигналы к частям вашего проекта, которые записывают и считывают из блока HDL Minimum Resource FFT.

FFT Length

По умолчанию: 8

Длина БПФ должна быть степенью 2, в области значений 23 .. 216.

Rounding mode

По умолчанию: Floor

Блок HDL Minimum Resource БПФ поддерживает все режимы округления блока БПФ. См. также ссылку на блоки БПФ.

Overflow mode

По умолчанию: Saturate

Блок HDL Minimum Resource БПФ поддерживает все режимы переполнения блока БПФ. См. также ссылку на блоки БПФ.

Sine table

По умолчанию: Same word length as input

Выберите способ задания размера слова для значений синусоидальной таблицы. Длина дроби значений синусоидальной таблицы равна размеру слова минус единица.

Когда вы выбираете Same word length as input, размеры слова значений синусоидальной таблицы совпадают с таковыми у входа к блоку.

Когда вы выбираете Specify word lengthможно ввести размер слова значений синусоидальной таблицы, в битах, в поле Sine table word length. Значения синусоидальной таблицы не подчиняются параметрам Rounding mode и Overflow mode; они всегда насыщаются и округлятся, чтобы Nearest.

Product output

По умолчанию: Same as input

Используйте этот параметр, чтобы задать, как вы хотите обозначить выходное слово продукта и длины дроби:

Когда вы выбираете Same as inputэти характеристики совпадают с характеристиками входов блока.

Когда вы выбираете Binary point scaling, можно ввести размер слова и длину дроби выходного продукта, в битах, в полях Product word length и Product fraction length.

Accumulator

По умолчанию: Same as input

Используйте этот параметр, чтобы задать, как вы хотите обозначить слово аккумулятора и длины дроби:

Когда вы выбираете Same as product output, эти характеристики совпадают с характеристиками выходных данных продукта.

Когда вы выбираете Same as inputэти характеристики совпадают с характеристиками входов блока.

Когда вы выбираете Binary point scaling, можно ввести размер слова и длину дроби аккумулятора, в битах, в полях Accumulator word length и Accumulator fraction length.

Output

По умолчанию: Same as input

Выберите, как вы задаете выход размера слова и длину дроби:

Когда вы выбираете Same as inputэти характеристики совпадают с характеристиками входов блока.

Когда вы выбираете Binary point scaling, можно ввести размер слова и длину дроби выхода, в битах, в полях Output word length и Output fraction length.

Примечание

Блок HDL FFT пропускает операцию деления на два на выходах бабочки для сигналов с фиксированной точкой.

HDL Coder™ предоставляет дополнительные опции строения, которые влияют на реализацию HDL и синтезированную логику.

Этот блок имеет одну архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров для размещения на выходах путем перемещения существующих задержек в рамках вашего проекта. Распределённая конвейеризация не перераспределяет эти регистры. Значение по умолчанию является |

| InputPipeline | Количество входных этапов конвейера для вставки в сгенерированный код. Распределённая конвейеризация и ограниченная выходная конвейеризация могут перемещать эти регистры. Значение по умолчанию является |

| OutputPipeline | Количество выходных этапов конвейера для вставки в сгенерированный код. Распределённая конвейеризация и ограниченная выходная конвейеризация могут перемещать эти регистры. Значение по умолчанию является |