(Удалено) Radix-2 БПФ с децимацией в частоте (DIF) - оптимизировано для генерации HDL-кода

Блок HDL Streaming FFT удален. Используйте БПФ HDL Optimized блок с Architecture набора параметров для Streaming Radix 2^2, вместо этого. Для получения дополнительной информации смотрите Реализация БПФ для FPGA Использование Оптимизированного блока FFT HDL.

Устаревший

dspobs

Блок HDL Streaming FFT возвращает результаты, идентичные результатам, возвращаемым Radix-2 алгоритмом DIF блока FFT.

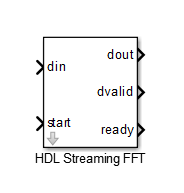

Блок имеет следующие входные порты:

din: Сигнал входных данных. Кодер требует комплексного сигнала с фиксированной точкой.

start: Логический сигнал управления. Когда start утверждает true (1), блок HDL Streaming FFT инициирует обработку системы координат данных.

Блок имеет следующие выходы порты:

dout: Выходной сигнал данных.

dvalid: Логический сигнал управления. Блок HDL Streaming FFT утверждает этот сигнал true (1), когда поток действительных выходных данных доступен в dout порт.

ready: Логический сигнал управления. Блок HDL Streaming FFT утверждает этот сигнал true (1), чтобы указать, что он готов обработать новую систему координат.

Блок HDL Streaming FFT работает в одном из двух режимов:

Continuous data streaming режим: В этом режиме блок HDL Streaming FFT рассчитывает получить непрерывный поток данных в din. После начальной задержки блок генерирует непрерывный поток данных в dout.

Non-continuous data streaming режим: В этом режиме блок HDL Streaming FFT получает непрерывные пакеты потоковых данных в din. После начальной задержки блок производит непостоянные пакеты потоковых данных на dout.

Поведение сигналов управления определяет временной режим блока.

Утверждение start сигнал (активный высокий) запускает обработку блоком HDL Streaming FFT. Чтобы инициировать непрерывную обработку потока данных, задайте start сигнал одним из следующих способов:

Удерживайте сигнал запуска на высоком уровне (как показано на рисунке «Непрерывная потоковая передача данных с сохранением высокого сигнала запуска»).

Импульсируйте стартовый сигнал каждые N тактов, где N - длина БПФ (как показано на рисунке «Непрерывная потоковая передача данных с импульсным начальным сигналом»).

Один тактовый цикл после start триггер, блок начинает загружать данные в din. После первой системы координат потоковых данных блок начинает принимать следующую систему координат потоковых данных.

Между тем, блок выполняет вычисление БПФ на входящих системах координат данных и выводит результаты постоянно на dout. Блок HDL Streaming FFT утверждает и отменяет ready и dvalid автоматически. Блок утверждает dvalid высокий каждый раз, когда выходной поток данных является допустимым. Блок утверждает ready high, чтобы указать, что блок готов к загрузке новой системы координат данных. Когда ready низкая, блок игнорирует start сигнал.

Следующие рисунки иллюстрируют непрерывную потоковую передачу данных. Каждая система координат данных соответствует потоку N входных значений данных, где N - длина БПФ.

Непрерывная потоковая передача данных с высоко удерживаемым стартовым сигналом

Примечание

The start сигнал может быть одним импульсом цикла; он не должен удерживаться высоким для всей системы координат данных. Когда начинается обработка для системы координат, дальше импульсируется start не влияют на обработку этой системы координат. Однако a start импульс должен возникнуть в начале каждой системы координат данных.

Непрерывная потоковая передача данных с импульсным начальным сигналом

В этом режиме блок HDL Streaming FFT получает непрерывные пакеты потоковых данных в din. После начальной задержки блок производит непостоянные пакеты потоковых данных на dout. Пропуски происходят между системами координат данных, когда существует следующее условие:

The start сигнал не утверждает каждый N тактов (где N - длина БПФ)

The start сигнал не постоянно поддерживается высоким.

Непостоянный режим потоковой передачи данных позволяет вам более гибко определять интервалы между потоками входных данных.

Начальная задержка блока HDL Streaming FFT является интервалом между следующими временами:

Время, когда блок начинает получать первую систему координат входных данных

Время, которое утверждает блок dvalid и создает первые действительные выходные данные.

Начальная задержка представляет время, которое блок использует, чтобы загрузить систему координат данных, вычислить БПФ и вывести начало первой выходной системы координат. Следующий рисунок иллюстрирует начальную задержку.

Если вы выбираете опцию блока Display computed initial delay on mask, значок блока отображает начальную задержку. Это отображение представляет время задержки как Z-n, где n - время задержки в выборках.

FFT Length

По умолчанию: 1024

Длина БПФ должна быть степенью 2, в области значений 23 к 216.

Rounding mode

По умолчанию: Floor

Блок HDL Streaming FFT поддерживает все режимы округления блока FFT. См. также ссылку на блоки БПФ.

Overflow mode

По умолчанию: Wrap

Блок HDL Streaming FFT поддерживает все режимы переполнения блока FFT. См. также ссылку на блоки БПФ.

Sine table

По умолчанию: Same word length as input

Выберите способ задания размера слова для значений синусоидальной таблицы. Длина дроби значений синусоидальной таблицы равна размеру слова минус единица.

Когда вы выбираете Same word length as input, размеры слова значений синусоидальной таблицы совпадают с размерами слова входных параметров блока.

Когда вы выбираете Specify word lengthможно ввести размер слова значений синусоидальной таблицы, в битах, в поле Sine table word length. Значения синусоидальной таблицы не подчиняются параметрам Rounding mode и Overflow mode. Они всегда насыщаются и округлятся до Nearest.

Product output

По умолчанию: Same as input

Используйте этот параметр, чтобы задать, как вы хотите обозначить выходное слово продукта и длины дроби:

Когда вы выбираете Same as inputэти характеристики совпадают с характеристиками входов блока.

Binary point scaling: Введите размер слова и длину дроби выходного продукта, в битах, в полях Product word length и Product fraction length.

Accumulator

По умолчанию: Same as input

Используйте этот параметр, чтобы задать, как вы хотите обозначить слово аккумулятора и длины дроби:

Когда вы выбираете Same as product outputэти характеристики соответствуют характеристикам выходного продукта.

Когда вы выбираете Same as inputэти характеристики совпадают с характеристиками входов блока.

Binary point scaling: Введите размер слова и длину дроби аккумулятора, в битах, в полях Accumulator word length и Accumulator fraction length.

Output

По умолчанию: Same as input

Выберите, как вы задаете выход размера слова и длину дроби:

Same as input: эти характеристики совпадают с характеристиками входов блока.

Binary point scaling: позволяет вам ввести размер слова и длину дроби выхода, в битах, в полях Output word length и Output fraction length.

Output in bit-reversed order

По умолчанию: Off

On: Выходной поток данных находится в обратном битовом порядке.

Off: Выходной поток данных в естественном порядке.

Для получения дополнительной информации об эффектах сторнирования битов смотрите Линейный и Обратный битов Выходной порядок.

Display computed initial delay on mask

По умолчанию: Off

On: Значок блока отображает начальную задержку как Z-n, где n - время задержки в выборках.

Off: Значок блока не отображает начальную задержку.

Примечание

Sine table, Product output, Accumulator и Output не поддерживают:

Inherit via internal rule

Slope and bias scaling

HDL Coder™ предоставляет дополнительные опции строения, которые влияют на реализацию HDL и синтезированную логику.

Этот блок имеет одну архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров для размещения на выходах путем перемещения существующих задержек в рамках вашего проекта. Распределённая конвейеризация не перераспределяет эти регистры. Значение по умолчанию является |

| InputPipeline | Количество входных этапов конвейера для вставки в сгенерированный код. Распределённая конвейеризация и ограниченная выходная конвейеризация могут перемещать эти регистры. Значение по умолчанию является |

| OutputPipeline | Количество выходных этапов конвейера для вставки в сгенерированный код. Распределённая конвейеризация и ограниченная выходная конвейеризация могут перемещать эти регистры. Значение по умолчанию является |