Используйте функцию сбора данных FPGA, чтобы наблюдать сигналы от вашего проекта, в то время как проект работает на FPGA. Эта функция захватывает окно данных о сигнале из FPGA и возвращает данные в MATLAB® или Simulink®. Чтобы захватить сигналы, HDL Verifier генерирует IP-ядро, которое вы должны интегрировать в свой HDL-проект и развернуть в FPGA вместе с остальной частью вашего проекта. HDL Verifier также генерирует приложение, модель System object™ и Simulink, которые общаются с FPGA и возвращают данные в MATLAB или Simulink.

Для захвата данных FPGA:

Сгенерируйте настраиваемые компоненты и IP-ядро. Укажите имена и размеры портов для сгенерированного IP-адреса. Эти порты соединяются с сигналами, которые вы хотите захватить, и сигналами, которые вы хотите использовать в качестве триггеров. Запускает управление, когда происходит захват.

Интегрирование сгенерированного IP в проект FPGA и развертывание проекта на плате FPGA. Этот шаг автоматизируется при использовании HDL Workflow Advisor.

Используйте сгенерированное приложение, системный объект или модель Simulink для сбора данных для анализа, верификации или отображения. Можно сконфигурировать условие триггера, чтобы управлять, когда происходит захват.

Для этого шага необходимо загрузить пакет аппаратной поддержки для HDL Verifier. Доступные пакеты поддержки:

HDL Verifier поддержки Intel® Платы FPGA

HDL Verifier пакета поддержки для Xilinx® Платы FPGA

Дополнительная документация по функции сбора данных FPGA включена в комплект установки пакета поддержки. См. раздел Загрузка пакета поддержки платы FPGA (HDL Verifier).

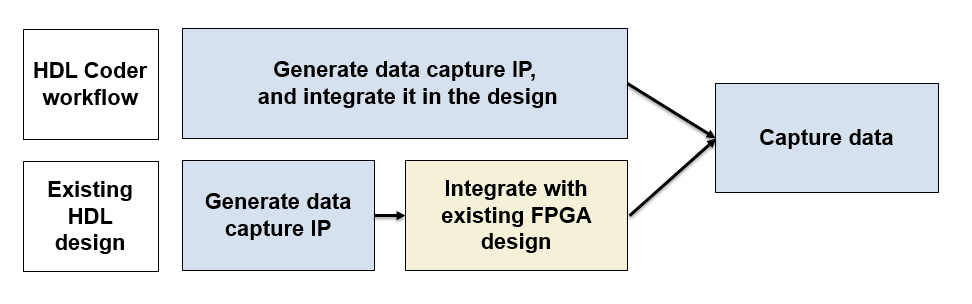

Следующая схема показывает два рабочих процессов для сбора данных:

Рабочий процесс захвата данных (HDL Verifier)

Высокоуровневый рабочий процесс для сбора данных о сигнале из проекта, выполняемого на FPGA.

Начало работы с HDL Workflow Advisor

Изучение основ HDL Workflow Advisor и способов выполнения различных задач.