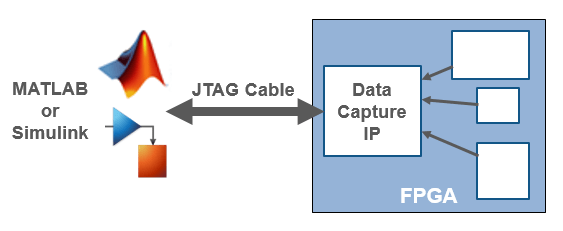

Используйте функцию сбора данных FPGA, чтобы наблюдать сигналы от вашего проекта, пока проект работает на FPGA. Эта функция захватывает окно данных о сигнале из FPGA и возвращает данные в MATLAB® или Simulink®.

Чтобы использовать эту функцию, необходимо загрузить пакет аппаратной поддержки для вашей платы FPGA. См. раздел Загрузка пакета поддержки платы FPGA.

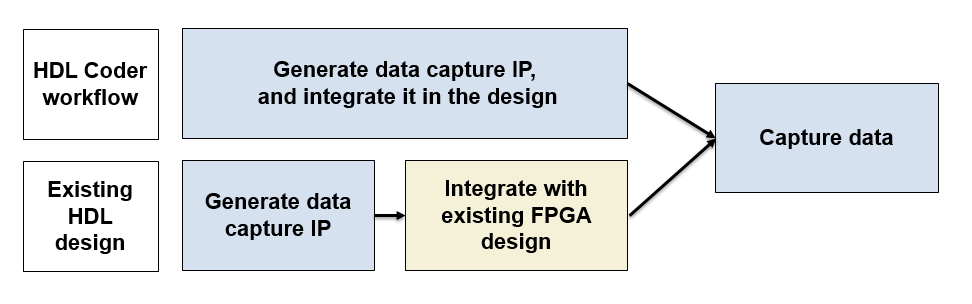

Можно выбрать между двумя рабочими процессами, чтобы захватить данные с платы FPGA и вернуть их в MATLAB или Simulink.

Если вы генерируете HDL-IP с HDL- Coder™, используйте HDL Workflow Advisor, чтобы сгенерировать данные для сбора IP и интегрировать его в ваш проект FPGA.

Если у вас есть существующий проект HDL, используйте инструменты HDL- Verifier™, чтобы сгенерировать IP-адрес захвата данных. Затем вручную интегрируйте сгенерированный IP в проект FPGA.

Чтобы захватить сигналы от вашего проекта, HDL Verifier генерирует IP-ядро, которое взаимодействует с MATLAB. Используйте рабочий процесс HDL Coder, чтобы автоматически интегрировать IP-ядро захвата данных в ваш проект. В противном случае вручную интегрируйте это IP-ядро в проект HDL и развертывайте его в FPGA вместе с остальной частью вашего проекта. Затем используйте один из этих методов для сбора данных.

Для сбора данных в MATLAB - HDL Verifier генерирует настраиваемое приложение, которое возвращает записанному сигналу данные. Кроме того, можно использовать сгенерированный Системный object™ для программного сбора данных.

Для захвата данных в Simulink - HDL Verifier генерирует блок, который имеет выходные порты, соответствующие захваченным сигналам.

В обоих случаях можно задать типы данных для захваченных данных, количество окон для захвата и инициировать условия, которые управляют при выборке данных.

Когда проект работает на FPGA, сначала сгенерированное IP-ядро ожидает заданного условия триггера. Задайте условие триггера путем определения значений, совпадающих по одному или нескольким сигналам. Когда триггер обнаружен, логика захватывает назначенные сигналы в буфер и возвращает данные через интерфейс JTAG в главную машину. Затем можно анализировать и отображать эти сигналы в рабочем пространстве MATLAB или модели Simulink.

Когда вы используете HDL Workflow Advisor для генерации HDL- проекта, сначала отметьте желаемые сигналы как Configure Signals as Тестовых точек (Simulink) в Simulink. Сконфигурируйте свой проект, используя HDL Workflow Advisor, чтобы:

Включите генерацию тестовой точки, выбрав опцию Enable HDL DUT port generation for test points на Set Target Interface шаге. Для получения дополнительной информации смотрите Set Target Interface (HDL Coder).

Подключите сигналы тестовой точки к интерфейсу FPGA Data Capture - JTAG на Set Target Interface шаге.

Настройте buffer size и максимальную глубину последовательности для набора данных на Generate RTL Code and IP Core шаге. Для получения дополнительной информации смотрите Сгенерировать код RTL и IP Core (HDL Coder).

Затем выполните оставшиеся шаги, чтобы сгенерировать HDL для вашего проекта и запрограммировать FPGA. IP-ядро сбора данных интегрировано в сгенерированный проект FPGA. Теперь можно выполнить сбор данных из FPGA.

Пример использования захвата данных с HDL Workflow Advisor см. в Debug IP Core Using FPGA Data Capture (HDL Coder).

Прежде чем захватывать данные FPGA, необходимо сначала указать, какие сигналы нужно захватить и сколько выборок данных вернуть. При использовании существующего проекта используйте приложение FPGA Data Capture Component Generator, чтобы сконфигурировать параметры и сгенерировать IP-ядро захвата данных. Ядро IP содержит:

Порт для каждого сигнала, который вы хотите захватить или использовать как часть условия триггера

Память для захвата количества выборок, которые вы запросили для каждого сигнала

Логика интерфейса JTAG для связи с MATLAB

Логика триггера, которая может быть сконфигурирована во время исполнения

Приложение также генерирует настраиваемое FPGA Data Capture приложение, системный объект и модель, которые общаются с FPGA.

Для связи MATLAB с FPGA необходимо интегрировать сгенерированное ядро IP HDL в проект FPGA. Если вы использовали HDL Workflow Advisor для генерации IP-адреса захвата данных, этот шаг автоматизируется, и IP-адрес захвата данных работает с одночасовой частотой, которая является основным временем тестируемого проекта (DUT). В противном случае следуйте инструкциям в отчете генерации. Добавьте сгенерированные HDL- файлов из hdlsrc папка в проект FPGA. Затем создайте экземпляр IP-ядра HDL, datacapture, в вашем HDL-коде, и соедините его с сигналами, которые вы запросили для захвата и триггеров. Скомпилируйте проект и запрограммируйте FPGA с новым изображением. Теперь можно выполнить сбор данных из FPGA.

IP-ядро захвата данных FPGA сообщается по кабелю JTAG между платой FPGA и хоста-компьютера. Убедитесь, что кабель подключен. Перед захватом данных можно задать типы данных для захваченных данных и задать условия триггера, которые определяют, когда собирать данные. Чтобы сконфигурировать эти опции и захватить данные, можно:

Откройте приложение FPGA Data Capture Set trigger and data type parameters, а затем соберите данные в рабочее пространство MATLAB.

Используйте сгенерированный Системный объект, выведенный из hdlverifier.FPGADataReader. Установите типы данных и инициируйте условие с помощью методов и свойств системного объекта, а затем вызовите объект, чтобы захватить данные.

В Simulink откройте сгенерированную модель и сконфигурируйте параметры блока FPGA Data Reader. Затем запустите модель, чтобы захватить данные.

После захвата данных в рабочее пространство MATLAB или модель Simulink, можно анализировать, проверять и отображать данные.