Преобразуйте скалярный поток или меньшие векторы в векторный сигнал

Операции HDL-кодера/HDL

Блок Deserializer1D буферизует более быстрый, скалярный поток или векторные сигналы в больший, более медленный векторный сигнал. Более быстрый входной сигнал преобразуется в более медленный сигнал на основе Ratio и Idle Cycle значений, преобразование изменяет шаг расчета. Кроме того, выходной сигнал задерживается на один цикл медленного сигнала, потому что сериализованные данные должны быть собраны, прежде чем он может быть выведен как вектор. Для получения дополнительной информации см. приведенные ниже примеры.

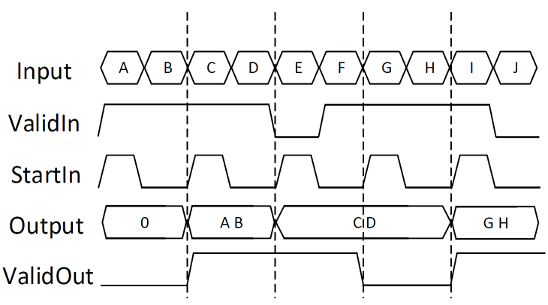

Можно сконфигурировать десериализацию так, чтобы она зависела от действительного входного сигнала ValidIn и стартового сигнала StartIn. Если ValidIn и StartIn параметров блоков выбраны, набор данных начинается только, если оба сигнала ValidIn и StartIn равны true. Рассмотрим этот пример:

Ratio 2 а Idle Cycles есть 0таким образом, каждый выходной цикл является двумя входными сигналами, длинными со всеми рассматриваемыми точками данных.

ValidIn и StartIn выбраны, поэтому набор данных может начаться только тогда, когда оба сигнала StartIn и ValidIn равны true.

ValidOut выбран.

В первом цикле ValidIn и StartIn являются true, поэтому набор данных начинается для A и B. Блок выводит десериализованный вектор в следующем допустимом цикле, поэтому вектор AB выхода в следующем цикле. Это также верно во втором цикле для C и D.

В третьем цикле, начиная с E, StartIn имеет значение true, но ValidIn не имеет значения. E отбрасывается. В F ValidIn имеет значение true, но StartIn - нет, поэтому F также отбрасывается. Поскольку он не может собрать данные для E или F, Deserializer1D выводит вектор предыдущего цикла, CD, но ValidOut изменяется на false.

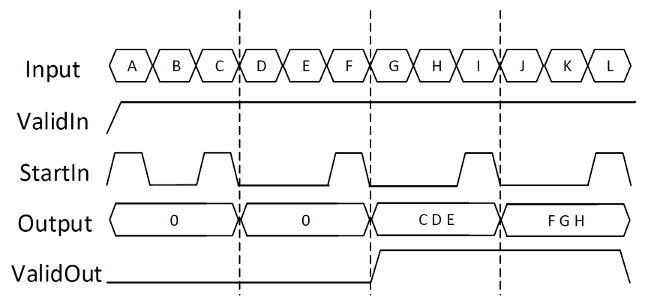

Другой сценарий, который следует учитывать, когда сигнал StartIn приходит слишком рано. Если длина между двумя сигналами StartIn недостаточно велика для сбора полного цикла отношения, недостаточные данные о сигнале сбрасываются. Рассмотрим этот пример:

Ratio 3поэтому каждый цикл имеет длину в две секции.

Idle Cycles 0, поэтому рассматриваются все входы данных.

ValidIn и StartIn выбраны, поэтому набор данных может начаться только тогда, когда оба сигнала StartIn и ValidIn равны true.

ValidOut выбран.

В первом цикле ValidIn и StartIn являются true, поэтому набор данных может начаться для A и B. Однако на C другой сигнал StartIn приходит прежде, чем можно будет собрать три сигнала. Поскольку StartIn прибыл раньше, A и B отбрасываются, и ни один действительный вектор не собирается в течение первого цикла. Поэтому выход второго цикла все еще равен нулю. Десериализация начинается в StartIn на C, для C, D и E. Этот вектор выхода в следующем допустимом цикле, который является циклом 3. Точно так же десериализация снова начинается в StartIn в F и выводит вектор FGH в четвертом цикле.

Вы задаете выход блока для первого периода дискретизации со значением параметра Initial condition.

Введите коэффициент десериализации. По умолчанию это 1.

Отношение является размером выходного вектора, разделенным на размер входного вектора. Коэффициент должен быть делится на вход размера вектора.

Введите количество циклов простоя, добавленных в конец каждого сериализованного входа. По умолчанию это 0.

Значение Idle Cycles влияет на десериализованную скорость выхода. Для примера, если Ratio 2 и входной сигнал A, B, B, C, D, D, ...без неактивных циклов выход будет AB, BC, DD.... Однако для тех же входов и отношения с Idle Cycles установлено на 1, выход следующий AB, CD.... Циклы бездействия, B и D, сбрасываются.

Поведение Deserializer1D меняется, если Idle Cycles не равен нулю, и ValidIn или StartIn включены. Значение цикла ожидания влияет только на выходную скорость, в то время как ValidIn и StartIn управляют тем, какие входные данные десериализованы.

Задайте начальный выход симуляции. Значение по умолчанию 0.

Выберите для активации порта StartIn. Значение по умолчанию отключено.

Выберите для активации порта ValidIn. Значение по умолчанию отключено.

Выберите для активации порта ValidOut. Значение по умолчанию отключено.

Введите размер входных данных сигнала. Размер входа должен быть делится на отношение плюс количество циклов ожидания. По умолчанию блок наследует размер на основе контекста в модели.

Введите временной интервал между попаданиями шаг расчета или укажите другой подходящий шаг расчета, такое как непрерывное. По умолчанию блок наследует свои шаги расчета на основе контекста в модели. Для получения дополнительной информации смотрите Шаг расчета.

Задайте тип входного сигнала блока следующим auto, real, или complex.

SВходной сигнал для десериализации. Типы данных шины не поддерживаются.

ValidInУказывает допустимый входной сигнал. Используйте с блоком Serializer1D. Этот порт доступен при установке флажка ValidIn.

Тип данных: Логический

StartOutУказывает, с чего начать десериализацию. Используйте с блоком Serializer1D. Этот порт доступен при установке флажка StartOut.

Тип данных: Логический

PДесериализованный выходной сигнал. Типы данных шины не поддерживаются.

ValidOutУказывает допустимый выходной сигнал. Этот порт доступен при установке флажка ValidOut.

Тип данных: Логический