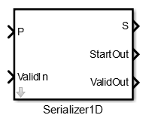

Преобразуйте векторный сигнал в скалярные или меньшие векторы

Операции HDL-кодера/HDL

Блок Serializer1D преобразует сигнал более медленного вектора в более быстрый поток скалярных сигналов или сигналов вектора меньшего размера на основе Ratio и Idle Cycle значений. Чтобы соответствовать более быстрому сериализованному выходу, шаг расчета изменяется согласно этому уравнению:

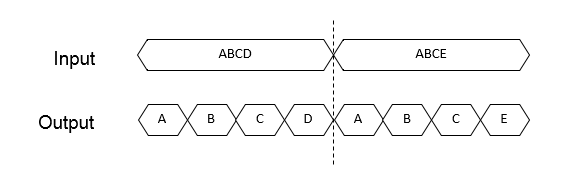

Рассмотрим этот пример, где входные данные являются вектором размера 4, а Ratio установлено на 4.

Данные выходы сериализуют каждый из сигналов вектора в четыре сигнала скаляра. На выходе шага расчета: .

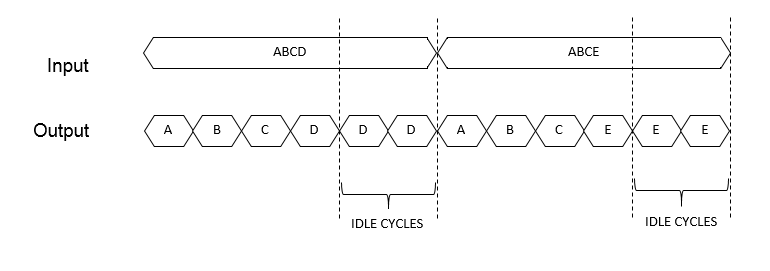

Чтобы добавить циклы бездействия в конец каждого выхода, для Idle Cycles задайте целое число, больше нуля. Рассмотрим этот пример с Ratio, равной 4 и Idle Cycles равной 2.

Для каждого медленного векторного сигнала выход имеет шесть быстрых циклов, состоящих из четырех сериализованных скалярных сигналов и двух неактивных циклов. Значение шага расчета на выходе является .

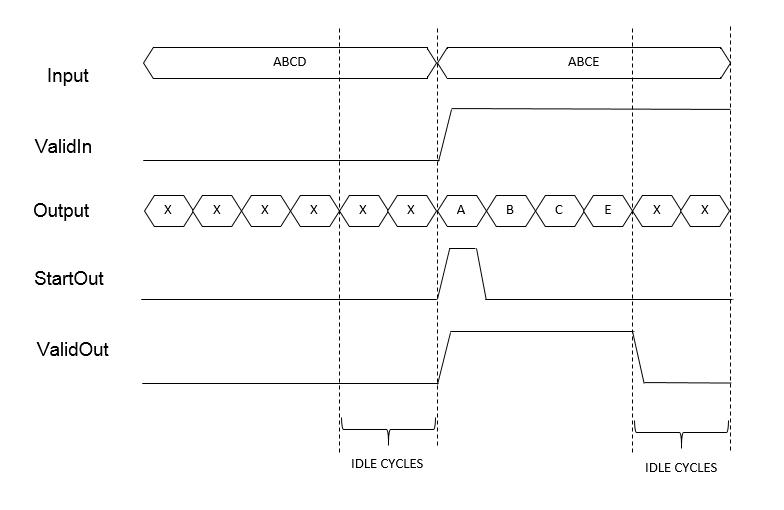

Блок Serializer1D обеспечивает три сигнала управления: ValidIn, ValidOut и StartOut. Можно использовать ValidIn для управления ValidOut и StartOut. Сериализованный выход не зависит от ValidIn. Чтобы определить, действительны ли выходные сериализованные данные, используйте ValidIn и ValidOut. Если вы даете высокий вход ValidIn, и нет циклов ожидания, ValidOut приводит к высокому выходу, что указывает на то, что выходные сериализованные данные действительны.

Рассмотрим пример, который имеет входные данные как вектор размера 4, Ratio установлено равным 4, Idle Cycles установлено равным 2 и использует все три управляющих сигнала.

Для первого входного вектора ABCD, ValidIn ложно. StartOut и ValidOut становятся ложными. Это означает, что значения выходных данных недопустимы. В форме волны значения данных представлены как X, которые соответствуют не заботятся о значениях.

Для второго входного вектора, ABCE, ValidIn верно. Данные выходы сериализируют вектор в четыре скаляра сигнала. Сигнал управления StartOut становится верным на выходе A для указания начала десериализации. В следующем цикле сигнал StartOut становится ложным. ValidOut верно для всех четырех выходных сигналов, указывающих действительные выходные данные для четырех циклов. ValidOut становится ложным для циклов бездействия, и выходы данных не имеют значения значения.

Коэффициент сериализации, заданный как положительная скалярная величина. По умолчанию это 1.

Отношение равно размеру вектора входа, разделенному на размер вектора выхода. Входы размера вектора должны быть делятся на соотношение.

Количество циклов простоя, добавляемых в конце каждого выхода. По умолчанию это 0.

Активирует ValidIn порт. По умолчанию это off.

Активирует StartOut порт. По умолчанию это off.

Активирует ValidOut порт. По умолчанию это off.

Размер входных данных сигнала. Входы размера вектора должны быть делятся на соотношение. По умолчанию блок наследует размер на основе контекста в модели.

Временной интервал между попаданиями шаг расчета или другим подходящим шагом расчета, таким как непрерывный. По умолчанию блок наследует шаг расчета на основе контекста в модели. Для получения дополнительной информации смотрите Шаг расчета.

Тип входного сигнала блока, заданный как auto, real, или complex. По умолчанию это auto.

PВходной сигнал для сериализации. Типы данных шины не поддерживаются.

ValidInВходной сигнал управления. Этот порт доступен при установке флажка ValidIn.

Тип данных: Логический

SСериализованный выходной сигнал. Типы данных шины не поддерживаются.

StartOutВыходной сигнал управления, который указывает, с чего начать десериализацию. Можно использовать этот сигнал как StartIn вход в блок Deserializer1D. Чтобы использовать этот порт, установите флажок StartOut.

Тип данных: Логический

ValidOutВыходной сигнал управления, который указывает на действительный выходной сигнал. Можно использовать этот сигнал как ValidIn вход в блок Deserializer1D. Этот порт доступен при установке флажка ValidOut.

Тип данных: Логический