Сохраняет последовательность входа отсчетов в первом, первом (FIFO) регистре

HDL-кодер/HDL-оперативная память

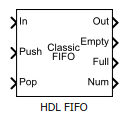

Блок HDL FIFO сохраняет последовательность входа отсчетов в первом регистре (FIFO). Данные, записанные первыми в реестр FIFO, выходят первыми. Реализация блока напоминает модуль FIFO в аппаратных платформах по функциональности и поведению.

In - Входной сигнал данныхscalarВходной сигнал данных в блок FIFO. Когда вы записываете данные в FIFO, самые новые данные выталкиваются в конец реестра FIFO. Блок выталкивает последующие вводы данных ниже этой записи.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

Push - Запись управляющего сигналаscalarКогда этот порт получает значение 1блок нажимает вход в In порт в конец регистра FIFO.

Типы данных: Boolean

Pop - Считайте управляющий сигналscalarКогда этот порт получает значение 1блок выводит первый элемент из реестра FIFO и удерживает Out порт при этом значении.

Типы данных: Boolean

Примечание

Если два или более входных портов управления срабатывают в один и тот же временной шаг, сначала выполняется всплывающая операция, а затем операция push.

Out - Выходной сигнал данныхscalarВыходной сигнал данных от блока FIFO. Когда вы считываете данные из FIFO, данные, которые вы вначале записали в реестр FIFO, выходят из FIFO и удерживаются на выходе.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

Empty - Выходной сигнал данныхscalarУправляющий сигнал, выводимый из FIFO, который становится 1 когда регистр FIFO пуст и не содержит вводов данных.

Чтобы включить этот порт, Show empty register indicator port (Empty) должны быть выбраны.

Типы данных: Boolean

Full - Выходной сигнал данныхscalarУправляющий сигнал, выводимый из FIFO, который становится 1 когда регистр FIFO полон и не может взять больше вводов данных.

Чтобы включить этот порт, Show full register indicator port (Full) должны быть выбраны.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

Num - Количество записейscalarКоличество вводов данных, которые в данный момент находятся в реестре FIFO. Num шагов по 1 для всех данных, которые вы записываете в FIFO. Num сокращения по 1 для всех данных, считанных из FIFO.

Чтобы включить этот порт, Show number of entries register port (Num) должны быть выбраны.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

Register size - Количество записей10 (по умолчанию)Укажите количество записей, которые могут храниться в реестре FIFO. Значение по умолчанию для Register size является 10. Минимальное значение для Register size 4.

Параметры блоков:

fifo_size |

| Тип: Вектор символов |

| Значение: Целое число, больше или равное четырем |

По умолчанию:

'10' |

Mode - Операция'Classic' (по умолчанию) | 'FWFT'Задайте режим операции для FIFO. По умолчанию для Mode задано значение Classic. Вы видите, что значок блока отображается Classic FIFO. Можно изменить Mode на FWFT. При изменении Mode отображается значок блока FWFT FIFO. При помощи FWFT можно искать и видеть первое слово, записанное в реестр FIFO, не делая запроса на чтение. Режим FWFT особенно полезен, когда вы применяете противодавление с AXI4-Stream интерфейсами.

Параметры блоков:

mode |

| Тип: Вектор символов |

Значение:

'Classic''FWFT' | |

По умолчанию:

'Classic' |

The ratio of output sample time to input sample time - Коэффициент частоты дискретизации1 (по умолчанию)Задайте отношение выхода шага расчета к входным шагам расчета. Коэффициент по умолчанию является 1, что означает, что входы In и Push, и выходы Out и Pop, запускать с той же частотой дискретизации. Входы и выходы могут выполняться в разное шаги расчета. Используйте положительное целое или 1/N, где N является положительным целым числом. Для примера, если вы вводите 1/2, выходной шаг расчета составляет половину входного шага расчета, или выходы выполняются быстрее. The Full, Empty, и Num сигналы запускаются с более высокой скоростью.

Параметры блоков:

ratio |

| Тип: Вектор символов |

| Значение: Целое число, больше или равное единице |

По умолчанию:

'1' |

Push onto full register - условие переполнения'Warning' (по умолчанию) | 'Ignore' | 'Error'Укажите, как блок должен реагировать при записи в FIFO, который полон. Значение по умолчанию является Warning.

Параметры блоков:

push_msg |

| Тип: Вектор символов |

Значение:

'Warning''Ignore' | 'Error' |

По умолчанию:

'Warning' |

Pop onto empty register - условие нижнего потока'Warning' (по умолчанию) | 'Ignore' | 'Error'Укажите, как блок должен реагировать, когда вы считываете из FIFO, который пуст. Значение по умолчанию является Warning.

Параметры блоков:

pop_msg |

| Тип: Вектор символов |

Значение:

'Warning''Ignore' | 'Error' |

По умолчанию:

'Warning' |

Show empty register indicator port (Empty) - Опциональный пустой портУкажите, включать ли Empty выходной порт. Этот порт выводит 1 когда реестр FIFO пуст и 0 если FIFO содержит одни или несколько вводов данных.

Параметры блоков:

show_empty |

| Тип: Вектор символов |

Значение:

'on''off' |

По умолчанию:

'on' |

Show full register indicator port (Full) - Опциональный полный портУкажите, включать ли Full выходной порт. Этот порт выводит 1 когда реестр FIFO заполнен.

Параметры блоков:

show_full |

| Тип: Вектор символов |

Значение:

'on''off' |

По умолчанию:

'on' |

Show num register indicator port (Num) - Опциональный num портУкажите, включать ли Num выходной порт. Этот порт выводит количество вводов данных, которые в данный момент доступны в очереди FIFO.

Параметры блоков:

show_num |

| Тип: Вектор символов |

Значение:

'on''off' |

По умолчанию:

'on' |

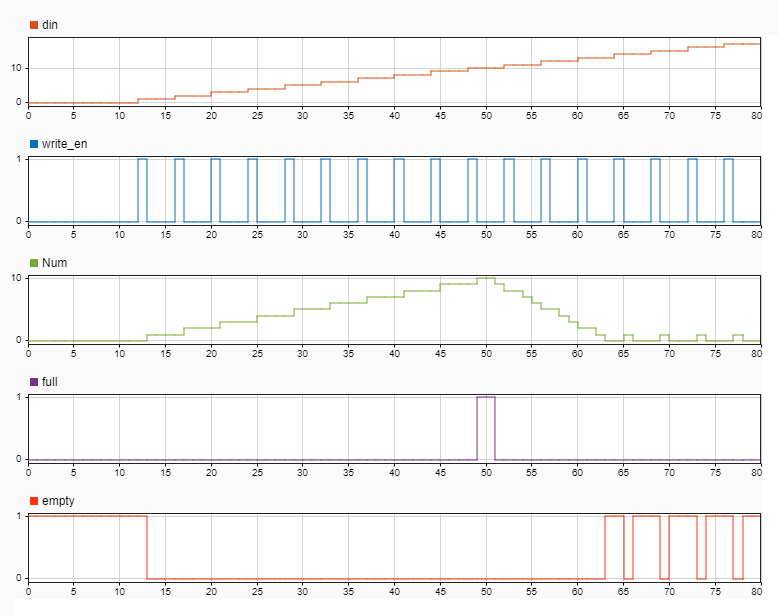

Этот рисунок отображает операцию записи FIFO. Входной порт Push действует как разрешающий сигнал для операции записи. Этот сигнал обозначается сигналом write_en на рисунке.

Когда сигнал write_en 0блок не записывает данные в FIFO и устанавливается флаг empty.

Когда write_en становится 1блок толкает din сигнал во входном порту In к концу регистра FIFO на следующем временном шаге. Сигнал Num указывает количество вводов данных в регистре FIFO. Каждый раз, когда вы записываете данные в FIFO, сигнал Num увеличивается на 1. Во временной шаг 12, write_en есть 1. В следующий временной шаг 13, данные записываются в FIFO. Num шаги сигнала по 1 и флаг empty отменяется.

Этот FIFO использует размер регистра по умолчанию 10. Когда сигнал Num становится равным Register size во временной шаг 49, задан Full сигнал. После того, как сигнал Full станет 1, если вы пытаетесь записать больше записей в FIFO, блок генерирует предупреждение.

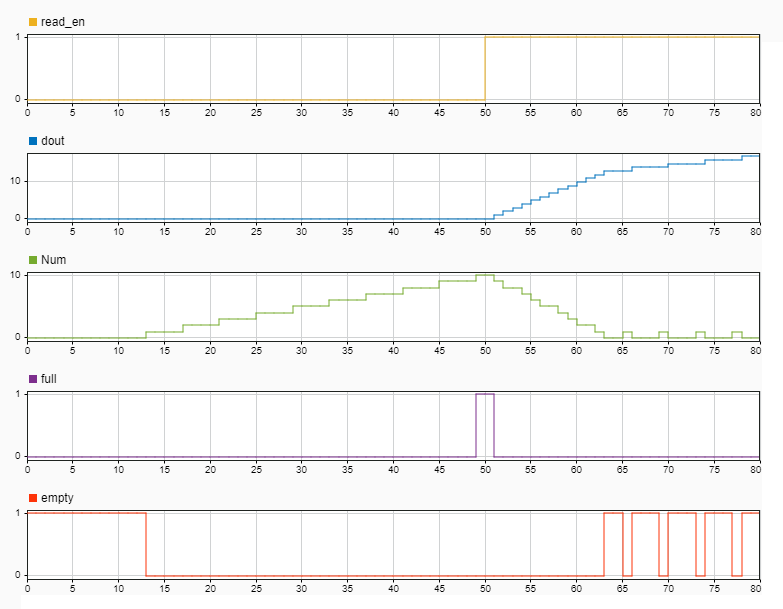

Этот рисунок отображает операцию считывания FIFO. Входной порт Pop действует как разрешающий сигнал для операции считывания. Этот сигнал обозначается сигналом read_en на рисунке.

Когда сигнал read_en 0выходной dout блока 0. Когда сигнал read_en становится 1 в временной шаг 50сигнал dout выводит самую старую запись в FIFO на следующем временном шаге 51. Флаг Full отменяется, и сигнал Num уменьшается на 1 начиная с временного шага 51 при считывании данных из FIFO.

Когда сигнал Num становится равным 0, задан Empty сигнал. После того, как сигнал Empty станет 0, если вы пытаетесь прочитать больше записей из FIFO, блок генерирует предупреждение.

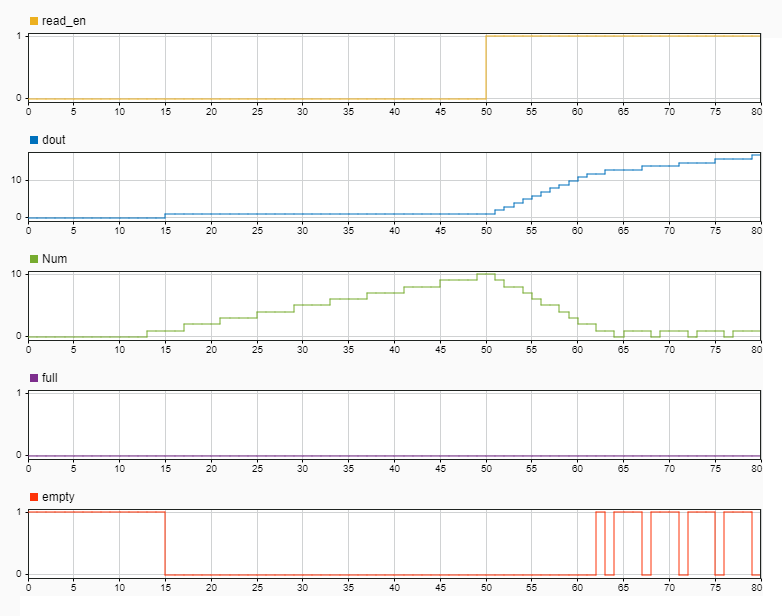

Этот рисунок отображает операцию считывания FIFO. Входной порт Pop действует как разрешающий сигнал для операции считывания. Этот сигнал обозначается сигналом read_en на рисунке.

По умолчанию HDL FIFO работает в Classic режим. Можно также использовать первый режим FWFT для FIFO. В диалоговом окне Параметров блоков задайте Mode следующим образом FWFT.

В FWFT mode, операция записи работает так же, как и Classic режим. The FWFT режим отличается от Classic режим при выполнении операции чтения. В Classic mode, после размещения запроса на чтение или ввода 1 для порта Pop данные становятся доступными на выходе FIFO в следующем такте. В FWFT режим, первое слово, которое вы записываете в FIFO, переходит к выходу и доступно в Out выходного сигнала.

На рисунке, хотя read-en становится 1 в временной шаг 50FIFO считывает первое слово, dout на временном шаге 15. Вы можете использовать эту возможность, чтобы посмотреть вперед и увидеть первое слово, которое было написано в FIFO.

HDL Coder™ предоставляет дополнительные опции строения, которые влияют на реализацию HDL и синтезированную логику.

Этот блок имеет одну архитектуру HDL по умолчанию.

| Общая информация | |

|---|---|

| ConstrainedOutputPipeline | Количество регистров для размещения на выходах путем перемещения существующих задержек в рамках вашего проекта. Распределённая конвейеризация не перераспределяет эти регистры. Значение по умолчанию является |

| InputPipeline | Количество входных этапов конвейера для вставки в сгенерированный код. Распределённая конвейеризация и ограниченная выходная конвейеризация могут перемещать эти регистры. Значение по умолчанию является |

| OutputPipeline | Количество выходных этапов конвейера для вставки в сгенерированный код. Распределённая конвейеризация и ограниченная выходная конвейеризация могут перемещать эти регистры. Значение по умолчанию является |

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.