Вы можете задать пользовательские платы и пользовательские исходные проекты, чтобы они были доступны как целевые аппаратные опции в рабочем процессе SoC. Пользовательские платы и пользовательские исходные проекты используют ту же систему, которую HDL- Coder™ использует для предопределенных плат и исходного проекта целей.

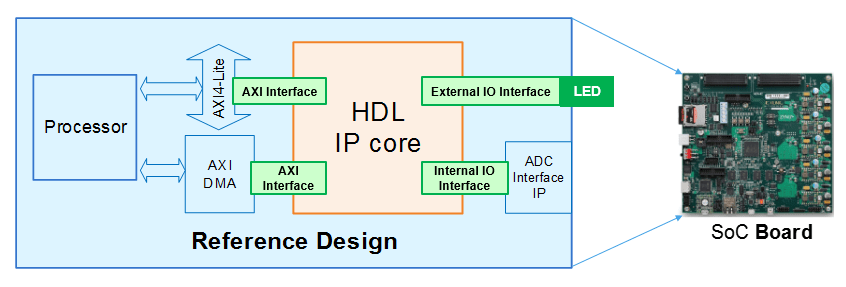

А reference design - это проект встраиваемой системы, с которым интегрируется сгенерированное IP-ядро. Это board платформы SoC.

Для пользовательской платы или пользовательского исходного проекта можно задать различные виды интерфейсов:

Интерфейс AXI: интерфейс между сгенерированным вами IP-ядром и AXI4 или AXI4-Lite интерфейсом.

Внешний интерфейс ввода-вывода: интерфейс между сгенерированным IP-ядром и внешним интерфейсом.

Внутренний интерфейс ввода-вывода: интерфейс между сгенерированным IP-ядром и другим IP-ядром в исходный проект.

После интеграции исходного проекта и IP-ядра в проект разработки встраиваемых систем можно запрограммировать плату с помощью проекта встраиваемых систем.

Чтобы определить и зарегистрировать плату, вы должны иметь board definition, board plugin и board registration file.

Определение платы является файлом, который определяет характеристики платы. Можно задать несколько пользовательских плат.

Плагин платы является папкой пакета, которая содержит:

Определение платы.

Все исходные проекты плагины, которые связаны с платой.

Плагин платы имеет одно определение платы, но может иметь несколько исходные проекты.

Файл регистрации платы всегда называется hdlcoder_board_customization.m, и содержит список плат-плагинов. На MATLAB может быть несколько файлов регистрации плат® путь, но плагин платы не может быть указан в нескольких файлах регистрации платы.

Когда откроется HDL Workflow Advisor, он будет искать файлы с именем по пути MATLAB hdlcoder_board_customization.m, и использует информацию для заполнения опций целевой платы. Интерфейсы, которые вы добавляете и определяете для платы, отображаются как опции в выпадающем списке Target Platform Interface.

Чтобы определить и зарегистрировать исходный проект, вы должны иметь reference design definition, reference design plugin и reference design registration file.

Определение исходного проекта является файлом, который задает характеристики исходного проекта, включая связанную с ним плату и интерфейсы. Можно задать несколько пользовательские исходные проекты для каждой платы.

Плагин для исходного проекта является папкой пакета, которая содержит:

Определение исходного проекта.

Файлы, которые являются частью проекта разработки встраиваемой системы и специфичны для вашего стороннего инструмента синтеза, включая Tcl, проект и файлы проектирования.

Плагин исходного проекта имеет одно определение исходного проекта и связан с одной платой.

Файл регистрации исходного проекта всегда называется hdlcoder_ref_design_customization.m, и содержит список исходного проекта плагинов для определенной платы. На пути MATLAB может быть несколько файлов регистрации исходного проекта для определенной платы, но исходный проект плагин не может быть указан более чем в одном исходном проекте файле регистрации плагина.

Когда откроется HDL Workflow Advisor, он будет искать файлы с именем по пути MATLAB hdlcoder_ref_design_customization.m, и использует информацию для заполнения исходного проекта опций для каждой платы. Интерфейсы, которые вы добавляете и определяете для исходного проекта, появляются как опции в выпадающем списке Target Platform Interface.

Примеры определений рабочих плат и исходных проектов см. в предопределенном Altera® SoC и Xilinx® Zynq® Плашечные плагины, которые включают предопределенные плагины исходного проекта:

support_package_installation_folder/toolbox/hdlcoder/supportpackages/zynq7000/+ZedBoard/

support_package_installation_folder/toolbox/hdlcoder/supportpackages/zynq7000/+ZynqZC702/

support_package_installation_folder/toolbox/hdlcoder/supportpackages/alterasoc/+AlteraCycloneV/

support_package_installation_folder/toolbox/hdlcoder/supportpackages/alterasoc/+ArrowSoCKit/

hdlcoder.Board | hdlcoder.ReferenceDesign