Вы генерируете HTML пользовательский отчет ядра IP по умолчанию, когда вы генерируете пользовательское ядро IP. Отчет описывает поведение и содержимое сгенерированного пользовательского IP-ядра.

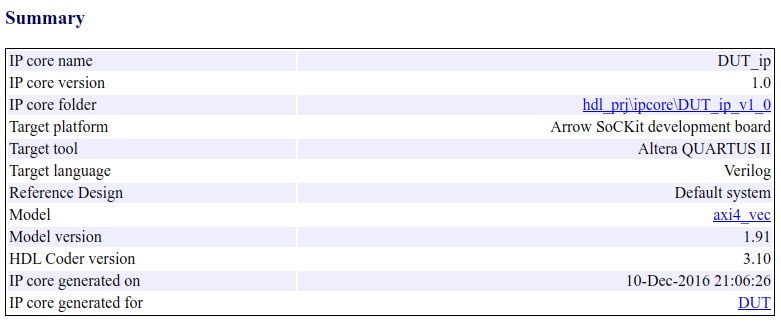

В разделе «Сводка» показаны настройки кодера при создании пользовательского ядра IP.

Следующий рисунок является примером раздела Summary.

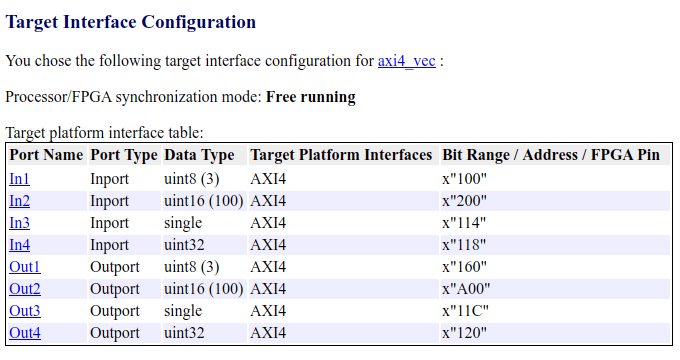

В разделе Target Interface Configuration показано, как порты DUT сопоставляются с интерфейсом целевого компьютера и режимом синхронизации процессор/FPGA.

Следующий рисунок является примером раздела Target Interface Configuration.

Дополнительные сведения о режимах синхронизации процессора/FPGA см. в разделах Синхронизация процессора и FPGA.

Дополнительные сведения об интерфейсах целевой платформы см. в разделе Пользовательские IP- Генерации Core.

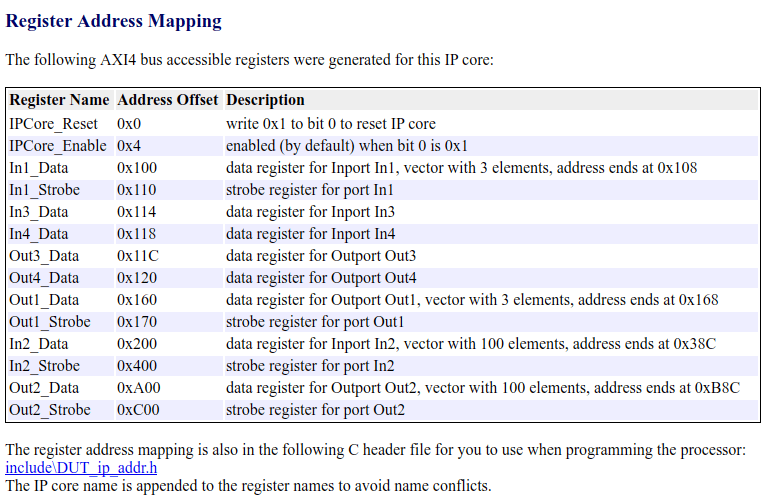

В разделе Register Address Mapping показаны смещения адресов для AXI4-Lite регистров, доступных для шины, в пользовательском IP-ядре и имя файла заголовка C, который содержит те же смещения адресов.

Следующий рисунок является примером раздела Register Address Mapping.

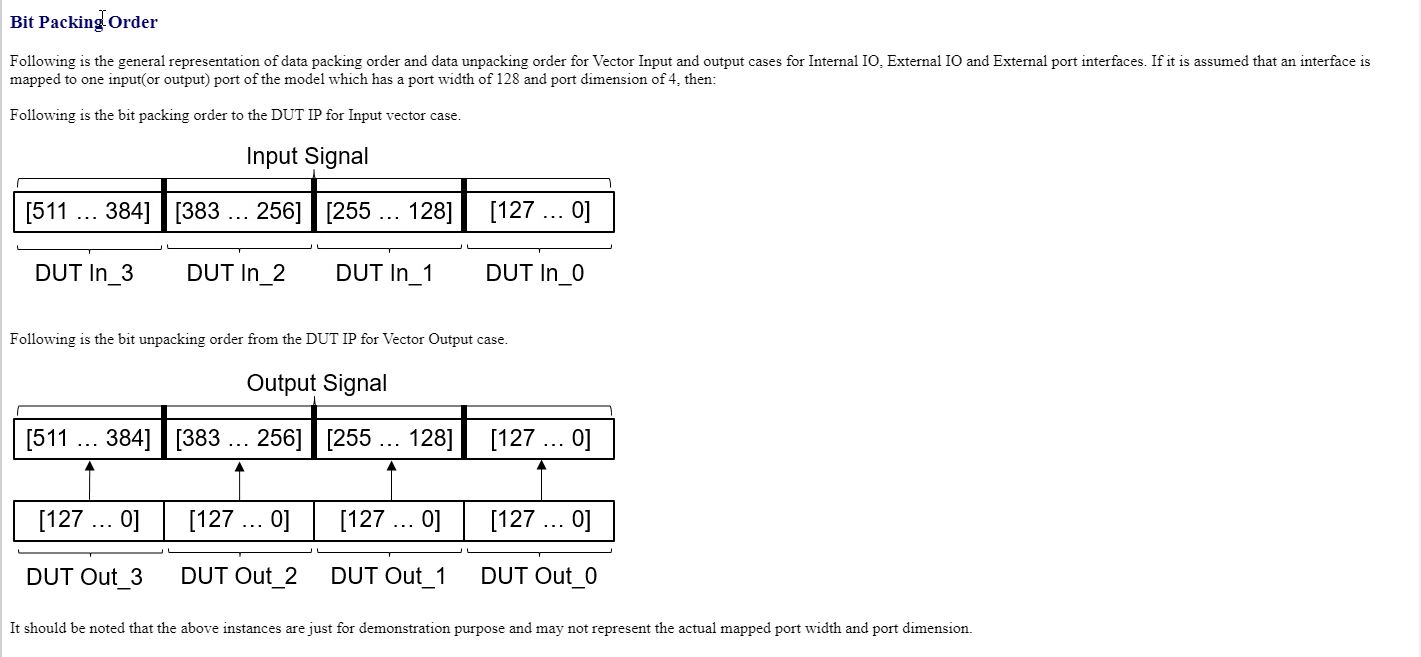

В разделе Bit Packing Order представлен высокоуровневый обзор порядка упаковки данных для векторных входов и выходов для интерфейсов внутреннего ввода-вывода, внешнего ввода-вывода и внешнего порта. Этот раздел появляется только тогда, когда ширина портов внутреннего ввода-вывода, внешнего ввода-вывода и внешнего порта превышает 128 бит в ширину.

Это изображение является примером раздела Bit Packing Order:

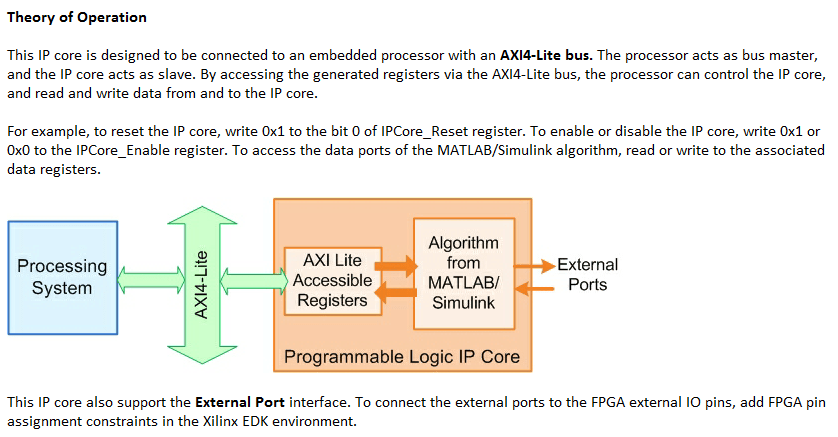

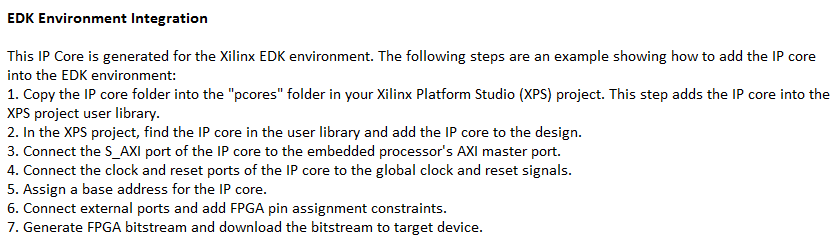

В разделе IP Core User Guide представлен высокоуровневый обзор архитектуры системы, описан режим синхронизации процессора и FPGA, а также приведены инструкции по интеграции IP-ядра в среду интеграции встроенных систем.

Следующий рисунок является примером описания архитектуры системы IP Core User Guide.

Следующий рисунок является примером описания синхронизации процессор/FPGA.

Если вы используете сигналы векторных данных в интерфейсе DUT, отчет ядра IP отображает этот раздел, который показывает, как генератор кода синхронизирует векторные данные через интерфейс AXI4.

Следующий рисунок является примером инструкции для интеграции IP-ядра в вашу встраиваемую систему интегрирования окружения на Xilinx® платформы. Если вы нацелены на Altera® В отчете отображаются аналогичные инструкции по интеграции IP-ядра в окружение Altera Qsys.

В разделе IP Core File List перечислены файлы и папки файлов, которые составляют ваше пользовательское IP-ядро.

Следующий рисунок является примером списка файлов ядра IP.