Используя HDL Workflow Advisor, можно сгенерировать пользовательское IP-ядро из модели или алгоритма. Сгенерированное IP-ядро является шарнирным и многоразовым. Вы можете интегрировать его с большей проект, добавив его в окружение интегрирования встраиваемых систем, такую как Intel® Qsys, Xilinx® EDK или интегратор IP Xilinx.

Чтобы узнать, как сгенерировать пользовательское IP-ядро, смотрите:

Можно сгенерировать IP-ядро:

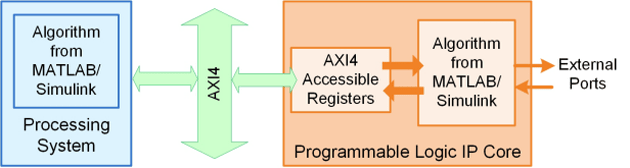

С AXI4 или AXI4-Lite интерфейсом.

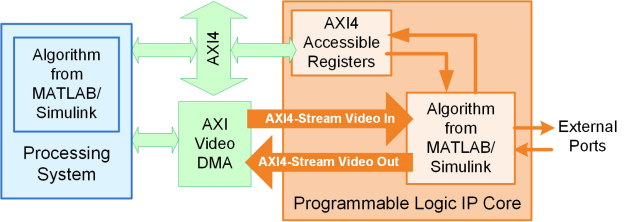

С AXI4 или AXI4-Lite интерфейсом и AXI4-Stream Video интерфейсами.

Без каких-либо AXI4 или AXI4-Lite интерфейсов. Дополнительные сведения см. в разделе Генерация независимого от платы IP-ядра HDL из модели Simulink.

Алгоритм из блока MATLAB/Simulink представляет ваш DUT. HDL Coder™ генерирует остальную часть IP-ядра на основе настроек интерфейса целевой платформы и режима синхронизации процессора/FPGA.

Можно сопоставить каждый порт в DUT с одним из следующих интерфейсов целевой платформы в IP-ядре:

AXI4-Lite: Используйте этот подчиненный интерфейс для регистров управления доступом или для легкой передачи данных. HDL Coder генерирует сопоставленные с памятью регистры и выделяет смещения адреса для портов, которые вы сопоставляете с этим интерфейсом.

AXI4: Используйте этот подчиненный интерфейс для подключения к компонентам, поддерживающим пакетную передачу данных. HDL Coder генерирует сопоставленные с памятью регистры и выделяет смещения адреса для портов, которые вы сопоставляете с этим интерфейсом.

Примечание

Интерфейсы AXI4 и AXI4-Lite также называются AXI4 подчиненными интерфейсами. В сгенерированном IP-ядре HDL можно иметь AXI4 или AXI4-Lite интерфейс, но не оба интерфейса.

AXI4-Stream Video: Используйте этот интерфейс для отправки или получения 32-битного потока скаляра видео данных.

Внешние порты: Используйте внешние порты для подключения к внешним контактам ввода-вывода FPGA или к другим IP-ядрам с внешними портами.

FPGA Данных Capture - JTAG: Используйте FPGA Данных Capture через интерфейс JTAG для наблюдения тестовой точки сигналов и сигналов в портах DUT выхода в то время как ваш проект запусков на FPGA. Пример маркировки внутренних сигналов в качестве тестовых точек см. в Debug IP Core Using FPGA Data Capture. Дополнительные сведения о сборе данных см. в разделе Рабочий процесс захвата данных (HDL Verifier).

Примечание

Чтобы использовать этот интерфейс, необходимо загрузить пакет аппаратной поддержки для вашей платы FPGA. См. раздел Загрузка пакета поддержки платы FPGA (HDL Verifier).

Дополнительные сведения о AXI4, AXI4-Lite и AXI4-Stream Video протоколах см. в документации по целевому компьютеру.

HDL Coder генерирует логику синхронизации в IP-ядре на основе выбранного режима синхронизации процессор/FPGA.

При генерации пользовательского IP-ядра доступны следующие опции синхронизации процессор/FPGA:

Free running (по умолчанию)

Coprocessing – blocking

Дополнительные сведения о режимах синхронизации процессора/FPGA см. в разделах «Синхронизация процессора и FPGA».

После того, как вы сгенерируете пользовательское IP-ядро, файлы IP-ядра находятся в ipcore папка в папке проекта. В HDL Workflow Advisor можно просмотреть имя основной IP-папки в IP core folder поле задачи HDL Code Generation > Generate RTL Code and IP Core.

Папка IP-ядра содержит следующие сгенерированные файлы:

Файлы определения ядра IP.

Исходные файлы HDL (.vhd или .v).

Файл заголовка C с адресной картой регистра.

(Необязательно) HTML с инструкциями по использованию ядра и интеграции IP-ядра во встроенный системный проект.

IP Core Generation рабочий процесс не поддерживает:

RAM Architecture установлено на Generic RAM without clock enable.

Использование различных синхроимпульсов для ядра IP и интерфейса AXI. The IPCore_Clk и AXILite_ACLK должен быть синхронным и подключен к одному и тому же источнику синхроимпульса. The IPCore_RESETN и AXILite_ARESETN должен быть подключен к тому же источнику сброса. См. «Синхронизация сигнала глобального сброса с тактовой Областью IP Core».