Этот раздел содержит параметры на панели HDL Code Generation > Floating Point диалогового окна Параметров конфигурации. Используйте эти параметры, чтобы задать стратегию задержки, цель и необходимость инициализации регистров конвейера в целевом IP с плавающей точкой до нуля.

Вставляет дополнительную логику во время генерации HDL-кода, чтобы инициализировать значения регистров конвейера в Altera® конечный IP с плавающей точкой в нуле. Если этот флажок не установлен, HDL- Coder™ сообщает предупреждение во время генерации HDL-кода.

По умолчанию: On

Вставляет дополнительную логику, чтобы инициализировать регистры конвейера в целевом IP с плавающей точкой в нуле.

Не добавляет дополнительную логику для инициализации регистров конвейера в целевом IP с плавающей точкой в нуль.

Чтобы задать этот параметр, установите Floating Point IP Library равным Altera Megafunctions (ALTERA FP FUNCTIONS). Прежде чем вы задаете библиотеку с плавающей точкой, задайте путь к инструменту синтеза с помощью hdlsetuptoolpath функция.

Чтобы задать эту настройку:

Создайте целевой объект строения с плавающей точкой с Altera Megafunctions (ALTERA FP FUNCTIONS) как целевую библиотеку с плавающей точкой.

fpconfig = hdlcoder.createFloatingPointTargetConfig('AlteraFPFunctions');Задайте InitializeIPPipelinesToZero свойство LibrarySettings атрибут целевого объекта строения с плавающей точкой.

fpconfig.LibrarySettings.InitializeIPPipelinesToZero = 0;

Установите целевое строение с плавающей точкой в модели и затем сгенерируйте HDL-код. В этом примере показов, как установить строение на sfir_single Модель и сгенерируйте HDL-код для symmetric_fir подсистема:

hdlset_param('sfir_single','FloatingPointTargetConfig',fpconfig)

makehdl('sfir_single/symmetric_fir')

Укажите, хотите ли вы, чтобы проект сопоставил минимальную или максимальную задержку с Xilinx® LogiCORE или ALTFP Altera megafunction IPs.

По умолчанию:

MIN

Опции:

MINПреобразуется в минимальную задержку для заданного целевого IP с плавающей точкой.

MAXПреобразуется в максимальную задержку для заданного целевого IP с плавающей точкой.

Чтобы задать этот параметр, установите Floating Point IP Library равным Altera Megafunctions (ALTFP) или Xilinx LogiCORE. Прежде чем вы задаете библиотеку с плавающей точкой, задайте путь к инструменту синтеза с помощью hdlsetuptoolpath функция.

Чтобы задать эту настройку:

Создайте целевой объект строения с плавающей точкой с Altera Megafunctions (ALTERA FP FUNCTIONS) как целевую библиотеку с плавающей точкой.

fpconfig = hdlcoder.createFloatingPointTargetConfig('ALTFP');Задайте LatencyStrategy свойство LibrarySettings атрибут целевого объекта строения с плавающей точкой.

fpconfig.LibrarySettings.LatencyStrategy = 'MAX';

Установите целевое строение с плавающей точкой в модели и затем сгенерируйте HDL-код. В этом примере показов, как установить строение на sfir_single Модель и сгенерируйте HDL-код для symmetric_fir подсистема:

hdlset_param('sfir_single','FloatingPointTargetConfig',fpconfig)

makehdl('sfir_single/symmetric_fir')

Укажите, нужно ли оптимизировать проект для скорости или площади при сопоставлении с целевыми библиотеками с плавающей точкой.

По умолчанию:

SPEED

Опции:

NONEВыберите эту опцию, если вы не хотите оптимизировать проект для скорости или площади.

SPEEDВыберите эту опцию, чтобы оптимизировать проект для скорости.

AREAВыберите эту опцию, чтобы оптимизировать проект для области.

Чтобы задать этот параметр, установите Floating Point IP Library равным Altera Megafunctions (ALTFP) или Xilinx LogiCORE. Прежде чем вы задаете библиотеку с плавающей точкой, задайте путь к инструменту синтеза с помощью hdlsetuptoolpath функция.

Чтобы задать эту настройку:

Создайте целевой объект строения с плавающей точкой с Altera Megafunctions (ALTERA FP FUNCTIONS) как целевую библиотеку с плавающей точкой.

fpconfig = hdlcoder.createFloatingPointTargetConfig('ALTFP');Задайте Objective свойство LibrarySettings атрибут целевого объекта строения с плавающей точкой.

fpconfig.LibrarySettings.Objective = 'AREA';

Установите целевое строение с плавающей точкой в модели и затем сгенерируйте HDL-код. В этом примере показов, как установить строение на sfir_single Модель и сгенерируйте HDL-код для symmetric_fir подсистема:

hdlset_param('sfir_single','FloatingPointTargetConfig',fpconfig)

makehdl('sfir_single/symmetric_fir')

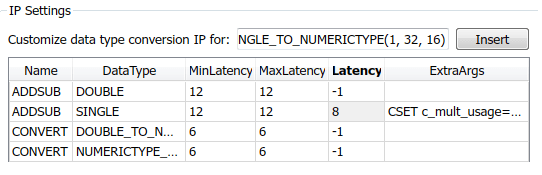

Раздел IP Settings имеет таблицу строения IP с именами IP и типами данных и дополнительные опции для определения пользовательской задержки и любых дополнительных аргументов.

Опции в таблице строения IP зависят от заданной библиотеки.

Если вы задаете ALTERA MEGAFUNCTION (ALTERA FP FUNCTIONS) library, HDL Coder выводит значение задержки из Target Frequency (MHz) значения.

Если вы задаете ALTERA MEGAFUNCTION (ALTFP) или XILINX LOGICORE libraries, HDL Coder выводит задержку IP из Latency Strategy параметра. Таблица строения IP имеет два дополнительных столбца, MinLatency и MaxLatency, которые содержат минимальное и максимальное значения задержки для каждого IP в таблице.

Таблица строения IP содержит следующие разделы:

Name: Содержит список IP- имен, которые HDL Coder сопоставляет с Simulink® блоки, к, такие как ABS, ADDSUB, и CONVERT.

DataType: Содержит список типов данных IP для каждого IP в таблице. В основном это SINGLE и DOUBLE типы данных. The CONVERT Блоки IP могут иметь DOUBLE_TO_NUMERICTYPE, NUMERICTYPE_TO_DOUBLE типы данных и так далее.

Latency: Значение задержки по умолчанию –1 означает, что IP наследует значение задержки от целевой частоты или параметра стратегии задержки в зависимости от выбранной библиотеки. Чтобы настроить задержку IP, с которой сопоставлены ваши блоки Simulink, введите собственное пользовательское значение задержки.

ExtraArgs: Задайте любые дополнительные параметры, характерные для IP.

Например, если у вас есть Add блок с Single типы данных в модели Simulink, HDL Coder сопоставляет блок с ADDSUB IP. Если вы хотите задать пользовательское значение задержки, например 8, для IP, введите значение в столбце Latency для IP.

cmultusage является параметром, который можно задать с помощью Xilinx LogiCORE® библиотеки.

Чтобы задать этот параметр, установите Floating Point IP Library равным Altera Megafunctions (ALTFP) или Xilinx LogiCORE. Прежде чем вы задаете библиотеку с плавающей точкой, задайте путь к инструменту синтеза с помощью hdlsetuptoolpath функция.

Чтобы задать эту настройку:

Создайте целевой объект строения с плавающей точкой с Altera Megafunctions (ALTERA FP FUNCTIONS) как целевую библиотеку с плавающей точкой.

fpconfig = hdlcoder.createFloatingPointTargetConfig('ALTFP');Чтобы просмотреть строение IP с плавающей точкой, используйте IPConfig объект.

fpconfig.IPConfig

Чтобы настроить задержку или задать дополнительные аргументы, используйте customize способ.

fpconfig.IPConfig.customize('ADDSUB','Single','Latency',6);Установите целевое строение с плавающей точкой в модели и затем сгенерируйте HDL-код. В этом примере показов, как установить строение на sfir_single Модель и сгенерируйте HDL-код для symmetric_fir подсистема:

hdlset_param('sfir_single','FloatingPointTargetConfig',fpconfig)

makehdl('sfir_single/symmetric_fir')