Сопоставление с библиотекой с плавающей точкой позволяет вам синтезировать проект с плавающей точкой, не делая преобразования из плавающей запятой в фиксированную запятую. Исключение шага преобразования из плавающей запятой в фиксированную запятую уменьшает потерю точности данных и позволяет моделировать более широкую динамическую область значений.

Библиотека с плавающей точкой FPGA является набором IP- блоков с плавающей точкой, которые оптимизированы для синтеза на конкретных целевых компьютерах. Altera® Мегафункции и Xilinx® LogiCORE IP являются примерами таких библиотек.

В библиотеке HDL Coder™ блоков - подмножество Simulink® блоки поддерживают отображение библиотек с плавающей точкой. Смотрите HDL Coder поддержка библиотечных Отображений FPGA с плавающей точкой.

Чтобы сопоставить ваш проект с плавающей точкой с библиотекой Altera или Xilinx FPGA с плавающей точкой:

Установите опции целевого устройства для инструмента синтеза Altera или Xilinx FPGA с помощью hdlset_param. Для примера установите инструмент синтеза следующим Altera Quartus II и семейство чипов как Arria10:

hdlset_param(model,'SynthesisToolChipFamily','Arria10', ... 'SynthesisToolDeviceName','10AS066H2F34E1SG', ... 'SynthesisToolPackageName','', ... 'SynthesisToolSpeedValue','')

Чтобы настроить путь к исполняемому файлу инструмента синтеза, используйте hdlsetuptoolpath. Например, чтобы задать путь к Altera Quartus II инструмент синтеза:

hdlsetuptoolpath('ToolName','Altera Quartus II','ToolPath',... 'C:\altera\14.0\quartus\bin\quartus.exe');

См. Раздел «Setup пути инструмента синтеза».

Настройте библиотеки симуляции Altera или Xilinx FPGA с плавающей точкой. См. раздел Setup библиотеки симуляцию FPGA.

Можно сопоставить модель Simulink с целевыми библиотеками с плавающей точкой из диалогового окна Параметры конфигурации или из командной строки.

Для сопоставления с библиотекой с плавающей точкой FPGA:

На вкладке Apps выберите HDL Coder. Появится вкладка HDL Code. Нажмите Settings.

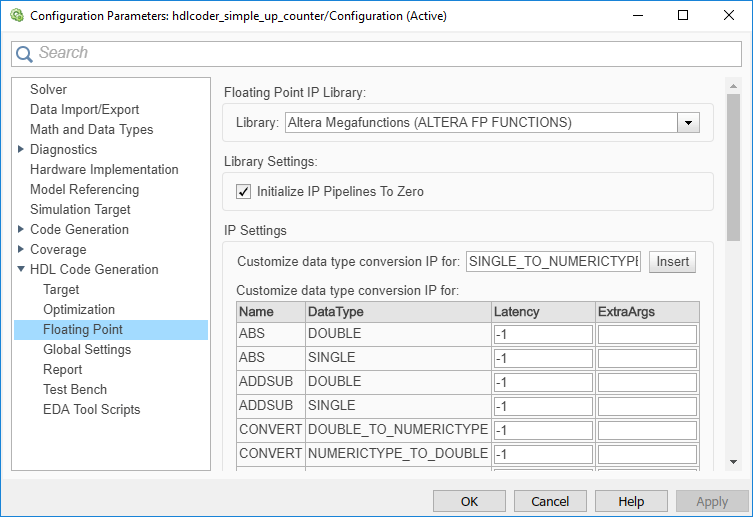

На панели HDL Code Generation > Floating Point Target выберите библиотеку IP с плавающей точкой.

Для Xilinx LogiCORE® IP, выберите XILINX LOGICORE в качестве библиотеки. Для Altera megafunction IP можно выбрать ALTERA MEGAFUNCTION (ALTFP) или ALTERA MEGAFUNCTION (ALTERA FP FUNCTIONS) в качестве библиотеки.

Если вы выбираете ALTERA MEGAFUNCTION (ALTERA FP FUNCTIONS) в качестве библиотеки, становится доступным опция Initialize IP Pipelines to Zero. Выберите опцию Initialize IP Pipelines to Zero, чтобы инициализировать регистры конвейера в IP до нуля. На панели Target and Optimizations введите целевую частоту, на которую должен соответствовать IP с плавающей точкой.

Примечание

При сопоставлении с ALTERA FP FUNCTIONS целевой язык должен быть установлен на VHDL.

Когда вы выбираете ALTERA FP FUNCTIONS отобразится таблица Строение. Используя таблицу типов данных, можно настроить параметры IP целевой библиотеки с плавающей точкой. Для получения дополнительной информации смотрите Настройка задержки IP с целевой частотой.

Если вы выбираете XILINX LOGICORE или ALTERA MEGAFUNCTION (ALTFP) в качестве библиотеки, выберите Latency Strategy и Objective для IP.

При выборе этих библиотек появляется таблица Строение. При помощи таблицы типов данных можно настроить задержку целевого IP с плавающей точкой. Для получения дополнительной информации смотрите Настройка задержки IP со стратегией задержки.

Чтобы совместно использовать IP-ресурсы с плавающей точкой, на вкладке HDL Code Generation Target and Optimizations > Resource Sharing, убедитесь, что Floating-point IPs включена. Количество IP- блоков с плавающей точкой, которые получают общий доступ, зависит от SharingFactor, которую вы задаете в подсистеме.

Нажмите Apply. На панели инструментов Simulink Toolstrip нажмите Generate HDL Code.

Чтобы сгенерировать HDL-код из командной строки, можно использовать hdlcoder.createFloatingPointTargetConfig функция для создания IP- строения с плавающей точкой.

При помощи hdlcoder.createFloatingPointTargetConfig function, создать hdlcoder.FloatingPointTargetConfig объект для библиотеки с плавающей точкой. Затем используйте hdlset_param для сохранения строения в модели.

Например, чтобы создать целевое строение с плавающей точкой для ALTERA FP FUNCTIONS библиотека с настройками по умолчанию:

fpconfig = hdlcoder.createFloatingPointTargetConfig('ALTERAFPFUNCTIONS');

hdlset_param('sfir_single', 'FloatingPointTargetConfiguration', fpconfig);Параметры IP можно настроить на основе заданной библиотеки с плавающей точкой. Для получения дополнительной информации см. раздел «Настройка IP- Строения с плавающей точкой».

Использовать makehdl для генерации HDL-кода из подсистемы.

Чтобы просмотреть отчеты генерации кода отображения библиотеки с плавающей точкой, прежде чем вы начнете генерацию кода, включите генерацию Отчета об использовании ресурсов и Отчета об оптимизации. Чтобы узнать, как создавать эти отчеты, см. раздел Создание и использование отчетов генерации кода.

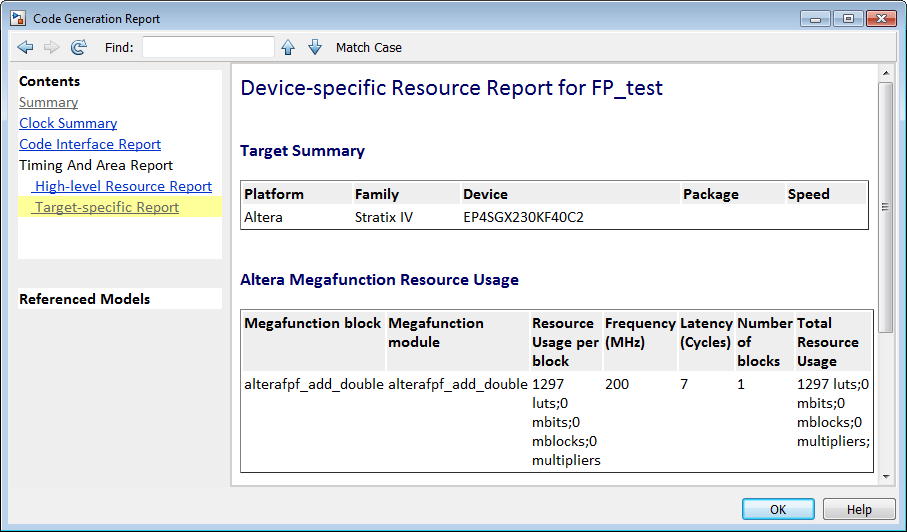

Чтобы увидеть целевой блок с плавающей точкой, к которому сопоставлен ваш проект, задержку и количество аппаратных ресурсов для целевого устройства, в отчете генерации кода, выберите Target-specific Report.

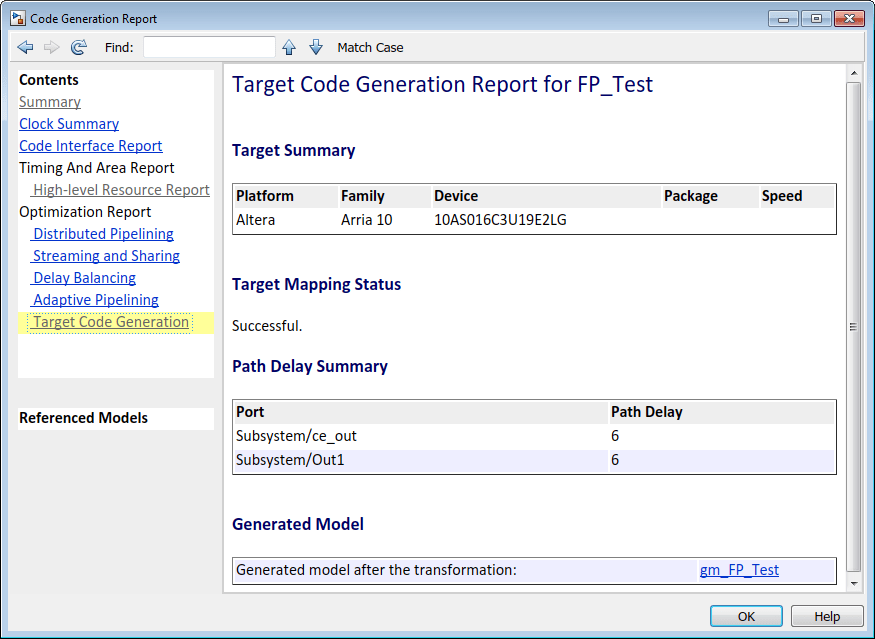

В отчете о генерации кода в разделе Target Code Generation отчета об оптимизации показан статус настроек оптимизации, примененных к модели. Отчет показывает, успешно ли HDL Coder сгенерировал целевой код с плавающей точкой.

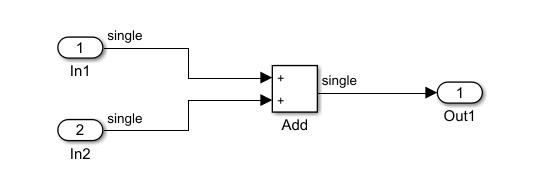

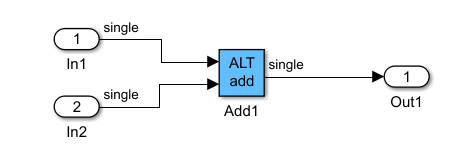

Можно получить информацию о задержках целевого IP с плавающей точкой из сгенерированной модели после генерации HDL-кода. Например, рассмотрите этот блок добавления в Simulink с входами двойного типа данных.

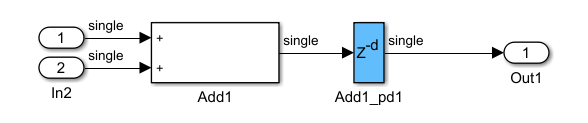

После генерации HDL-кода в отчете об оптимизации для генерации целевого кода отображается ссылка на сгенерированную модель. Чтобы увидеть целевую библиотеку с плавающей точкой, которую сопоставил блок Simulink, дважды кликните подсистему в сгенерированной модели.

Дважды кликните блок добавления ALT. Длина блока задержки является задержкой целевого IP с плавающей точкой.

Чтобы узнать больше о сгенерированной модели, см. Сгенерированные Модель и Модель Валидации.

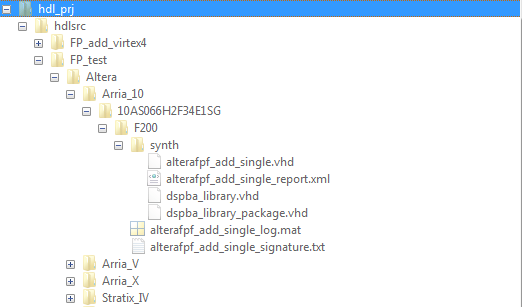

Чтобы увидеть результаты сопоставления библиотек с плавающей точкой FPGA, можно просмотреть файлы ядра IP, сгенерированные после генерации HDL-кода.

HDL Coder проверяет и повторно использует существующие сгенерированные файлы IP-ядра, занимая меньше времени при последовательной генерации кода для того же целевого IP с плавающей точкой.