Для выполнения легкой передачи данных или для регистров управления доступом используйте AXI4 ведомых интерфейсов. Ведомые интерфейсы AXI4 включают интерфейсы AXI4 и AXI4-Lite. С помощью программного обеспечения HDL Coder™ вы не должны реализовывать AXI4 или AXI4-Lite протокол в своей модели. Программное обеспечение генерирует AXI4 или AXI4-Lite интерфейсов в IP-ядре HDL.

Когда вы моделируете свой проект, задайте порты данных, вы хотите сопоставить с AXI4 ведомыми интерфейсами. Затем HDL Coder сопоставляет порты данных с регистрами, сопоставленными с памятью, и распределяет смещения адресов для портов.

Когда вы сопоставляете ваши порты DUT с AXI4 или AXI4-Lite интерфейсами:

Можно сопоставить все скалярные, векторные или шинные порты в проекте с AXI4 или AXI4-Lite интерфейсами.

Вы не можете сопоставить некоторые порты DUT с AXI4 интерфейсами и другими портами DUT с AXI4-Lite интерфейсами для того же проекта.

Когда вы используете скалярные типы данных в портах интерфейса DUT, можно непосредственно сопоставить порты интерфейса с AXI4 или AXI4-Lite интерфейсами. Генератор кода присваивает уникальный адрес каждому порту данных, который вы хотите сопоставить с AXI4 интерфейсом.

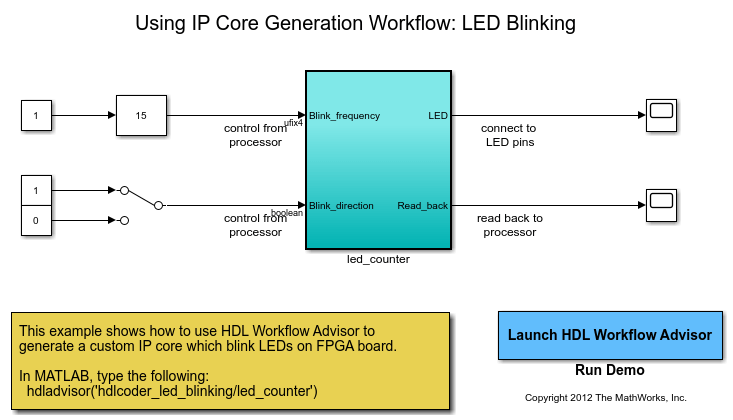

Для примера, который показывает, как сопоставить скалярные порты с AXI4-Lite интерфейсами, откройте модель hdlcoder_led_blinking.

open_system('hdlcoder_led_blinking')

В этой модели подсистема led_counter является оборудование подсистемой. Он моделирует счетчик, который мигает светодиодами на плате FPGA. Два входных порта, Blink_frequency и Blink_direction, являются портами управления, которые определяют частоту и направление мигания светодиода. Все блоки за пределами подсистемы led_counter предназначены для реализации программного обеспечения.

В Simulink®можно использовать Slider Gain блок или Manual Switch блок, чтобы настроить входные значения аппаратной подсистемы. Процессор ARM управляет сгенерированным IP-ядром путем записи в регистры AXI-интерфейса, доступные во встроенном ПО. Порт выхода аппаратной подсистемы соединяется с оборудованием LED. Можно использовать выход порт Read_back для чтения данных обратно на процессор.

Когда вы запускаете IP Core Generation рабочий процесс, в Set Target Interface задаче вы видите, что порты Blink_frequency, Blink_direction, и Read_back сопоставить с AXI4-Lite интерфейсами.

Чтобы узнать больше об этом примере, смотрите:

Когда вы используете типы векторных данных в портах интерфейса DUT, можно непосредственно сопоставить порты интерфейса с AXI4 или AXI4-Lite интерфейсами. Генератор кода присваивает уникальный адрес для каждого порта данных, который вы хотите сопоставить с AXI4 интерфейсом.

Когда вы сопоставляете порты векторов, HDL Coder использует дополнительные регистры строба для каждого порта, чтобы поддерживать синхронизацию с логикой IP- основного алгоритма. Для входа портов регистры strobe управляют разрешающими сигналами для набора теневых регистров, что делает логику IP- основного алгоритма видящей обновленные векторные элементы одновременно. Для выходных портов регистры strobe гарантируют, что считываемые векторные данные регистрируются синхронно.

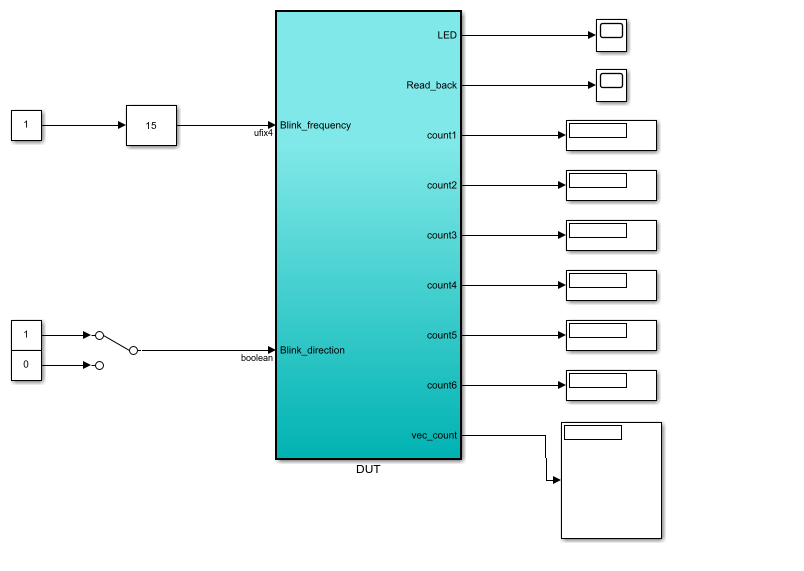

Для примера, который показывает, как сопоставить векторные порты с AXI4-Lite интерфейсами, откройте модель hdlcoder_led_vector.

open_system('hdlcoder_led_vector')

В этой модели подсистема DUT реализует алгоритм LED-мигания и имеет векторные выходные порты. Когда вы запускаете IP Core Generation рабочий процесс, вы видите, что входные и выходные порты сопоставлены с AXI4-Lite интерфейсами в Set Target Interface задаче.

Для получения дополнительной информации смотрите рабочий процесс генерации IP-ядра с процессором MicroBlaze: Xilinx Kintex-7 KC705.

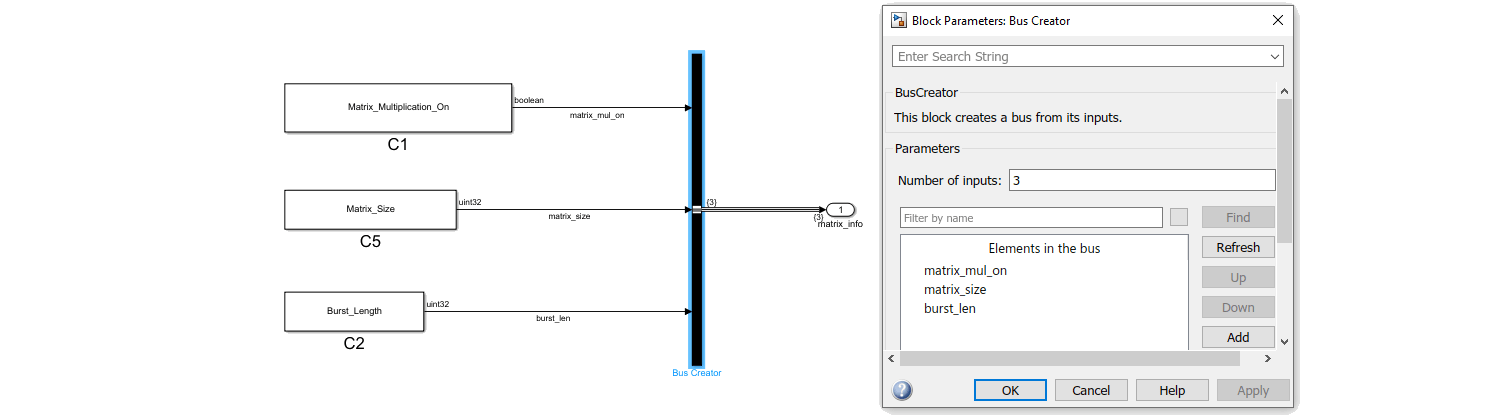

Когда вы используете типы данных шины в портах интерфейса DUT, можно непосредственно сопоставить порты интерфейса с AXI4 или AXI4-Lite интерфейсами.

Когда вы сопоставляете типы данных шины, HDL Coder присваивает уникальный адрес для каждого порта данных, который вы хотите сопоставить с AXI4 интерфейсом. Шины верхнего и подуровня не имеют адреса смещения регистра. Отображение адресов для отдельных скалярных или векторных элементов шины не смежно.

Моделируйте элемент шины с помощью блока создателя шины или блока элемента шины, чтобы создать порт шины.

Моделируйте элемент шины с помощью блока создателя шины.

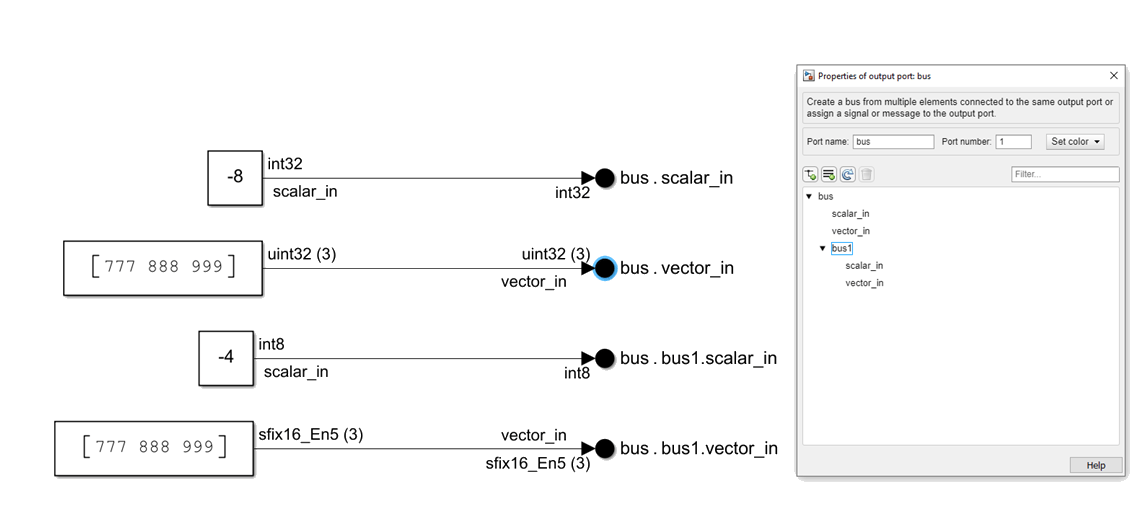

Моделируйте элемент шины с помощью блоков элемента шины:

Для получения дополнительной информации см. раздел «Сопоставить типы данных шины с AXI4 подчиненных интерфейсов».

Когда вы запускаете IP Core Generation рабочий процесс или Simulink Real-Time FPGA I/O рабочий процесс, можно задать начальное значение для входных портов, сопоставленных с AXI4 ведомыми регистрами. Вы можете задать начальное значение при сопоставлении с этими целевыми интерфейсами:

AXI4

AXI4-Lite

PCIe

По умолчанию начальное значение равно нулю. Чтобы задать ненулевое значение:

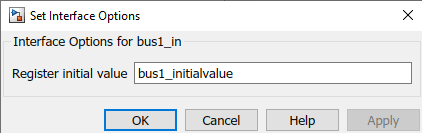

В таблице интерфейса целевой платформы, когда вы сопоставляете входной порт DUT с AXI4 подчиненным интерфейсом, в столбце Interface Options появляется кнопка Options.

Нажмите кнопку Options, а затем укажите RegisterInitialValue.

Заданное значение сохраняется в блоках Inport DUT как свойство HDL-блока, IOInterfaceOptions на вкладке Target Specification. Например, если вы сопоставили входной порт DUT с AXI4-Lite интерфейсом, установите RegisterInitialValue на 5, а затем запустите Set Target Interface задачу. Свойство IOInterfaceOptions этого входного порта сохраняется со значением {'RegisterInitialValue','5'}.

Чтобы просмотреть IOInterfaceOptions значение, если полный путь к порту DUT hdlcoder_led_blinking/led_counter/LED, введите:

hdlget_param('hdlcoder_led_blinking/led_counter/LED',... 'IOInterfaceOptions')

Задайте начальное значение для скалярных портов.

hdlset_param('hdlcoder_led_blinking/led_counter/LED', ... 'IOInterfaceOptions', {'RegisterInitialValue','5'});

Чтобы задать начальное значение для шины, задайте struct, имена полей которой совпадают с именами элементов шины. Для примера,

Можно также задать начальное значение с помощью переменной, определенной в MATLAB® рабочей области. Для примера:

bus1_initialvalue = struct('scalar_in1',1,'scalar_in2',2,'scalar_in3',3,'scalar_in4',4,'vector_in',[1 3])

Когда вы запускаете IP Core Generation рабочий процесс, можно считать назад значение, которое записывается в AXI4 ведомые регистры с помощью AXI4 ведомого интерфейса. Например, можно считать назад значения, которые записываются в AXI4 ведомые регистры при помощи devmem команда в консоли Linux процессора ARM. Если установлены HDL Verifier™, можно использовать MATLAB как AXI Master IP для чтения значений.

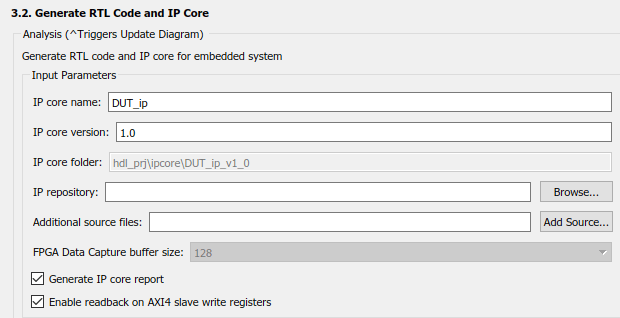

Чтобы использовать эту возможность, в Generate RTL Code and IP Core задаче IP Core Generation рабочий процесс, установите флажок Enable read back on AXI4 slave write registers, а затем запустите Generate RTL Code and IP Core задачу

Когда вы запускаете эту задачу, HDL Coder сохраняет настройку read back, которая была включена в модели. В HDL Block Properties Подсистемы DUT, в IP Core Parameter разделе вкладки Target Specification, вы видите параметр, AXI4RegisterReadback установлено на on. Если вы экспортируете запуск HDL Workflow Advisor в скрипт, вы видите эту настройку, сохраненную в модели при помощи hdlset_param.

hdlset_param('hdlcoder_led_vector/DUT', 'AXI4RegisterReadback', 'on');

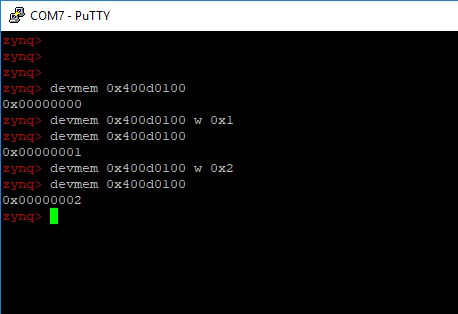

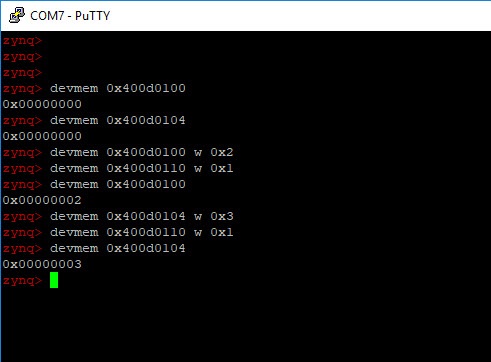

Эти примеры показывают, как вы можете считать значения назад с помощью devmem команда в консоли Linux с такой программой, как PuTTy™.

Чтобы считать значения при сопоставлении скалярных портов с AXI4 интерфейсами, вы сначала записываете значения в регистры AXI4, а затем считываете значения. Адрес памяти регистров AXI4 можно увидеть в отчете Генерация ядра IP.

Чтобы считать значения при сопоставлении портов векторов с AXI4 интерфейсами, вы сначала записываете в регистры AXI4, затем записываете адрес регистра строба в 0x1, а затем считайте значения. Адрес памяти регистров AXI4 и стробирующего регистра можно увидеть в отчете IP Core Generation.

Когда ваша модель содержит несколько выходных регистров, и вы хотите считать обратно данные из нескольких AXI4 ведомых регистров, логика read back становится длинной мультиплексорной цепью, которая может уменьшить частоту синтеза. Если вы выбираете параметр Enable readback on AXI4 slave write register в задании Generate RTL Code and IP Core, HDL Coder добавляет mux для каждого AXI4 регистра в логике Address Decoder. Когда количество AXI4 ведомых регистров увеличивается, мультиплексорная цепь становится больше, что дополнительно уменьшает частоту синтеза.

Можно оптимизировать логику readback и достичь целевой частоты, которую вы хотите. Когда вы запускаете IP Core Generation рабочий процесс, в Generate RTL Code and IP Core задаче вы видите настройку AX4 slave port to pipeline register ratio. Значение по умолчанию этой настройки auto. Этот параметр указывает AXI4 сколько ведомых регистров вставлен регистр трубопровода. Для примера - AX4 slave port to pipeline register ratio 20 означает, что один регистр трубопровода вставляется для каждого 20 Ведомые регистры AXI. The auto установка означает, что генератор кода вставляет определенное количество трубопроводов для AXI4 ведомых портов в зависимости от количества портов и заданного инструмента синтеза. Можно отключить эту настройку или выбрать число между 5 и 50 для этого соотношения.

Когда вы запускаете эту задачу, HDL Coder сохраняет значение, заданное для настройки в модели. В HDL Block Properties Подсистемы DUT, в IP Core Parameter разделе вкладки Target Specification, вы видите параметр, AX4SlavePortToPipelineRegisterRatio установить на заданное значение. Если вы экспортируете запуск HDL Workflow Advisor в скрипт, вы видите эту настройку, сохраненную в модели при помощи hdlset_param.

hdlset_param('hdlcoder_led_vector/DUT', ... 'AXI4SlavePortToPipelineRegisterRatio', '20');