Кодер включает блок комментария заголовка в верхней части файлов, которые он генерирует. Блок комментария заголовка содержит спецификации генерирующего фильтра и опции кодера, которые были выбраны во время генерации HDL-кода.

Можно использовать опцию Comment in header, чтобы добавить комментарий в конец блока комментариев заголовка в каждом сгенерированном файле. Для примера используйте эту опцию, чтобы добавить "This module was automatically generated”. С этим изменением предыдущий блок комментария заголовка появится следующим образом:

-- ------------------------------------------------------------- -- -- Module: Hlp -- -- Generated by MATLAB(R) 7.11 and the Filter Design HDL Coder 2.7. -- -- Generated on: 2010-08-31 13:32:16 -- -- This module was automatically generated -- -- ------------------------------------------------------------- -- ------------------------------------------------------------- -- HDL Code Generation Options: -- -- TargetLanguage: VHDL -- Name: Hlp -- UserComment: User data, length 47 -- Filter Specifications: -- -- Sampling Frequency : N/A (normalized frequency) -- Response : Lowpass -- Specification : Fp,Fst,Ap,Ast -- Passband Edge : 0.45 -- Stopband Edge : 0.55 -- Passband Ripple : 1 dB -- Stopband Atten. : 60 dB -- ------------------------------------------------------------- -- ------------------------------------------------------------- -- HDL Implementation : Fully parallel -- Multipliers : 43 -- Folding Factor : 1 -- ------------------------------------------------------------- -- Filter Settings: -- -- Discrete-Time FIR Filter (real) -- ------------------------------- -- Filter Structure : Direct-Form FIR -- Filter Length : 43 -- Stable : Yes -- Linear Phase : Yes (Type 1) -- Arithmetic : fixed -- Numerator : s16,16 -> [-5.000000e-001 5.000000e-001) -- Input : s16,15 -> [-1 1) -- Filter Internals : Full Precision -- Output : s33,31 -> [-2 2) (auto determined) -- Product : s31,31 -> [-5.000000e-001 5.000000e-001) (auto determined) -- Accumulator : s33,31 -> [-2 2) (auto determined) -- Round Mode : No rounding -- Overflow Mode : No overflow -- -------------------------------------------------------------

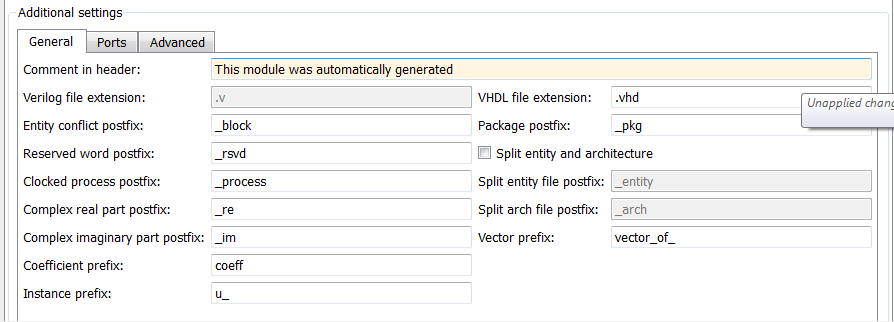

Чтобы добавить комментарий заголовка,

Выберите вкладку Global Settings в диалоговом окне Сгенерировать HDL.

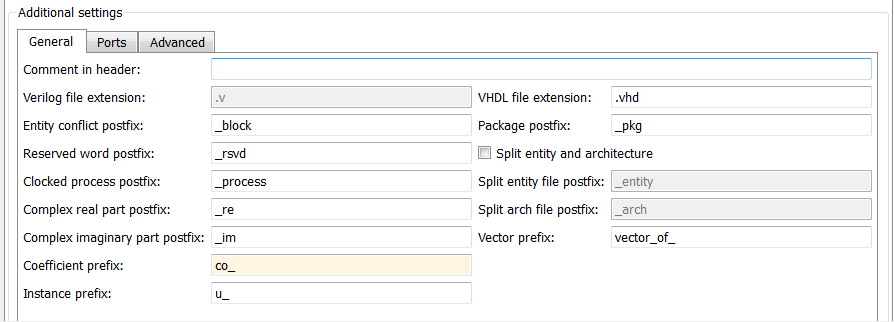

Выберите вкладку General на панели Additional settings.

Введите текст комментария в поле Comment in header, как показано на следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством UserComment чтобы добавить комментарий в конец блока комментариев заголовка в каждом сгенерированном HDL- файла.

Кодер проверяет, имеют ли несколько сущностей в VHDL или несколько модулей в Verilog одно и то же имя. Если существует конфликт имен, кодер добавляет постфикс '_block' ко второму из двух совпадающих векторов символов.

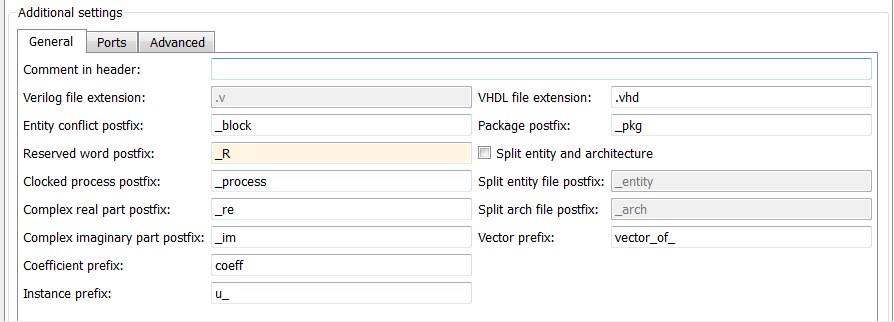

Чтобы изменить постфикс:

Выберите вкладку Global Settings в диалоговом окне Сгенерировать HDL.

Выберите вкладку General на панели Additional settings.

Введите новый вектор символов в поле Entity conflict postfix, как показано на следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством EntityConflictPostfix изменение сущности или модуля приводит к конфликту постфикса.

Кодер проверяет, являются ли векторы символов, которые вы задаете в качестве имен, значений постфикса или меток, зарезервированными словами VHDL или Verilog. Список зарезервированных слов VHDL и Verilog см. в разделе Таблицы зарезервированных слов.

Если вы задаете зарезервированное слово, кодер добавляет постфикс _rsvd в вектор символов. Например, если вы пытаетесь назвать свой фильтр mod, для кода VHDL, кодер добавляет постфикс _rsvd для формирования имени mod_rsvd.

Чтобы изменить постфикс:

Выберите вкладку Global Settings в диалоговом окне Сгенерировать HDL.

Выберите вкладку General на панели Additional settings.

Введите новый вектор символов в поле Reserved word postfix, как показано на следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством ReservedWordPostfix для изменения зарезервированного слова postfix.

В следующих таблицах перечислены VHDL и Verilog зарезервированные слова.

Зарезервированные слова VHDL

abs | access | after | alias | all |

and | architecture | array | assert | attribute |

begin | block | body | buffer | bus |

case | component | configuration | constant | disconnect |

downto | else | elsif | end | entity |

exit | file | for | function | generate |

generic | group | guarded | if | impure |

in | inertial | inout | is | label |

library | linkage | literal | loop | map |

mod | nand | new | next | nor |

not | null | of | on | open |

or | others | out | package | port |

postponed | procedure | process | pure | range |

record | register | reject | rem | report |

return | rol | ror | select | severity |

signal | shared | sla | sll | sra |

srl | subtype | then | to | transport |

type | unaffected | units | until | use |

variable | wait | when | while | with |

xnor | xor |

Verilog зарезервированные слова

always | and | assign | automatic | begin |

buf | bufif0 | bufif1 | case | casex |

casez | cell | cmos | config | deassign |

default | defparam | design | disable | edge |

else | end | endcase | endconfig | endfunction |

endgenerate | endmodule | endprimitive | endspecify | endtable |

endtask | event | for | force | forever |

fork | function | generate | genvar | highz0 |

highz1 | if | ifnone | incdir | include |

initial | inout | input | instance | integer |

join | large | liblist | library | localparam |

macromodule | medium | module | nand | negedge |

nmos | nor | noshowcancelled | not | notif0 |

notif1 | or | output | parameter | pmos |

posedge | primitive | pull0 | pull1 | pulldown |

pullup | pulsestyle_onevent | pulsestyle_ondetect | rcmos | real |

realtime | reg | release | repeat | rnmos |

rpmos | rtran | rtranif0 | rtranif1 | scalared |

showcancelled | signed | small | specify | specparam |

strong0 | strong1 | supply0 | supply1 | table |

task | time | tran | tranif0 | tranif1 |

tri | tri0 | tri1 | triand | trior |

trireg | unsigned | use | vectored | wait |

wand | weak0 | weak1 | while | wire |

wor | xnor | xor |

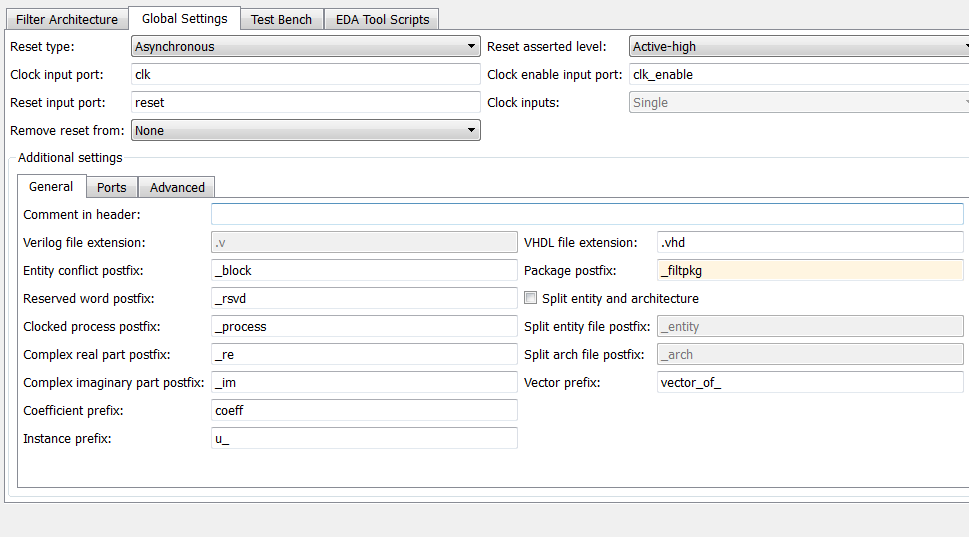

По умолчанию кодер добавляет постфикс _pkg к базовому имени файла при генерации файла пакета VHDL. Чтобы переименовать постфикс для файлов пакета, выполните следующие действия:

Выберите вкладку Global Settings в диалоговом окне Сгенерировать HDL.

Выберите вкладку General на панели Additional settings .

Задайте новое значение в поле Package postfix.

Примечание

При указании вектора символов для использования в качестве постфикса в именах файлов учитывайте размер базового имени и специфичных для платформы требований к именованию файлов и ограничений.

Альтернатива командной строки: используйте generatehdl функция со PackagePostfix свойство для переименования имени файла postfix для файлов пакета VHDL.

Кодер объявляет коэффициенты для фильтра как константы в rtl архитектура. Кодер выводит постоянные имена, добавляя префикс coeff. Имена коэффициентов зависят от типа фильтра.

| Для... | Префикс конкатенирован с... |

|---|---|

| Конечная импульсная характеристика | Каждое число коэффициентов, начиная с 1. Примеры: |

| БИХ | Символ подчеркивания (_) и Пример: |

Для примера:

ARCHITECTURE rtl OF filt IS -- Type Definitions TYPE delay_pipeline_type IS ARRAY(NATURAL range <>) OF signed(15 DOWNTO 0);-- sfix16_En15 CONSTANT coeff1 : signed(15 DOWNTO 0) := to_signed(-30, 16); -- sfix16_En15 CONSTANT coeff2 : signed(15 DOWNTO 0) := to_signed(-89, 16); -- sfix16_En15 CONSTANT coeff3 : signed(15 DOWNTO 0) := to_signed(-81, 16); -- sfix16_En15 CONSTANT coeff4 : signed(15 DOWNTO 0) := to_signed(120, 16); -- sfix16_En15

Как использовать префикс, отличный от coeff,

Выберите вкладку Global Settings в диалоговом окне Сгенерировать HDL.

Выберите вкладку General на панели Additional settings.

Введите новый вектор символов в поле Coefficient prefix, как показано на следующем рисунке.

Вектор символов, который вы задаете

Начнем с буквы.

Невозможно включить двойной символ подчеркивания (__).

Примечание

Если вы задаете зарезервированное слово VHDL или Verilog, кодер добавляет зарезервированное слово postfix к вектору символов, чтобы сформировать допустимый идентификатор. Если вы задаете префикс, который заканчивается подчеркиванием, кодер заменяет символ подчеркивания на under. Для примера, если вы задаете coef_кодер генерирует имена коэффициентов, такие как coefunder1.

Альтернатива командной строки: используйте generatehdl функция со свойством CoeffPrefix для изменения базового имени коэффициентов фильтра.

Кодер генерирует блоки процессов для изменения содержимого регистров. Метка для каждого из этих блоков определяется из имени регистра и постфикса _process. Для примера кодер выводит метку delay_pipeline_process в следующем блоке из имени регистра delay_pipeline и постфикс '_process'.

delay_pipeline_process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

delay_pipeline (0 To 50) <= (OTHERS => (OTHERS => '0'));

ELSIF clk'event AND clk = '1' THEN

IF clk_enable = '1' THEN

delay_pipeline(0) <= signed(filter_in)

delay_pipeline(1 TO 50) <= delay_pipeline(0 TO 49);

END IF;

END IF;

END PROCESS delay_pipeline_process;

Свойство Clocked process postfix позволяет вам изменить постфикс на значение, отличное от '_process'. Например, чтобы изменить постфикс на '_clkproc', выполните следующее:

Выберите вкладку Global Settings в диалоговом окне Сгенерировать HDL.

Выберите вкладку General на панели Additional settings.

Введите новый вектор символов в поле Clocked process postfix, как показано на следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством ClockProcessPostfix для изменения постфикса, добавленного к меткам обработки.

Instance prefix задает вектор символов, префиксируемый к именам образцов компонентов в сгенерированном коде. Значение по умолчанию является 'u_'.

Вы можете задать префикс на значение, отличное от 'u_'. Чтобы изменить префикс:

Выберите вкладку Global Settings в диалоговом окне Сгенерировать HDL.

Выберите вкладку General на панели Additional settings.

Введите новый вектор символов в поле Instance prefix, как показано на следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством InstancePrefix для изменения префикса образца.

Vector prefix задает вектор символов, который будет префиксирован к именам векторов в сгенерированном коде VHDL. Значение по умолчанию является 'vector_of_'.

Примечание

Vector prefix не поддерживается для генерации кода Verilog.

Вы можете задать префикс на значение, отличное от 'vector_of_'. Чтобы изменить префикс:

Выберите вкладку Global Settings в диалоговом окне Сгенерировать HDL.

Выберите вкладку General на панели Additional settings.

Введите новый вектор символов в поле Vector prefix, как показано на следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством VectorPrefix для изменения префикса образца.