Можно оптимизировать тактовую частоту, используемую кодом фильтра, применяя регистры конвейера. Несмотря на то, что регистры увеличивают общую задержку фильтра и используемое пространство, они обеспечивают значительное улучшение тактовой частоты. Эти регистры по умолчанию отключены. Когда вы включаете их, кодер добавляет регистры между этапами расчета в фильтре.

| Для... | Добавлены регистры трубопроводов |

|---|---|

| Конечная импульсная характеристика, антисимметричные конечные импульсные характеристики и симметричные конечные импульсные характеристики фильтры | Между уровнями дерева окончательного суммирования |

| Транспонированные конечная импульсная характеристика | Между умножителями коэффициентов и сумматорами |

| БИХ | Между секциями |

| CIC | Между секциями гребня |

Для примера для фильтра БИХ шестого порядка кодер добавляет два регистра конвейера. Кодер вставляет регистр конвейера между первой и второй секциями и между второй и третьей секциями.

Для конечная импульсная характеристика использование регистров трубопровода оптимизирует итоговое суммирование фильтра. Для получения дополнительной информации смотрите Оптимизацию Итогового Суммирования для конечная импульсная характеристика.

Примечание

Регистры конвейера в конечной импульсной характеристике, антисимметричных конечных импульсных характеристиках и симметричных конечных импульсных характеристиках фильтрах могут выдавать числовые результаты, которые отличаются от результатов, полученных исходным объектом фильтра, потому что они форсируют древовидный режим окончательного суммирования.

Чтобы использовать регистры трубопровода,

Выберите опцию Add pipeline registers на панели Filter architecture диалогового окна Генерация HDL.

Для конечной импульсной характеристики, антисимметричных конечных импульсных характеристик и симметричных конечных импульсных характеристик фильтров рассмотрите установку запаса ошибки для сгенерированного испытательного стенда, чтобы принять во внимание числовые различия. Запас по ошибке - это количество наименее значимых битов, которые испытательный стенд игнорирует при сравнении результатов. Чтобы задать поле ошибки:

Выберите панель Test Bench в диалоговом окне Генерация HDL. Затем перейдите на вкладку Configuration.

Установите поле Error margin (bits) в целое число, которое указывает на максимально допустимое количество бит различия в числовых результатах.

Продолжите установку других опций или щелкните Generate, чтобы инициировать генерацию кода.

Альтернатива командной строки: используйте generatehdl функция со свойством AddPipelineRegisters для оптимизации фильтров с регистрами трубопроводов.

Если вы сохраняете операции умножения для конечная импульсная характеристика, можно достичь более высоких тактовых частот путем добавления этапов конвейера на входах или выходах умножителя.

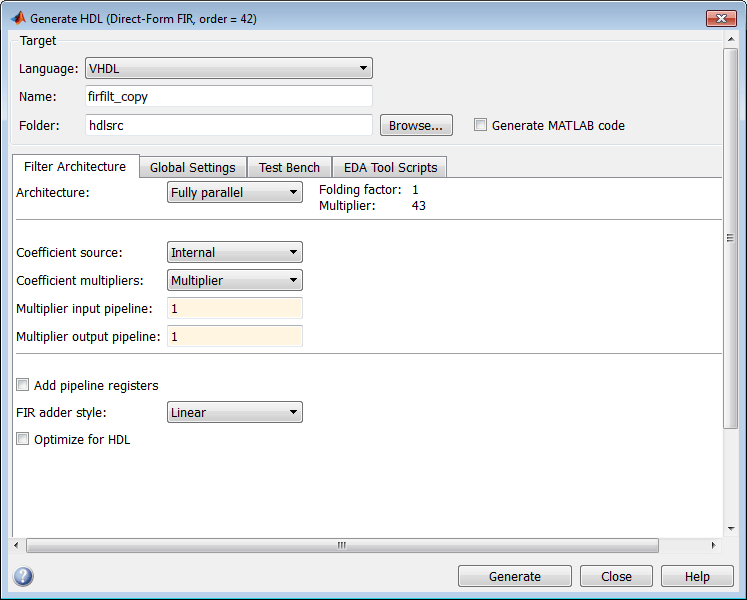

Следующий рисунок показывает опции пользовательского интерфейса для опций конвейеризации множителя. Чтобы включить эти опции, Coefficient multipliers Multiplier.

Multiplier input pipeline: Чтобы добавить этапы трубопровода перед каждым умножителем, введите желаемое количество этапов как целое число, больше или равное 0.

Multiplier output pipeline: Чтобы добавить этапы трубопровода после каждого умножителя, введите желаемое количество этапов как целое число, больше или равное 0.

Альтернатива командной строки: используйте generatehdl функция со MultiplierInputPipeline и MultiplierOutputPipeline свойства для настройки конвейеризации умножителя для конечная импульсная характеристика.

Если вы генерируете HDL-код для конечная импульсная характеристика, рассмотрите оптимизацию метода окончательного суммирования, который будет применяться к фильтру. По умолчанию кодер применяет линейное суммирование сумматора, которое является методом окончательного суммирования, обсуждаемым в большинстве текстовых книг DSP. Кроме того, можно дать указание кодеру применить окончательное суммирование дерева или конвейера. При переходе в древовидный режим кодер создает конечный сумматор, который выполняет парное сложение для последующих продуктов, которые выполняются параллельно, а не последовательно. Режим Pipeline приводит к результатам, подобным древовидному режиму с сложением стадии регистров Pipeline после обработки каждого уровня дерева.

Для сравнения,

Количество операций суммирования для линейного и древовидного режимов одинаковое. Синхронизация для древовидного режима может быть лучше из-за параллельных сложений.

Режим конвейера оптимизирует тактовую частоту, но увеличивает задержку фильтра. Задержка увеличивается на log2(number of products), округлый до ближайшее целого числа.

Линейный режим помогает достичь числовой точности по сравнению с исходным объектом фильтра. Древовидные и конвейерные режимы могут привести к числовым результатам, которые отличаются от результатов, полученных объектом фильтра.

Чтобы изменить окончательное суммирование, которое будет применено к конечная импульсная характеристика:

Выберите один из следующих опций на панели Filter architecture диалогового окна Генерация HDL.

| Для... | Выберите... |

|---|---|

| Линейный режим (по умолчанию) | Linear из меню FIR adder style |

| Древовидный режим | Tree из меню FIR adder style |

| Режим трубопровода | Флажок Add pipeline registers |

Если вы задаете дерево или конвейерный режим, рассмотрите установку запаса по ошибке для сгенерированного испытательного стенда, чтобы учесть числовые различия. Запас по ошибке - это количество наименее значимых битов, которые испытательный стенд игнорирует при сравнении результатов. Чтобы задать поле ошибки,

Выберите панель Test Bench в диалоговом окне Генерация HDL. Затем перейдите на вкладку Configuration.

Установите поле Error margin (bits) в целое число, которое указывает на максимально допустимое количество бит различия в числовых результатах.

Продолжите установку других опций или щелкните Generate, чтобы инициировать генерацию кода.

Альтернатива командной строки: используйте generatehdl функция со свойством FIRAdderStyle или AddPipelineRegisters оптимизировать окончательное суммирование для конечная импульсная характеристика.

Кодер добавляет дополнительный входной регистр (input_register) и дополнительный выходной регистр (output_register) во время генерации HDL-кода. Эти дополнительные регистры могут быть полезны в целях синхронизации, но они добавляют к общей задержке.

Следующий блок процесса записывает в дополнительный входной регистр input_register когда происходит и clk событие синхроимпульса является активным высоким (1):

Input_Register_Process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

input_register <= (OTHERS => '0');

ELSIF clk'event AND clk = '1' THEN

IF clk_enable = '1' THEN

input_register <= input_typeconvert;

END IF;

END IF;

END PROCESS Input_Register_Process ;

Следующий блок процесса записывает в дополнительный выходной регистр output_register когда происходит и clk событие синхроимпульса является активным высоким (1):

Output_Register_Process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

output_register <= (OTHERS => '0');

ELSIF clk'event AND clk = '1' THEN

IF clk_enable = '1' THEN

output_register <= output_typeconvert;

END IF;

END IF;

END PROCESS Output_Register_Process;

Если общая задержка является проблемой для вашего приложения, и у вас нет временных требований, можно подавить генерацию дополнительных регистров следующим образом:

Выберите вкладку Global Settings в диалоговом окне Сгенерировать HDL.

Выберите вкладку Ports на панели Additional settings.

Очистить Add input register и Add output register по мере необходимости. Следующий рисунок показывает настройку для подавления генерации дополнительного входного регистра.

Альтернатива командной строки: используйте generatehdl и функционировать со свойствами AddInputRegister и AddOutputRegister чтобы добавить дополнительный входной или выходной регистр.