Используйте Filter Design HDL Coder™ UI или интерфейс командной строки, чтобы сгенерировать HDL-код для создания фильтра и испытательного стенда. UI генерирует файл VHDL или Verilog испытательного стенда в зависимости от выбора языка для сгенерированного HDL-кода. Можно задать другой язык испытательного стенда, выбрав Test bench language опции на панели Test Bench диалогового окна Генерация HDL. Вы не можете задать другой язык испытательного стенда при использовании интерфейса командной строки.

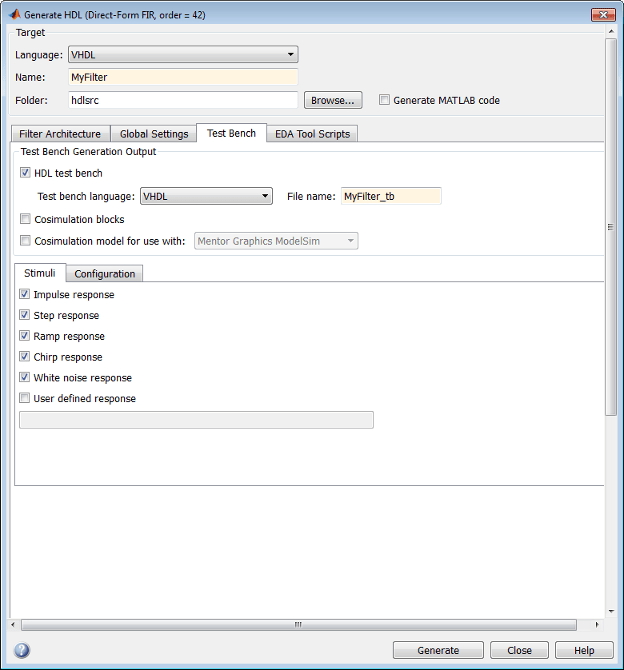

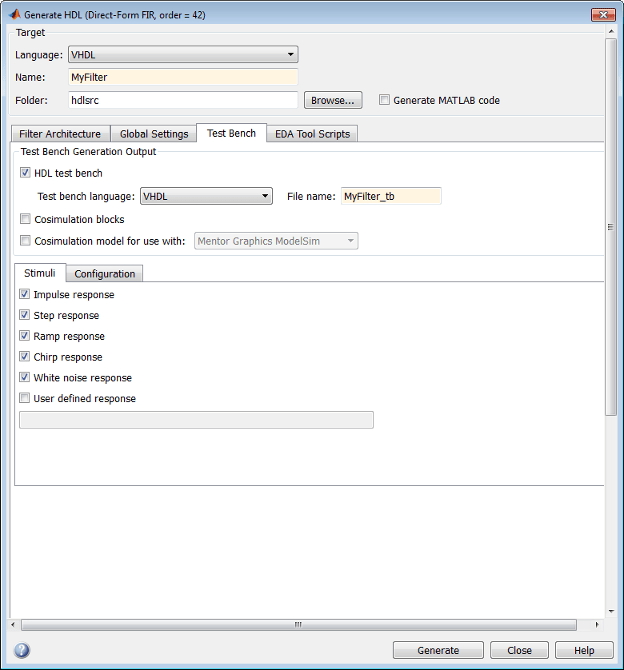

Следующий рисунок показывает настройки для генерации файлов фильтра (VHDL) и испытательного стенда (Verilog) MyFilter.vhd, и MyFilter_tb.v. Диалоговое окно также задает расположение сгенерированных файлов, в данном случае - папки hdlsrc в текущей рабочей папке.

После нажатия Generate, кодер отображает информацию о прогрессе, подобную следующей в MATLAB® Командное окно:

### Starting VHDL code generation process for filter: MyFilter ### Generating: C:\Work\sl_hdlcoder_work\hdlsrc\MyFilter.vhd ### Starting generation of MyFilter VHDL entity ### Starting generation of MyFilter VHDL architecture ### HDL latency is 2 samples ### Successful completion of VHDL code generation process for filter: MyFilter ### Starting generation of VERILOG Test Bench ### Generating input stimulus ### Done generating input stimulus; length 3429 samples. ### Generating Test bench: C:\Work\sl_hdlcoder_work\hdlsrc\MyFilter_tb.v ### Please wait ... ### Done generating VERILOG Test Bench

Примечание

Длина входных выборок стимула изменяется от фильтра к фильтру. Для примера значение 3429 в предыдущей последовательности сообщений не является фиксированной; значение зависит от тестируемого фильтра.

Если вы вызываете generatehdl функция из интерфейса командной строки, установка кода и испытательного стенда с парами имя свойства и значение. Можно также использовать функцию generatetbstimulus чтобы вернуть стимул испытательного стенда в переменную рабочей области.

После того, как вы сгенерируете свой фильтр и испытательный стенд HDL-файлы, запустите симулятор. Когда вы запускаете Mentor Graphics® ModelSim® симулятор, появляется экран, подобный следующему:

Запустив симулятор, установите текущую папку в папку, которая содержит ваши сгенерированные HDL- файлов.

Используя свой выбор HDL компилятора, скомпилируйте сгенерированный фильтр и испытательный стенд HDL- файлов. В зависимости от языка сгенерированного испытательного стенда и симулятора, который вы используете, вам, вероятно, придется выполнить некоторую настройку предварительной компиляции. Например, в симуляторе Mentor Graphics ModelSim можно принять решение создать библиотеку проектов для хранения скомпилированных сущностей, пакетов, архитектур и строений VHDL.

Следующая последовательность команд Mentor Graphics ModelSim изменяет текущую папку на hdlsrcсоздает библиотеку проектов work, и компилирует VHDL-фильтр и испытательный стенд код. The vlib команда создает работу библиотеки проекта и vcom команды инициируют компиляции.

cd hdlsrc vlib work vcom MyFilter.vhd vcom MyFilter_tb.vhd

Примечание

Для кода испытательного стенда VHDL, который имеет реализации с плавающей точкой (double), используйте компилятор, который поддерживает VHDL-93 или VHDL-02. Для примера в симуляторе Mentor Graphics ModelSim задайте vcom команда со -93 опция. Не компилируйте сгенерированный испытательный стенд помощью компилятора VHDL-87. VHDL- испытательных стендов, использующие типы данных с двойной точностью, не поддерживают VHDL-87. В тестовом стендовом коде используется атрибут image, который доступен только в VHDL-93 или выше.

На следующем отображении экрана показана эта командная последовательность и информационные сообщения, отображаемые во время компиляции.

Когда ваши сгенерированные HDL- файлов будут скомпилированы, загрузите и запустите испытательный стенд. Процедура варьируется в зависимости от используемого симулятора. В симуляторе Mentor Graphics ModelSim вы загружаете испытательный стенд для симуляции с vsim команда. Для примера:

vsim work.MyFilter_tb

На следующем отображении показаны результаты загрузки work.MyFilter_tb с vsim команда.

Когда проект будет загружен в симулятор, рассмотрите открытие окна отображения для мониторинга симуляции, когда будет запущен испытательный стенд. Для примера в симуляторе Mentor Graphics ModelSim можно использовать add wave * команда, чтобы открыть wave окно, чтобы просмотреть результаты симуляции как HDL-формы волны.

Чтобы начать выполнение симуляции, выполните команду start simulator. Например, в симуляторе Mentor Graphics ModelSim можно начать симуляцию с run -all команда.

Следующее отображение показывает add wave * команда используется для открытия wave окна и -run all команда используется для запуска симуляции.

Когда ваш испытательный стенд запускается, следите за сообщениями об ошибке. Если появляются сообщения об ошибках, интерпретируйте их так, как они относятся к вашему созданию фильтра и опциям генерации кода, которые вы применяли. Например, некоторые опции оптимизации HDL могут привести к числовым результатам, которые отличаются от результатов, полученных исходным объектом фильтра. Для испытательных стендов HDL сравниваются ожидаемые и фактические результаты. Если они отличаются (за исключением заданного запаса по ошибке), возвращается сообщение об ошибке, аналогичное следующему:

Error in filter test: Expected xxxxxxxx Actual xxxxxxxx

Необходимо определить, ожидаются ли фактические результаты на основе индивидуальных настроек, заданных при генерации HDL-кода фильтра.

Примечание

Сообщение об ошибке, отображаемое на предыдущем отображении, не помечает ошибку. Если сообщение содержит текст Test Complete, испытательный стенд имеет запуск к завершению, не сталкиваясь с ошибкой. The Failure часть сообщения привязана к механизму, который кодер использует для завершения симуляции.

В следующем wave окне показаны результаты симуляции как HDL-формы волны.

Чтобы включить генерацию HDL- испытательного стенда:

Выберите панель Test Bench в диалоговом окне Генерация HDL.

Выберите опцию HDL test bench, как показано на следующем рисунке.

Нажмите Generate, чтобы сгенерировать HDL и испытательный стенд.

Совет

По умолчанию HDL test bench выбран.

Альтернатива командной строки: используйте generatehdl функция со свойством GenerateHDLTestBench для генерации HDL- испытательного стенда.

Кодер выводит имя испытательного стенда, добавляя постфикс _tb на имя квантованного объекта фильтра. Расширение типа файла зависит от типа генерируемого испытательного стенда.

| Если испытательный стенд... | Расширение... |

|---|---|

| Файл Верилога | Определяется полем Verilog file extension в подпанели General панели Global Settings диалогового окна Генерация HDL |

| VHDL- файла | Определяется полем VHDL file extension на панели Global Settings диалогового окна Генерация HDL |

Файл помещается в папку, заданную опцией Folder на панели Target диалогового окна Генерация HDL.

Чтобы задать имя испытательного стенда, введите имя в Name поле панели Test bench settings, как показано на следующем рисунке.

Примечание

Если вы вводите вектор символов, которое является зарезервированным словом VHDL или Verilog, кодер корректирует идентификатор, добавляя зарезервированное слово postfix к вектору символов.

Альтернатива командной строки: используйте generatehdl свойства TestBenchName чтобы указать имя для вашего испытательного стенда.

По умолчанию кодер генерирует один файл испытательного стенда, содержащий испытательный стенд вспомогательные функции, данные и испытательный стенд код. Можно разделить эти элементы на отдельные файлы, выбрав опцию Multi-file test bench в подпанели Configuration панели Test Bench диалогового окна Генерация HDL.

При выборе опции Multi-file test bench активируется опция Test bench data file name postfix. Имена файлов испытательного стенда затем получают из имени испытательного стенда и настройки постфикса, TestBenchName_TestBenchDataPostfix.

Для примера, если имя испытательного стенда my_fir_filt, и целевой язык является VHDL, имена испытательных стендов по умолчанию:

my_fir_filt_tb.vhd: испытательный стенд

my_fir_filt_tb_pkg.vhd: пакет вспомогательных функций

my_fir_filt_tb_data.vhd: пакет данных

Если имя фильтра my_fir_filt и конечным языком является Verilog, имена файлов по умолчанию испытательного стенда:

my_fir_filt_tb.v: испытательный стенд

my_fir_filt_tb_pkg.v: пакет вспомогательных функций

my_fir_filt_tb_data.v: испытательные стенды

Альтернатива командной строки: используйте generatehdl свойства MultifileTestBench, TestBenchDataPostfix, и TestBenchName чтобы сгенерировать и назвать отдельные испытательные стенды вспомогательные функции, данные и файлы кода испытательного стенда.

На основе настроек по умолчанию кодер конфигурирует часы для фильтра испытательного стенда так что он:

Принудительно включает входные сигналы в активный высокий уровень (1).

Устанавливает тактовый сигнал 1 включения синхроимпульса после отключения сигнала сброса.

Силы тактовых входных сигналов низкие (0) на длительность 5 наносекунд и высокие (1) на продолжительность 5 наносекунд.

Чтобы изменить эти настройки строения часов:

Щелкните Configuration на панели Test bench диалогового окна Генерация HDL.

На панели Test Bench выберите подпанель Configuration.

Выполните следующие изменения строения, как описано в следующей таблице:

| Если вы хотите... | Тогда... |

|---|---|

| Отключите принудительное включение входных сигналов | Очистить Force clock enable. |

| Отключите форсирование синхроимпульса входных сигналов | Очистить Force clock. |

| Сбросьте количество наносекунд, которое испытательный стенд управляет входными сигналами синхроимпульса на низком уровне (0) | Задайте положительное целое или двойное число (максимум с 6 значащими цифрами после десятичной точки) в поле Clock low time. |

| Сбросьте количество наносекунд, которое испытательный стенд управляет входными сигналами синхроимпульса высокий (1) | Задайте положительное целое или двойное число (максимум с 6 значащими цифрами после десятичной точки) в поле Clock high time. |

| Измените время задержки, прошедшее между отключением сигнала сброса и установлением сигнала включения синхроимпульса. | Задайте положительное целое число в поле Clock enable delay. |

На следующем рисунке показаны применимые опции.

Альтернатива командной строки: используйте generatehdl свойства ForceClock, ClockHighTime, ForceClockEnable, и TestBenchClockEnableDelay для перенастройки испытательного стенда.

На основе настроек по умолчанию кодер конфигурирует сброс для фильтра испытательного стенда так что он:

Принудительно сбрасывает входные сигналы на активный высокий (1). (Установите входные уровни сброса испытательного стенда с помощью опции Reset asserted level).

Устанавливает входные сигналы сброса на длительность 2 такта.

Применяет время удержания 2 наносекунды для входных сигналов сброса.

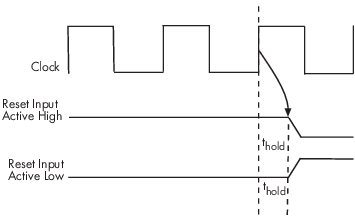

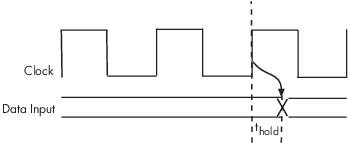

Время удержания - это количество времени, в течение которого испытательный стенд удерживает входные сигналы сброса за ребро повышения синхроимпульса. Рисунок показывает применение времени удержания (thold) для сброса входных сигналов в активных высоких и активных низких случаях. Испытательный стенд обеспечивает сброс после некоторых начальных тактов, определяемых опцией Reset length. Показан Reset length по умолчанию из 2 тактовых импульсов.

Примечание

Время удержания применяется к входным сигналам сброса, только если включена сила входных сигналов сброса.

В следующей таблице представлены параметры строения сброса.

| Если вы хотите... | Тогда... |

|---|---|

| Отключите форсирование входных сигналов сброса | Удаление Force reset на панели Test Bench диалогового окна Генерация HDL. |

| Измените длительность времени (в тактах), в течение которого выполняется сброс | Установите Reset length (in clock cycles) на целое число, больше или равное 0. Эта опция расположена на панели Test Bench диалогового окна Генерация HDL. |

| Измените значение сброса на активное низкое (0) | Выберите Active-low из меню Reset asserted level на панели Global Settings диалогового окна «Генерация HDL» (см. раздел «Установка заданного уровня для входного сигнала сброса») |

| Установите время удержания | Задайте положительное целое или двойное число (максимум с 6 значащими цифрами после десятичной точки), представляющее наносекунды, в поле Hold time. Когда Hold time меняется, значение Setup time (ns) обновляется. Значение Setup time (ns), вычисленное как (clock period - HoldTime) в наносекундах. Эти опции находятся на панели Test Bench диалогового окна Генерация HDL. |

Следующие рисунки подсвечивают применимые опции.

Примечание

Настройки времени удержания и времени настройки также применяются к входным сигналам данных.

Альтернатива командной строки: используйте generatehdl свойства ForceReset, ResetLength, и HoldTime для перенастройки сбросов испытательного стенда.

По умолчанию кодер применяет время удержания 2 наносекунды для входных сигналов фильтрации данных. Время удержания - это количество времени, в течение которого входные сигналы данных должны удерживаться за ребро повышения частоты синхроимпульса. Следующий рисунок показывает применение времени удержания (thold) для входных сигналов данных.

Чтобы изменить настройку времени удержания,

Перейдите на вкладку Test Bench в диалоговом окне Генерация HDL.

На панели Test Bench выберите подпанель Configuration.

Задайте положительное целое или двойное число (максимум с 6 значащими цифрами после десятичной точки), представляющее наносекунды, в поле Hold time. На следующем рисунке время удержания устанавливается равным 2 наносекундам.

Когда Hold time меняется, значение Setup time (ns) обновляется. Кодер вычисляет значение Setup time (ns) следующим (clock period - HoldTime) в наносекундах. Setup time (ns) является полем только для отображения.

Примечание

Когда вы активируете принудительную передачу входных сигналов сброса, время удержания и настройки времени настройки также применяются к сигналам сброса.

Альтернатива командной строки: используйте generatehdl свойства HoldTime чтобы настроить настройку времени удержания.

Индивидуальные настройки, которые обеспечивают оптимизацию, могут сгенерировать испытательный стенд, который приводит к числовым результатам, которые отличаются от результатов, полученных исходным объектом фильтра. Эти опции включают:

Optimize for HDL

FIR adder style установлено на Tree

Add pipeline registers для конечной импульсной характеристики, асимметричных конечных импульсных характеристик и симметричных конечных импульсных характеристик фильтров

Для учета различий в числовых результатах рассмотрите установку запаса по ошибке для сгенерированного испытательного стенда. Запас по ошибке - это количество наименее значимых битов, которые испытательный стенд игнорирует при сравнении результатов. Чтобы задать поле ошибки:

Выберите панель Test Bench в диалоговом окне Генерация HDL.

На панели Test Bench выберите подпанель Configuration.

Для фильтров с фиксированной точкой поле начального Error margin (bits) имеет значение по умолчанию 4. Чтобы изменить поле ошибки, введите целое число в поле Error margin (bits). На следующем рисунке значение поля ошибки устанавливается равным 4 биты.

Альтернатива командной строки: используйте generatehdl свойства ErrorMargin для определения количества бит допустимой ошибки.

По умолчанию начальное значение, управляемое на входах испытательного стенда, 'X' (неизвестно). Кроме того, можно задать, что начальное значение, управляемое на входах испытательного стенда, 0, следующим образом:

Выберите панель Test Bench в диалоговом окне Генерация HDL.

На панели Test Bench выберите подпанель Configuration.

Для установки начального входа стенда в 0Выберите опцию Initialize test bench inputs.

Для установки начального входа стенда в 'X', очистить опцию Initialize test bench inputs.

Альтернатива командной строки: используйте generatehdl свойства InitializeTestBenchInputs установить исходный вход испытательного стенда.

По умолчанию кодер генерирует испытательный стенд фильтра, который включает в себя стимулы, которые соответствуют заданному типу фильтра. Однако при необходимости можно настроить настройки стимулов или задать определяемые пользователем стимулы.

Чтобы изменить входящие в испытательный стенд стимулы, выберите один или несколько типов отклика на Stimuli подпанели вкладки Test bench диалогового окна Генерация HDL. Рисунок подсвечивает эту панель диалогового окна.

Если вы выбираете User defined response, задайте выражение или функцию, которая возвращает вектор значений, которые будут применены к фильтру. Значения, заданные в векторе, квантуются и масштабируются на основе настроек квантования фильтра.

Альтернатива командной строки: используйте generatehdl свойства TestBenchStimulus и TestBenchUserStimulus для настройки настроек стимулов.

Данные опорного сигнала представлены в виде массивов в сгенерированном коде испытательного стенда. Вектор символов, заданный Test bench reference postfix, добавляется к именам сгенерированных сигналов. Значение по умолчанию является '_ref'.

Вы можете задать постфикс на значение, отличное от '_ref'. Чтобы изменить этот параметр:

Выберите панель Test Bench в диалоговом окне Генерация HDL.

На панели Test Bench выберите подпанель Configuration.

Введите новый вектор символов в поле Test bench reference postfix, как показано на следующем рисунке.

Альтернатива командной строки: используйте generatehdl свойства TestBenchReferencePostfix для изменения вектора символов postfix.