Следуйте инструкциям для вызова HDL Workflow Advisor в MATLAB®. См. раздел Начало работы с HDL Workflow Advisor (HDL Coder).

Примечание

Для генерации HDL-кода с помощью HDL Workflow Advisor необходимо иметь лицензию на HDL Coder™.

В разделе Select Code Generation Target убедитесь, что Workflow установлено на Generic ASIC/FPGA.

В разделе HDL Verification выберите Verify with FPGA-in-the-Loop.

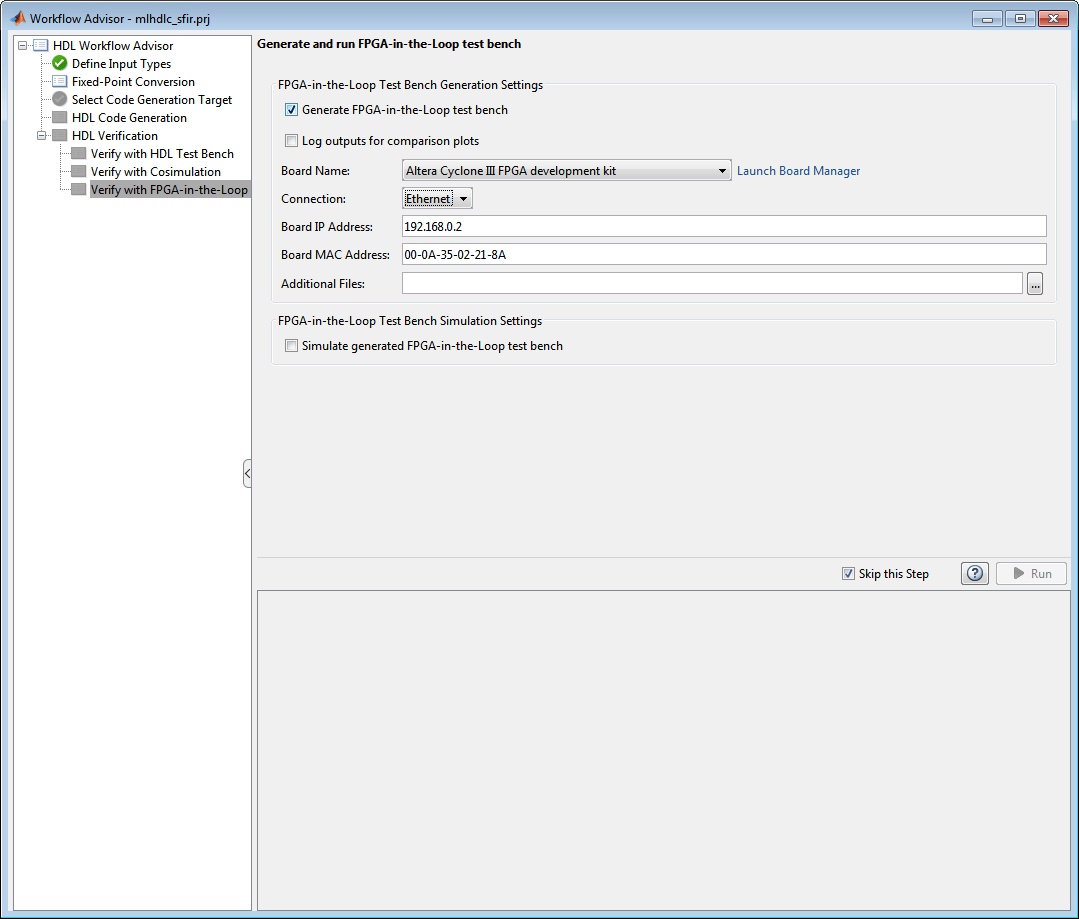

Generate FPGA-in-the-Loop test bench: Выберите эту опцию, чтобы сгенерировать испытательный стенд для симуляции с FPGA-в цикл.

Log outputs for comparison plots: Этот дополнительный выбор позволяет вам логгировать и построить выходы функции исходного проекта и FPGA.

Board Name: Выберите одну из плат разработки FPGA. Если вы еще не загрузили пакет поддержки платы HDL Verifier™ FPGA, выберите Get more boards. А после загрузки пакета поддержки платы FPGA вернитесь к этому шагу.

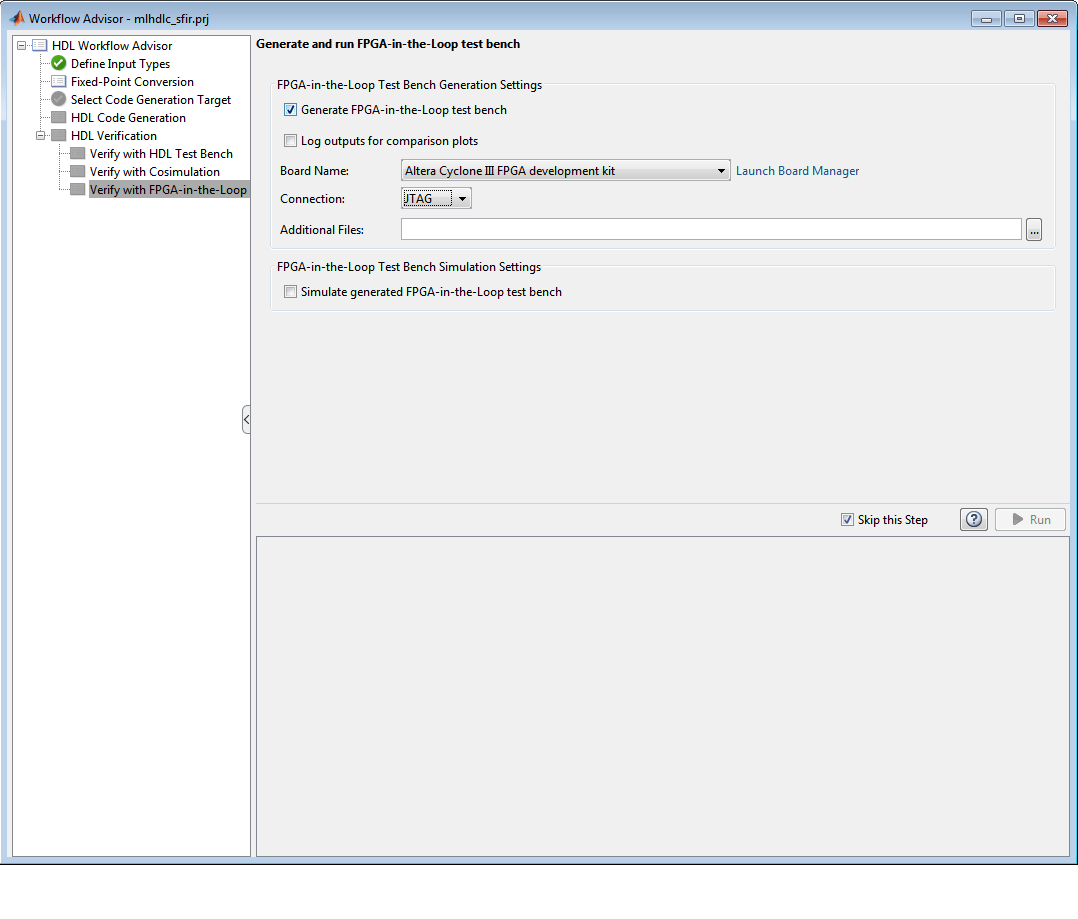

FPGA-in-the-Loop Connection: Метод соединения симуляции FIL. Опции в раскрывающемся меню обновляются в зависимости от методов подключения, поддерживаемых для выбранной целевой платы. Если целевая плата и HDL Verifier поддерживают подключение, можно выбрать Ethernet, JTAG, или PCI Express.

Board IP Address и Board MAC Address:

При выборе соединения Ethernet можно при необходимости настроить IP-адрес и MAC-адрес платы.

| Опция | Инструкции |

|---|---|

| Board IP address | Используйте эту опцию для настройки IP-адреса платы, если он не является IP-адресом по умолчанию (192.168.0.2). Если IP-адрес платы по умолчанию (192.168.0.2) используется другим устройством или вам нужна другая подсеть, измените IP-адрес платы в соответствии со следующими рекомендациями:

|

| Board MAC address | В большинстве случаев вам не нужно менять MAC-адрес платы. Если вы подключите несколько плат разработки FPGA к одному хосту-компьютеру, измените MAC-адрес платы для любых дополнительных плат так, чтобы каждый адрес был уникальным. Для каждой платы необходимо иметь отдельный сетевой адаптер. Для изменения MAC-адреса платы щелкните в поле Board MAC address. Укажите адрес, отличный от адреса любого другого устройства, подключенного к компьютеру. Для получения MAC-адреса системной платы для конкретной платы разработки FPGA см. метку, проставленную на плате, или ознакомьтесь с документацией по продукту. |

Additional files

Введите имена любых дополнительных исходных файлов для DUT. Если у вас есть несколько дополнительных исходных файлов, используйте кнопку ..., чтобы добавить больше.

FPGA-in-the-Loop Test Bench Simulation Settings:

Если необходимо, чтобы HDL Workflow Advisor открыл симуляцию FIL, установите флажок для Simulate generated FPGA-in-the-Loop test bench.

FIL по Ethernet

FIL по JTAG

FIL Over PCI Express

Если вы еще не запустили предыдущие шаги, щелкните правой кнопкой мыши Verify with FPGA-in-the-Loop и выберите Run to Selected Task. В противном случае нажмите кнопку Run.

Этот шаг генерирует пользовательскую hdlverifier.FILSimulation Системный object™, который обеспечивает интерфейс к вашему проекту, работающему на плате FPGA, и генерирует испытательный стенд, который использует этот объект для подключения к плате FPGA.

Если вы выбрали Simulate generated FPGA-in-the-Loop test bench, этот шаг загружает файл программирования FPGA в FPGA и запускает автоматически сгенерированный испытательный стенд с цикл.

Если вы не выбрали Simulate generated FPGA-in-the-Loop test bench, необходимо загрузить файл программирования FPGA вручную, используя либо настроенный toplevel_programFPGAprogramFPGA метод сгенерированного объекта. Напоминаем: если вы еще не выполнили Управляемый Аппаратный Setup или Настройте FPGA Проекта Software Инструментов, сделайте это сейчас, прежде чем загружать файлы программирования.

Произведенный toplevel_programFPGA

./toplevel_fil/toplevel_programFPGA

programFPGA функция объекта:

MYFIL.programFPGA

Чтобы запустить проект на плате FPGA, запустите сгенерированный испытательный стенд или используйте сгенерированный объект в собственном коде MATLAB. Первый вызов объекта устанавливает связь с платой FPGA.