Настройка управляемого оборудования для плат FPGA помогает быстрее начать работу с FPGA-in-the- Цикла (FIL), данными захватом или MATLAB AXI master. Прежде чем запускать управляемую настройку, убедитесь, что все необходимое оборудование готово и все необходимые сторонние программы уже установлены.

Управляемая настройка запускается автоматически во время загрузки и установки пакета поддержки. После установки выбранного пакета поддержки появится запрос на выбор имени платы и интерфейса, который необходимо использовать с этой платой. Вы можете выбрать только интерфейсы, поддерживаемые платой FPGA. A PCI Express® связь с FIL не поддерживается в Linux®.

Примечание

Чтобы перезапустить настройку пакета поддержки в любое время:

На MATLAB® Home вкладке в Environment разделе выберите Help > Check for Updates.

Примечание

Не подключайте и не включайте плату разработки FPGA до получения запроса на более позднем шаге.

Плата разработки FPGA

Кабель USB-JTAG с установленным программным обеспечением поставщика (Vivado® или Quartus®)

Кабель Ethernet

Выделенная сетевая плата (NIC) или адаптер USB 3.0 Gigabit Ethernet

Степень адаптер питания (если для платы требуется один)

Плата разработки FPGA

Кабель USB-JTAG с установленным программным обеспечением поставщика (Vivado или Quartus)

Степень адаптер питания (если для платы требуется один)

HDL Verifier™ поддерживает подключение PCI Express для FIL с Windows® только операционные системы.

Плата разработки FPGA

Кабель USB-JTAG с установленным программным обеспечением поставщика (Vivado или Quartus)

Паз PCI Express и доступные пространства на системной плате

Степень адаптер питания (если для платы требуется один)

Убедитесь, что выключатель степени платы отключен во время этих шагов настройки. Отобразится запрос на включение степени на более позднем шаге.

Подключите шнур степени переменного тока к степени штекеру и подключите кабель адаптера питания степени к плате разработки FPGA.

Используйте кабель crossover Ethernet для подключения разъема Ethernet на плате разработки FPGA непосредственно к адаптеру Ethernet на вашем компьютере.

Используйте кабель загрузки JTAG для подключения платы разработки FPGA к компьютеру.

Убедитесь, что все перемычки на плате разработки FPGA находятся в заводском положении по умолчанию.

Включите переключатель степени на плате FPGA.

Убедитесь, что выключатель степени платы отключен во время этих шагов настройки. Отобразится запрос на включение степени на более позднем шаге.

Подключите шнур степени переменного тока к степени штекеру и подключите кабель адаптера питания степени к плате разработки FPGA.

Используйте кабель загрузки JTAG для подключения платы разработки FPGA к компьютеру.

Убедитесь, что все перемычки на плате разработки FPGA находятся в заводском положении по умолчанию.

Включите переключатель степени на плате FPGA.

Убедитесь, что выключатель степени платы отключен во время этих шагов настройки. Отобразится запрос на включение степени на более позднем шаге.

Выберите максимальное количество каналов PCI Express, поддерживаемых платой. Для получения дополнительной информации см. руководство пользователя по системной плате.

| Поддерживаемая плата | Интерфейс PCI Express Setup | Документация |

|---|---|---|

| DSP Development Kit, Стратикс® V Издание | Установите три переключателя (PCIE_PRSNT2nx1, x4, x8) в dip switch SW6 на ON. Этот параметр выбирает 8-линейный PCIe (настройка платы по умолчанию). | https://www.intel.com/content/www/us/en/programmable/products/boards_and_kits/dev-kits/altera/kit-stratix-v-dsp.html |

| Циклон® V GT Комплект для разработки ПЛИС | Установите два переключателя (PCIe_x1, x4) в dip switch SW3 на ON. Этот параметр выбирает PCIe с 4 линиями (настройка платы по умолчанию). | https://www.intel.com/content/www/us/en/programmable/products/boards_and_kits/dev-kits/altera/kit-cyclone-v-gt.html |

| Kintex®- 7 KC705 | Установите J32 перемычки так, чтобы она соединяла контакты 5 и 6. Этот параметр выбирает 8-линейный PCIe (настройка платы по умолчанию). | https://www.xilinx.com/products/boards-and-kits/ek-k7-kc705-g.html |

| Virtex®- 7 VC707 | Установите J49 перемычки так, чтобы она соединяла контакты 5 и 6. Этот параметр выбирает 8-линейный PCIe (не параметр платы по умолчанию). | https://www.xilinx.com/products/boards-and-kits/ek-v7-vc707-g.html |

Выключите хост-компьютер.

Установите плату разработки FPGA в паз PCI Express внутри хоста-компьютера.

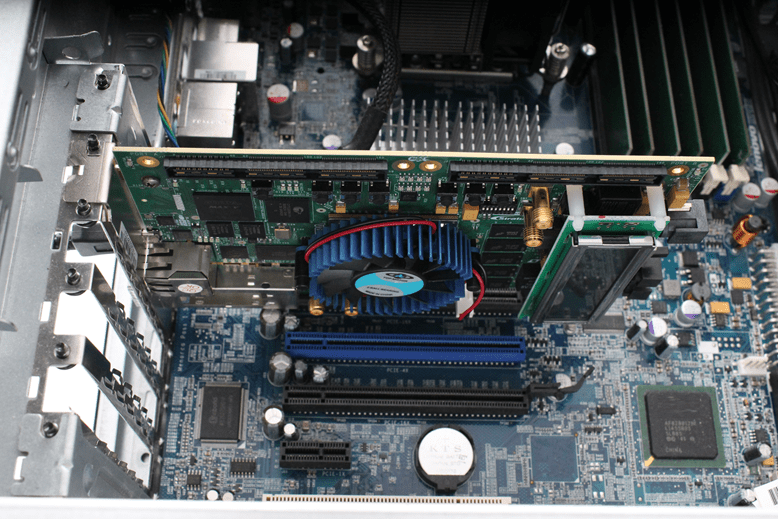

Установлена плата Stratix V

Эта установка также применяется ко всем поддерживаемым Intel® Платы VC.

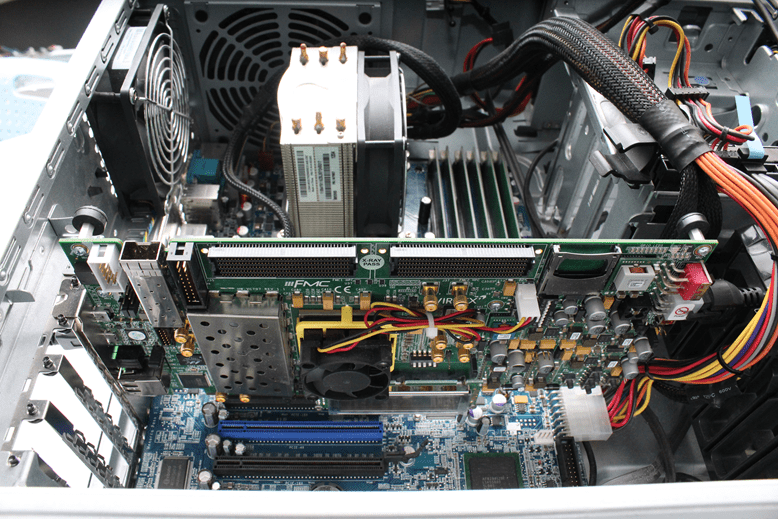

VC707 системной платы

Обратите внимание на степень справа. Эта установка также применяется ко всем поддерживаемым Xilinx® платы.

Для плат Xilinx подключите внешний источник степени к розетке стенки. Затем подключите кабель адаптера степени питания к плате разработки FPGA.

Системные платы Intel не используют внешний источник степени.

Подключите кабель JTAG к плате разработки FPGA и компьютеру. Когда вы используете PCI Express для симуляции FIL, для программирования FPGA все еще требуется кабель JTAG.

Включите переключатель степени на плате FPGA.

Запустите хост-компьютер.

Этот шаг требуется только при использовании FIL по Ethernet.

Если сетевая карта уже настроена, этот шаг можно пропустить.

Укажите сетевую карту на хост-компьютер, которую необходимо использовать с платой разработки и FIL. Если у вас есть только один NIC, необходимо отключить от Интернета при использовании NIC для FIL. В этом случае рассмотрите использование адаптера USB 3.0 Gigabit Ethernet dongle. Если вы добавляете сетевой адаптер или адаптер USB 3.0 Gigabit Ethernet на этом шаге настройки, нажмите Refresh, чтобы увидеть новое оборудование в списке.

Оставьте IP-адрес сетевого адаптера по умолчанию или укажите IP-адрес в пунктирном формате квадрат, например 192.168.0.1.

Этот шаг требуется только при использовании FIL через PCI Express.

Если драйверы PCI Express уже установлены, этот шаг можно пропустить.

Установите драйверы PCI Express перед использованием FIL с PCI Express. На этом шаге выполняется установка драйвера. Процесс может занять 10 или более минут и может потребовать прав системного администратора.

Можно позволить настройке пакета поддержки установить драйверы сейчас, или можно принять решение о повторном запуске настройки позже. Чтобы запустить настройку пакета поддержки в любое время:

На вкладке Home MATLAB, в разделе Environment, выберите Help > Check for Updates.

Можно проверить настройку оборудования для подключений Ethernet и JTAG. Этот шаг запускает тест FPGA в цикле, который генерирует файл программирования FPGA для вашей платы. Можно также указать, что этот шаг включает плату FPGA в тест, что означает, что шаг фактически выполняет косимуляцию FIL с вашей платой.

Убедитесь, что вы установили соответствующий инструмент поставщика и что инструмент находится на пути MATLAB. Смотрите раздел Настройка программного обеспечения Проект FPGA Инструменты.

Выберите Run FPGA-in-the-Loop test. Если необходимо включить плату FPGA в тест, выберите Include FPGA board in the test.

Нажмите Run Selected Tests.

Можно повторить тесты столько раз, сколько угодно. Когда тесты будут завершены к вашему удовлетворению, вы можете продолжить настройку.

Когда установщик завершит настройку вашего оборудования, можно либо выйти из установщика, либо открыть пример Verify HDL Implementation of ПИД-регулятор Используя цикл, чтобы начать.