Представление времени симуляции значительно отличается между Симулятором HDL и Simulink®. Каждое приложение имеет свой собственный механизм синхронизации, и программное обеспечение верификации должно синхронизировать времена симуляции между ними.

В симуляторе HDL модуль измерения времени симуляции упоминается как такт. Длительность такта определяется пределом разрешения Симулятора HDL. Разрешение по умолчанию предела 1 нс, но может варьироваться в зависимости от симулятора.

ModelSim® Пользователи:

Чтобы определить текущий предел разрешения ModelSim, введите echo $resolution или report simulator state в приглашении ModelSim. Вы можете переопределить предел разрешения по умолчанию, задав -t опция в командной строке ModelSim или путем выбора другого Разрешение в диалоговом окне ModelSim Simulate. Доступные разрешения в ModelSim 1x, 10x, или 100x в единицах fs, ps, ns, us, ms или sec. Для получения дополнительной информации смотрите документацию ModelSim.

Острый® Пользователи:

Чтобы определить текущий предел разрешения Симулятора HDL, введите echo $timescale по запросу Симулятора HDL. Для получения дополнительной информации см. Симулятор HDL документацию.

Simulink поддерживает время симуляции как значение двойной точности, масштабируемое до секунд. Это представление включает моделирование как непрерывных, так и дискретных систем.

Отношение между Simulink и Симулятором HDL временем влияет на следующие аспекты симуляции:

Общее время симуляции

Input port шагов расчета

Выход порт шагов расчета

Тактовые периоды

Во время прогона симуляции Simulink сообщает текущее время симуляции симулятору HDL на каждом промежуточном шаге. (Промежуточный шаг соответствует временному хиту Simulink. На каждом промежуточном шаге новые значения применяются к входным портам, или выходные порты дискретизируются.)

Чтобы привести симулятор HDL в соответствие с Simulink во время косимуляции, необходимо преобразовать дискретизированное время Simulink во время симулятора HDL (тактов) и позволить HDL-симулятору запускаться для вычисленного количества тактов.

Различия в представлении времени симуляции могут быть согласованы одним из двух способов с помощью интерфейса HDL- Verifier™:

Путем определения отношения синхронизации вручную (с Timescales панелью)

Когда вы задаете отношение вручную, вы определяете, сколько фемтосекунд, пикосекунд, наносекунд, микросекунд, миллисекунд, секунд или тактов в симуляторе HDL представляют 1 секунду в Simulink.

Путем разрешения HDL Verifier определять шкалу времени (с Timescales панелью)

Когда вы позволяете программе задать отношение времени, она пытается задать коэффициент времени между Симулятором HDL и Simulink как можно ближе к 1 секунде в Симулятор HDL = 1 секунде в Simulink. Если эта настройка невозможна, HDL Verifier пытается задать скорость сигнала на порте модели Simulink как минимум возможное количество Симулятора HDL тактов.

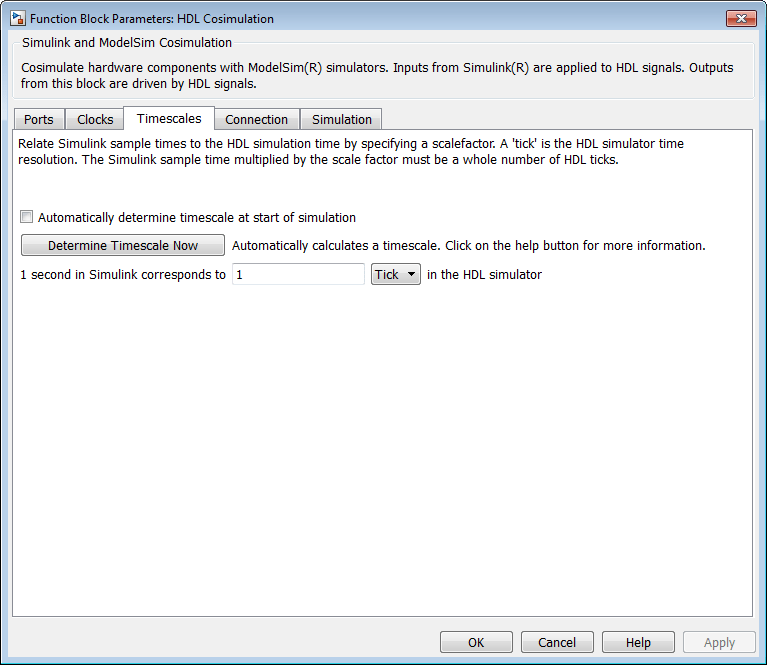

Панель Timescales диалогового окна параметров блоков HDL Cosimulation задает соответствие между одной секундой времени Simulink и некоторой величиной времени симулятора HDL. Такое количество времени симулятора HDL может быть выражено одним из следующих способов:

В относительных терминах (т.е. как некоторое количество Симулятора HDL тактов). В этом случае, называется, что косимуляция работает в относительном временном режиме. Блок HDL Cosimulation по умолчанию переходит в относительный режим синхронизации для косимуляции. Для получения дополнительной информации об относительном режиме синхронизации см. Раздел «Относительный режим синхронизации».

В абсолютных модулях (таких как миллисекунды или наносекунды). В этом случае называется, что косимуляция работает в абсолютном временном режиме. Для получения дополнительной информации об абсолютном режиме синхронизации см. «Абсолютный режим синхронизации».

Панель Timescales позволяет вам выбрать оптимальное соотношение времени между Simulink и Симулятором HDL либо путем ввода Симулятора HDL эквивалента, либо путем разрешения HDL Verifier вычислить шкалу времени для вас.

Можно выбрать, чтобы HDL Verifier вычислял шкалу времени во время установки параметров в диалоговом окне блока, нажав на опцию Timescale, затем щелкнув Determine Timescale Now или можно получить HDL Verifier вычислить шкалу времени, когда симуляция начинается путем выбора Automatically determine timescale at start of simulation.

Следующий рисунок показывает настройки по умолчанию панели Timescales (пример показан для использования с ModelSim).

Инструкции по установке режима синхронизации вручную или с помощью диалогового окна Timescales см. на панели Timescales в HDL Cosimulation вхождении блока.

Чтобы программное обеспечение HDL Verifier рассчитало отношение времени для вас:

Запустите симулятор HDL. Программное обеспечение HDL Verifier может получить разрешение по пределу Симулятора HDL только при запуске этого симулятора.

Выберите, чтобы программное обеспечение HDL Verifier предложило шкалу времени, немедленно или вычислить шкалу времени при запуске симуляции Simulink.

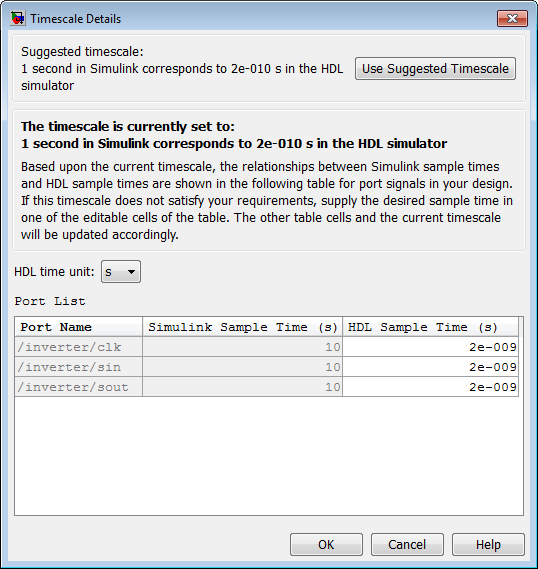

Чтобы выполнить вычисление во время настройки блока, на вкладке Timescale нажмите Determine Timescale Now. Программа соединяет Simulink с Симулятором HDL, чтобы Simulink мог использовать разрешение Симулятора HDL для вычисления наилучшей шкалы времени. Затем ссылка отображает результаты в диалоговом окне Timescale Details.

Примечание

Чтобы результаты отображались, убедитесь, что Симулятор HDL работает и проект загружен для косимуляции. Симуляция не должна выполняться.

Вы можете принять предложенный шкала времени, или изменить список портов непосредственно:

Чтобы вернуться к первоначально рассчитанным настройкам, нажмите Use Suggested Timescale.

Чтобы просмотреть шаги расчета для всех портов в HDL- проекта, выберите Show all ports and clocks.

Чтобы выполнить вычисление, когда симуляция начнётся, выберите Automatically determine timescale at start of simulation и нажмите Apply. Вы получаете то же диалоговое окно Timescale Details, когда симуляция начинается в Simulink.

Примечание

Чтобы результаты отображались, убедитесь, что Симулятор HDL работает и проект загружен для косимуляции. Симуляция не должна выполняться.

Программное обеспечение HDL Verifier анализирует все тактовые и портовые частоты сигналов от блока HDL Cosimulation, когда программное обеспечение вычисляет коэффициент шкалы.

Примечание

Программное обеспечение HDL Verifier не может автоматически вычислить временную шкалу выборки на основе любых сигналов, управляемых с помощью команд Tcl или в симуляторе HDL. Программное обеспечение ссылки не может выполнить такие вычисления, потому что не может знать скорости этих сигналов.

Программное обеспечение ссылки возвращает частоту дискретизации за секунды или такты:

Если результаты указаны в секундах, то программное обеспечение ссылки смогло разрешить различия во времени в пользу точности (абсолютное время).

Если результаты указаны в тактах, то программное обеспечение ссылки было лучше всего способно разрешить различия во времени в пользу эффективности (относительное время).

Каждый раз, когда вы выбираете Determine Timescale Now или Automatically determine timescale at start of simulation, открывается интерактивное отображение. На этом отображении описываются результаты вычисления шкалы времени. Если программное обеспечение ссылки не может вычислить шкалу времени для заданных шагов расчета, измените шаги расчета в Port List.

Щелкните Apply, чтобы зафиксировать изменения.

Примечание

HDL Verifier не поддерживает временные шкалы, рассчитанные автоматически из основанных на кадрах сигналов.

Относительный режим синхронизации задает следующее соответствие один к одному между временем симуляции в Simulink и Симулятор HDL:

Одна секунда в Simulink соответствует N тактов в Симулятор HDL, где N является шкала фактором. |

Эта корреспонденция выполняется независимо от Симулятора HDL временного разрешения.

Следующий псевдокод показов, как модули времени Simulink преобразуются в Симулятор HDL тактов:

InTicks = N * tInSecs

где InTicks является Симулятор HDL временем в такты, tInSecs время Simulink в секундах и N является шкала фактором.

Блок HDL Cosimulation по умолчанию переходит в относительный режим синхронизации с коэффициентом шкалы 1. Таким образом, 1 секунда Simulink соответствует 1 такту в симуляторе HDL. В случае по умолчанию:

Если общее время симуляции в Simulink задано как N секунд, тогда симуляция HDL будет запускаться точно N такты (т.е. N ns при предельном разрешении по умолчанию).

Точно так же, если Simulink вычисляет шаг расчета входного порта блока HDL Cosimulation как Tsi секунд, новые значения будут отложены на входном порте HDL при точных кратных тактах. Если порт выхода имеет явно заданную шаг расчета Tso секунд, значения считываются с симулятора HDL в множители из тактов Tso.

Чтобы понять, как работает относительный режим синхронизации, рассмотрим результаты косимуляции из следующей модели примера.

Режим абсолютного времени позволяет вам задать отношение времени между Simulink и Симулятором HDL с точки зрения абсолютных временных модулей и шкалы фактора:

| Одна секунда в Simulink соответствует (N * Tu) секундам в HDL симуляторе, где Tu является абсолютным временным модулем (для примера, ms, ns и т.д.), а N является шкалой фактором. |

В режиме абсолютной синхронизации все шаги расчета и тактовые периоды в Simulink квантуются, чтобы Симулятор HDL тактов. Следующий псевдокод иллюстрирует преобразование:

tInTicks = tInSecs * (tScale / tRL)

где:

tInTicks - это Симулятор HDL время в такты.

tInSecs - время Simulink в секундах.

tScale - установка шкалы времени (модуль и масштабный коэффициент), выбранная в панели Timescales блока HDL Cosimulation.

tRL - это Симулятор HDL предел разрешения.

Например, учитывая настройку панели Timescales 1 с и ограничение разрешения HDL-симулятора 1 нс, время расчета выходного порта 12 нс будет преобразовано в метки деления следующим образом:

tInTicks = 12ns * (1s / 1ns) = 12

Чтобы сконфигурировать параметры Timescales для абсолютного режима синхронизации, вы выбираете модуль абсолютного времени, которая соответствует секунде Simulink, а не выбираете Tick.

Чтобы понять операцию абсолютного временного режима, вы снова рассмотрим пример модели, обсуждаемый в Операции Относительного Временного Режима. Предположим, что модель перенастроена следующим образом:

Параметры симуляции в Simulink:

Timescale параметров: 1 s времени Simulink соответствует 1 s времени симулятора HDL.

Общее время симуляции: 60e-9 s (60ns)

Input port (/inverter/inport) шаг расчета: 24e-9 s (24 ns)

Выходной порт (/inverter/outport) шаг расчета: 12e-9 s (12 ns)

Часы (inverter/clk) период: 10e-9 s (10 ns)

Симулятор HDL разрешения предела: 1 ns

Учитывая эти параметры симуляции, программное обеспечение Simulink будет сопряжено с Симулятором HDL в течение 60 нс, во время которого Simulink будет дискретизировать входы в интервалы 24 нс, обновлять выходы в интервалы 12 нс и приводить часы в интервалы 10 нс.

Следующий рисунок показывает окно wave ModelSim после прогона косимуляции.

При установке режима шкалы времени, возможно, потребуется выбрать настройку исходя из следующих факторов.

К использованию абсолютного и относительного режимов синхронизации применяются следующие ограничения:

Когда несколько блоков HDL Cosimulation в модели взаимодействуют с одним образцом Симулятора HDL, все блоки HDL Cosimulation должны иметь одинаковые настройки панели Timescales.

Если вы измените настройки панели Timescales в блоке HDL Cosimulation между последовательными запусками косимуляции, необходимо перезапустить симуляцию в Симулятор HDL.

Если вы задаете шаг расчета Simulink, которая не может быть выражена как целое число HDL- тактов, вы получите ошибку.

При использовании нецелочисленных периодов времени Симулятора HDL не может представлять такое бесконечно повторяющееся значение. Таким образом, симулятор обрезает период времени, но это происходит по-другому, чем то, как Simulink обрезает значение, и эти два периода времени больше не совпадают.

Следующий пример демонстрирует, как установить отношение синхронизации в следующем сценарии: вы хотите использовать период дискретизации в Simulink, что соответствует нецелочисленному периоду времени.

Ключевая идея здесь заключается в том, что вы должны всегда иметь возможность связать время Simulink с HDL- такта. HDL- такта является лучшим временным срезом, который распознает Симулятор HDL; для ModelSim такт деления по умолчанию является 1 нс, но она может быть сделана так же точно, как 1 фс.

Однако сигнал 3 Гц на самом деле имеет период 333.33333333333... ms, который не является действительным периодом такта для Симулятора HDL. Такие цифры будут усечены Симулятором HDL. Но Simulink не принимает того же решения; таким образом, для косимуляции, где вы пытаетесь сохранить два независимых симулятора в синхронизации, вы не должны ничего предполагать. Вместо этого вы должны решить, удобно ли усекать или округлить число.

Поэтому решение состоит в том, чтобы «привязать» либо шаг расчета Simulink, либо шаг расчета HDL (через шкалу времени) к допустимым числам. Возможности бесконечны, но вот несколько возможных способов выполнить привязку:

Измените шаги расчета Simulink с 1/3 секунды до 0,33333 секунды и установите временную шкалу блока косимуляции на '1 секунду в Simulink = 1 секунду в симуляторе HDL'. Если вы задаете часы на панели HDL Cosimulation блока Clocks, его период должен составлять 0.33333 секунд.

Сохраните шаги расчета Simulink на уровне 1/3 сек. и 1 секунду в Simulink = 6 такты в Симулятор HDL.

Если вы задаете часы в панели HDL Cosimulation блока Clocks, его период должен быть 1/3. Вкратце, эта спецификация говорит Simulink, чтобы каждый шаг расчета Simulink соответствовал каждому (1/3 * 6) = 2 такты, независимо от временного разрешения HDL.

Если ваше разрешение симулятора HDL по умолчанию составляет 1 нс, это означает, что ваши шаги расчета HDL каждые 2 нс. Этот пример времени будет работать таким образом, чтобы для каждого шага расчета Simulink существовал соответствующий HDL пример времени.

Однако Simulink думает с точки зрения периодов 1/3 с и HDL с точки зрения периодов 2 нс. Таким образом, можно было запутаться во время отладки. Если вы хотите, чтобы это совпадало с реальным периодом (таким как 5 мест, то есть 333,33 мс), вы можете следовать следующей опции в списке.

Держите шаги расчета Simulink в 1/3 секунду и 1 секунду в Simulink = 0.99999e9 такты в Симуляторе HDL. Если вы задаете часы в панели HDL Cosimulation блока Clocks, его период должен быть 1/3.

В целом Simulink обрабатывает шаг расчета для портов блока HDL Cosimulation следующим образом:

Если вход порт соединяется с сигналом, который имеет явный шаг расчета, основанное на прямом распространении, Simulink применяет эту скорость к этому входу порту.

Если вход порт соединяется с сигналом, который не имеет явного шага расчета, Simulink назначает для модели время расчета, которое равно наименьшему общему множеству (LCM) из всех идентифицированных входов шагов расчета порта.

После того, как Simulink устанавливает вход периодов дискретизации порта, он применяет пользовательские выходы шагов расчета ко всем портам выхода. Шаги расчета должно быть явным образом определено для всех выходных портов.

Если вы разрабатываете модель для косимуляции в относительном режиме синхронизации, примите во внимание следующее руководство по шагу расчета:

Задайте выход шага расчета для блока HDL Cosimulation как целое число, кратное пределу разрешения, заданному в Симулятор HDL. Используйте команду симулятор HDL report simulator state чтобы проверить предельное разрешение загруженной модели. Если предел разрешения Симулятора HDL равен 1 нс, и вы задаете выход блока шага расчета 20, Simulink взаимодействует с Симулятором HDL каждые 20 нс. |