Генератор TLM экспортирует целевой компонент TLM из Simulink® моделировать подсистему. Целевой компонент TLM имеет один сокет TLM, который поддерживает транзакции чтения и записи с помощью типового протокола TLM и типовой полезной нагрузки.

Следующая схема иллюстрирует самое простое поведение, которое можно задать для сгенерированного компонента TLM. Он не содержит карты памяти или команды и регистра состояния, и немедленно выполняет транзакции.

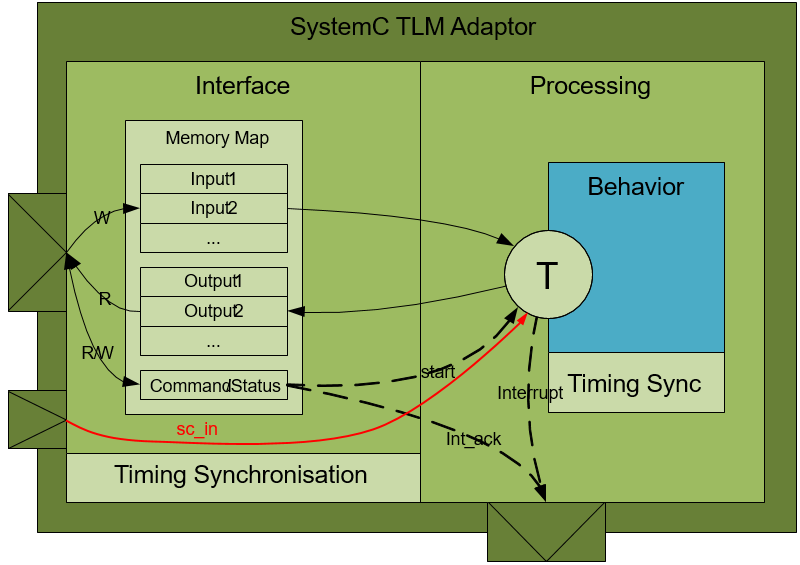

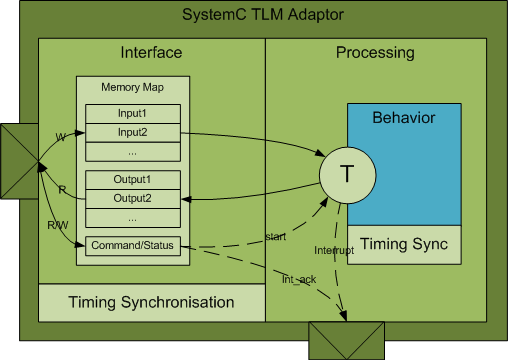

Для управления архитектурой сгенерированного компонента TLM можно выбрать среди нескольких опций. Включение карты памяти является одним из наиболее эффективнейшие опции. Следующий рисунок демонстрирует поведение сгенерированного компонента TLM с включенным полным дополнением функций.

Можно задать опции для следующих функций TLM:

Interface Timing - Моделирование времени, используемого транзакциями в реальной системе.

Выполнение алгоритма - Реализуйте компонент как поток SystemC или функцию обратного вызова.

No памяти map опции генерирует компонент TLM только с одним регистром чтения и одной записи без какого-либо адреса. Входы модели Simulink представлены регистром записи, а выходы представлены регистром чтения.

Без карты памяти сгенерированный компонент TLM имеет следующие характеристики:

Имеет один входной регистр и один выходной регистр.

Не нуждается - и игнорирует - адрес в запросах на чтение и запись во время симуляции SystemC, чтобы выбрать конкретные регистры на устройстве.

Получает все входные данные в одном запросе на запись, и запрос на чтение получает все выходы данные в возврат значении

Имеет входной и выходной регистры с размером либо для хранения всего набора данных, необходимого, либо созданные компонентом TLM, когда он выполняет поведение (функцию шага алгоритма) в вашей виртуальной платформе окружения

Когда входные регистры полны, это условие запускает (планирует) выполнение поведения в симуляторе SystemC. Выходные регистры обрабатываются одинаково.

Все значения по умолчанию для команд и состояния применяются.

Когда вы генерируете компонент TLM с этой опцией, можно использовать его в виртуальной платформе (VP) как:

Автономный компонент в испытательном стенде верификации

Прямая связанная совместная обработка модуля

Устройство, подключенное к каналу связи с помощью адаптера протокола

Автоматически сгенерированная карта памяти с опцией адреса генерирует компонент TLM с только одним регистром считанных данных и одним регистром записи данных с одним адресом каждый.

Входы модели Simulink представлены регистром записи, а выходы представлены регистром чтения. HDL Verifier™ автоматически присваивает адреса, необходимые для доступа к этим конкретным регистрам во время генерации кода. Эти адреса определяют конкретные смещения, необходимые для обращения к каждому отдельному регистру с помощью операций чтения и записи. Определение базового адреса для всего сгенерированного компонента TLM должно определяться виртуальной платформой, в которой находится компонент TLM. Определения адреса смещения появляются в файле определения, который генерируется вместе с компонентом TLM.

С одной карты памяти адреса сгенерированный компонент TLM имеет следующие характеристики:

Имеет один входной регистр и один выходной регистр, и опциональный регистр команд и состояний, а также тестовый и установленный регистр.

Должен иметь адрес в запросах на чтение и запись во время симуляции SystemC, чтобы выбрать конкретные регистры на устройстве.

Получает все входные данные в одном запросе на запись, и запрос на чтение получает все выходы данные в возврат значении

Имеет входной и выходной регистры с размером либо для хранения всего набора данных, необходимого, либо созданные компонентом TLM, когда он выполняет поведение (функцию шага алгоритма) в вашей виртуальной платформе окружения

Если команда и регистр состояния не используются или используется команда и регистр состояния и применяются значения по умолчанию, когда входной регистр полон, содержимое выталкивается в буфер, что затем запускает (планирует) выполнение поведения в симуляторе SystemC. Если используется команда и регистр состояния, а значение команды Push Входа Command устанавливается равным 1, модуль инициатора перемещает набор входных данных из регистра входа в вход буфер. Выходные регистры обрабатываются одинаково.

Если команда и регистр состояния не используются, применяются все значения по умолчанию для команд и состояния.

Когда вы генерируете компонент TLM с этой опцией, можно использовать его в виртуальной платформе (VP) как автономный компонент в испытательный стенд, или можно прикрепить его к каналу связи.

Автоматически сгенерированная карта памяти с опцией индивидуального адреса генерирует компонент TLM с одним регистром считанных данных на выход модели и записывает регистр данных на вход модели с отдельными адресами.

Каждый вход модели Simulink представлен соответствующим им регистром записи, и каждый выход представлен соответствующим им регистром чтения. Программа HDL Verifier автоматически присваивает адреса, необходимые для доступа к этим конкретным регистрам во время генерации кода. Эти адреса определяют конкретные смещения, необходимые для обращения к каждому отдельному регистру с помощью операций чтения и записи. Определение базового адреса для всего сгенерированного компонента TLM должно определяться виртуальной платформой, в которой находится компонент TLM. Определения адреса смещения появляются в файле определения, который генерируется вместе с компонентом TLM.

При индивидуальной карте памяти адреса сгенерированный компонент TLM имеет следующие характеристики:

Каждый входной регистр и каждый выходной регистр имеют свой собственный адрес, а также опциональную команду и регистр состояния и тестовый и установленный регистр.

Должен иметь адрес в запросах на чтение и запись во время симуляции SystemC, чтобы выбрать конкретные регистры на устройстве.

Доступ к каждому входу и выхода должен осуществляться индивидуально.

Модуль инициатора может записывать или читать каждый входной и выходной регистр в нескольких и/или частичных транзакциях.

Размер каждого входного и выходного регистра является размером данных.

Выполнение запускается, когда весь вход был записан или когда команда и набор бит регистра установлены в Автоматическое. Если установить значение вручную, модуль инициатора перемещает набор входных данных из регистра входа в вход буфер.

Выходные регистры обновляются, когда все выходные регистры были считаны или когда команда и набор бит регистров установлены в Автоматическое. Если установить значение вручную, модуль инициатора перемещает набор выхода данных из буфера выходов в выход регистр.

Когда вы генерируете компонент TLM с этой опцией, можно использовать его в виртуальной платформе (VP) как автономный компонент в испытательный стенд, или можно прикрепить его к каналу связи.

Можно принять решение сгенерировать компонент TLM с автоматически сгенерированной картой памяти с адресами. Когда вы делаете это, генератор TLM предлагает вам опцию включить регистр Command and Status (CSR) в сгенерированный компонент TLM. Определение для этого регистра появится в таблице.

Биты только для записи (WO) устанавливают взаимоисключающие команды. Можно утвердить только один командный бит в любой операции записи в CSR. Если в записи в CSR задано более одного командного бита, команда не определена. Вы активируете каждую команду, записав 1 в командный бит в регистре. Затем каждый командный бит автоматически очищается после выполнения команды. Вам не нужно записывать 0 в реестр, чтобы удалить команду бит. Биты только для записи всегда возвращаются равными 0 при любом чтении CSR. Запись команды не перезаписывает биты Read/Write или Write-Only.

Используйте биты Read and Write (R/W), чтобы получить текущее состояние и настройку. R/W бит sticky, что означает, что после того, как вы установили их путем записи 1 в бит в регистре, бит R/W остается установленным до тех пор, пока 0 не будет записано в тот же бит или не будет вызвана команда сброса. Биты Read-and-Write возвращают свои фактические значения любому чтению CSR.

Одна операция записи в CSR устанавливает все биты чтения и записи в регистре. Можно выбрать, чтобы задать только некоторые из бит и сохранить предыдущие значения других. Прежде чем вы сделаете это, необходимо сначала прочитать CSR, а затем изменить значения в соответствии с вашими требованиями. После завершения модификаций можно записать все 32 бита назад в CSR.

Биты только для чтения (RO) обеспечивают информацию о состоянии. Сгенерированный компонент автоматически устанавливает и очищает их значения, и модуль инициатора может считать их, чтобы узнать состояние. Биты только для чтения не изменяют свои фактические значения во время чтения или записи CSR.

В следующей таблице содержится полное определение регистра.

Следующая таблица объясняет, как заданы биты.

| Бит | Имя | Чтение/запись состояния | Описание |

|---|---|---|---|

| КСО < 0 > | Команда сброса | Только запись | Если установлено значение 1, то true:

Автоматически возвращается к 0 после выполнения команды. |

| КСО < 1 > | Запуск команды | Только запись | Вручную запускает выполнение поведения компонента TLM с помощью набора входных данных, который в данный момент находится в регистре входа, когда нет входа буферизации. Когда используется входная буферизация, эта команда не определена. |

| КСО < 2 > | Состояние прерывания | Только для чтения | Отражает текущее состояние сигнала прерывания. Предоставляет только статус. Устанавливает и очищает себя автоматически. |

| КСО < 3 > | Прерывание отключения | Прочтите и напишите | Если установлено значение 0, прерывания могут быть сгенерированы на сигнале прерывания и отражены в битах состояния прерывания CSR. Если установлено значение 1, отключает генерацию прерываний. |

| КСО < 8 > | Команда Push Input | Только запись | Когда используется буферизация, и режим Входа равен 0 (ручной режим), эта команда позволяет модулю инициатора переместить набор входных данных из регистра входа в вход буфер. Затем это запускает выполнение поведения компонента TLM. Когда буферизация не используется, эта команда не определена. Когда вход Mode равен 1 (автоматический), эта команда не определена. |

| КСО < 9 > | Вход | Прочтите и напишите | При установке значения 1 (автоматически) перемещение входных данных набора из регистра входа в вход буфер и выполнение поведения компонента TLM запускается автоматически, если полный набор данных был записан в вход регистр. Когда установлено значение 0 (вручную), перемещение входного набора данных из регистра входа в буфер входа и выполнение поведения должны быть инициированы вручную. Сделайте это, записав бит Start Command в 1, если буферизация не используется, или записав команду Push Input в 1, если буферизация присутствует. По умолчанию значение входа Mode устанавливается равным 1 (автоматический). Чтобы изменить его на 0 (вручную), задайте его в параметрах конструктора компонентов TLM. |

| КСО < 12 > | Команда Pull Output | Только запись | Когда используется буферизация, и значение Выхода Mode устанавливается на 0 (ручной режим), эта команда позволяет модулю инициатора переместить выход набор данных из головки выхода буфера в выход регистр. Когда буферизация не используется, эта команда не влияет. Когда значение выхода Mode равно 1 (автоматический), эта команда не определена. |

| КСО < 13 > | Выход | Прочтите и напишите | При установке значения 1 (автоматически) перемещение данных из головки выхода буфера в выход регистр запускается автоматически выполнением поведения компонента TLM. При установке значения 0 (вручную) перемещение данных из головки выхода буфера в выход регистр должно быть инициировано вручную. Сделайте это, записав команду Pull Output в 1, если буферизация присутствует. По умолчанию значение параметра Output Mode устанавливается равным 1 (автоматический). Чтобы изменить его на 0 (вручную), задайте его в параметрах конструктора компонентов TLM. |

Можно добавить сигнал прерывания, добавленный к сгенерированному компоненту TLM. Компонент TLM утверждает этот сигнал всякий раз, когда новые выходы доступны в любом выходном регистре. Сигнал автоматически очищается при каждом считывании значения из любого выходного регистра.

Сигнал прерывания является логическим сигналом SystemC, активным высоко. Активный бит прерывания в регистре состояния отражает состояние сигнала прерывания.

Можно использовать необязательный тест и задать регистр для управления доступом к общему компоненту TLM в среде SystemC. Любое чтение этого регистра возвращает текущее значение и устанавливает регистр на новое, заданное значение в атомарной операции. В системах с несколькими модулями инициатора выполнение этой задачи обычно требует доступа к одному и тому же целевому объекту. Если это так, то модуль инициатора имеет эксклюзивный доступ к сгенерированному компоненту TLM, пока следуют все другие модули инициатора. Модули инициатора должны считать тест и задать регистр и использовать целевое устройство только тогда, когда эта операция чтения возвращает значение 0. Модуль инициатора может проверить, что любое последующее чтение регистра теста и набора возвращает значение 1, которое указывает другим модулям инициатора, что устройство занято. После получения эксклюзивного доступа к компоненту TLM модуль инициатора освобождает компонент, когда целевые операции завершаются, записывая 0 в тестовый и установленный регистр.

Компонент TLM читает и записывает входы и выходы непосредственно из регистра интерфейса во время обработки алгоритма. После того, как инициатор запишет все входные регистры (если в режиме AUTO) или когда инициатор запишет команду START в CSR, алгоритм начинает обработку. Функция ожидания SystemC генерирует все таймеры.

Внимание

Чтобы предотвратить повреждение результатов обработки алгоритма, не позволяйте инициатору выполнять чтение или запись регистров во время обработки.

Эта схема показывает адаптер TLM с зарегистрированными интерфейсами.

Компонент читает и записывает входные и выходные входы через sc_signal порт (sc_in или sc_out). Эти входы/выходы не зарегистрированы. Когда функция step выполняется, она читает текущее значение sc_in портирует, выполняет и записывает результат в sc_out порты.

Эта схема показывает адаптер TLM с интерфейсами регистров и sc_in порт (красным).