Поведенческая модель интегральной схемы полумостового драйвера

Simscape/Электрический/Полупроводники и конвертеры

Блок Half-Bridge Driver обеспечивает абстрагированное представление интегральной схемы для управления полумостами MOSFET и IGBT. Блок моделирует входной гистерезис, задержку распространения и динамику включения/выключения. Если не моделировать схему драйвера затвора явно, всегда используйте этот блок или Gate Driver блок, чтобы задать напряжение источника затвора на блоке MOSFET или напряжении эмиттера затвора на блоке IGBT. Не соединяйте управляемый источник напряжения непосредственно с полупроводниковым затвором, потому что это опускает выходное сопротивление драйвера затвора, которое определяет динамику переключений.

Блок Half-Bridge Driver имеет два варианта моделирования, доступных путем щелчка правой кнопкой мыши по блоку в вашей блок-схеме и затем выбора соответствующей опции из контекстного меню, в разделе Simscape > Block choices:

PS input - Выходным состоянием драйвера управляет вход физического сигнала u. Используйте этот вариант, если Simulink определяет весь ваш контроллер, включая генерацию сигналов PWM® блоки. Этот вариант моделирования является вариантом по умолчанию.

Electrical input ports - Выходное состояние драйвера управляется двумя электрическими входными соединениями, PWM и REF. Используйте этот вариант, если ваша модель имеет аналоговые компоненты в восходящем направлении, такие как источник Controlled PWM Voltage.

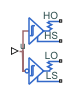

Первая пара выхода электрических портов, HO и HS, ведут себя так же, как порты G и S блока Gate Driver. Соедините эти порты с высокоскоростным MOSFET или IGBT полумоста. Вторая пара портов, LO и LS, соединяются с низкоскоростным MOSFET или IGBT полумоста. Они ведут себя подобным образом, за исключением того, что их логика инвертируется относительно высокой стороны.

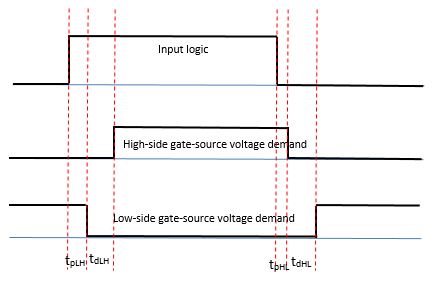

Схема показывает свойства синхронизации для полумостового драйвера, где:

t pLH является задержкой распространения на низкой стороне, когда входная логика переходит от 0 до 1.

t dLH является потерей времени на высокой стороне, когда входная логика переходит от 0 до 1.

t pHL является задержкой распространения на высокой стороне, когда входная логика переходит от 1 до 0.

t dHL - это низкоскоростное мертвое время, когда входная логика переходит от 1 до 0.

Можно вставить отказ в один или оба выходов в заданное время симуляции. Опции отказа:

Сбой входа фиксирован в логике 0

Неудачный вход, фиксированный в логике 1

Отказ высокой стороны off

Отказ высокой стороны на

Отказ нижней стороны off

Низкая сторона отказа на

Отказать высокие и низкие стороны off

Отказать высокие и низкие стороны на

Controlled PWM Voltage | Gate Driver | N-Channel IGBT | N-Channel MOSFET | P-Channel MOSFET