Simulink® Верификация модели библиотечных блоков оцените сигналы временной области в вашей модели, согласно спецификациям, которые вы присваиваете блокам. Блоки верификации модели возвращают утверждение, когда сигналы падают вне заданного предела или области значений. Во время симуляции, когда сигнал переходит предел, блок верификации может:

Остановите симуляцию и немедленно сфокусируйте внимание на этой части модели.

Сообщите об отказе с логическим сигналом. Если симуляция не завершается неуспешно, выходной сигнал true. Если симуляция прекращается, выход сигнала false.

Для ссылки информации об отдельных блоках верификации модели см. «Верификация модели».

Если вы используете блок Signal Builder для предоставления тестовых сигналов для вашей модели, можно включить и отключить блоки Верификации модели через графический интерфейс Верификации Manager. Чтобы открыть Verification Manager, на панели инструментов диалогового окна Signal Builder, выберите значок Show Verification Settings.![]()

Этот пример использует блок Check Static Lower Bound, чтобы остановить симуляцию модели, когда сигнал от блока Sine Wave переходит свой нижний предел границы.

В модели блок Check Static Lower Bound имеет параметр Lowner bound -0.8. Утверждение отключено, поэтому блок появляется вычеркнутым.

1. Дважды кликните блок Проверить статическую нижнюю границу и установите флажок Включить значения. Этот параметр включает утверждение блока верификации. В модели блок больше не вычеркивается.

2. Запустите симуляцию. Через 1.29517 секунд, когда сигнал от блока Sine Wave достигает нижней границы -0.8, блок верификации останавливает симуляцию с помощью этого диагностического сообщения:

An error occurred while running the simulation and the simulation was terminated Caused by: Assertion detected in 'ex_model_verif_block_check_static_lower_errwarn/Check Static Lower Bound' at time 1.29517

3. Чтобы проверить значение сигналов, дважды кликните блок Scope.

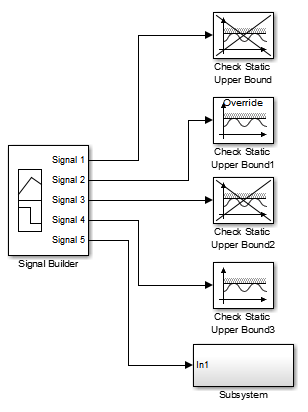

Эта модель содержит блок Signal Builder, который подает пять тестовых сигналов в блоки Верификации модели. Первые четыре сигнала соединяются непосредственно с блоками Check Static Upper Bound.

Пятый сигнал соединяется с подсистемой, которая содержит блок Check Static Upper Bound.

Включено только значение для блока Check Static Upper Bound3. Другие блоки Верификации модели появляются перечеркнутыми в модели, потому что их утверждения отключены.

Чтобы открыть Verification Manager, дважды кликните блок Signal Builder и выберите значок Показать параметры проверки.

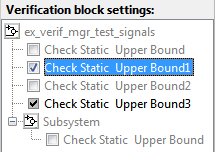

Диспетчер верификации состоит из панели Параметры блоков верификации и панели Requirements.

На панели Verification block settings перечислены все блоки Верификации модели в модели, сгруппированные по подсистемам. Для примера, в ex_verif_mgr_test_signals на модели Verification block settings отображаются пять блоков Check Static Upper Bound. Четыре находятся на верхнем уровне модели, а один - в подсистеме.

Можно выбрать дополнительные опции для просмотра блоков Верификации модели нажав правую кнопку мыши на панели Verification block settings:

Display > Tree format - Список блоков, которые появляются в иерархии модели.

Display > Overridden blocks only - Список только блоков, которые не включены для всех тестовых групп.

Display > Active blocks only - Список только блоков, которые включены для текущей группы сигналов.

На панели Requirements перечислены ссылки документов требований для текущей группы сигналов. Если у вас есть Simulink Requirements™, можно связать документы требований с тестами и соответствующими блоками Верификации модели через эту панель.

Чтобы открыть или закрыть панель Requirements, щелкните значок Requirements display.![]()

Чтобы связать документ требований с тестом, в панели Requirements щелкните правой кнопкой мыши и выберите Open Outgoing Links Dialog из контекстного меню. В диалоговом окне «Исходящие ссылки» можно просмотреть и выбрать документ требований. Для получения дополнительной информации смотрите Ссылка Тестов на Документы о требованиях (Simulink Requirements).

В Verification Manager каждый блок верификации имеет узел состояния, который указывает, включена или отключена его проверка. Узел состояния также указывает, применяется ли активный параметр повсеместно или только к текущей активной группе. В этой таблице описываются различные типы узлов состояния и опции контекстного меню, которые доступны при щелчке правой кнопкой мыши по узлу.

Узел | Статус | Опции контекстного меню |

|---|---|---|

| Блок верификации отключен для текущей активной группы. Щелкните, чтобы включить текущую активную группу. | Block enable for all groups - Включите блок верификации для всех тестовых групп. Тип узла изменяется на включенный для всех групп. |

| Block group enable - Включите блок верификации для текущей активной группы. Тип узла изменяется на включенный. | ||

| Блок верификации включен для текущей активной группы. Щелкните, чтобы отключить текущую активную группу. | Block enable for all groups - Включите блок верификации для всех тестовых групп. Тип узла изменяется на включенный для всех групп. |

| Block group disable - отключить блок верификации для текущей активной группы. Тип узла меняется на отключенный. | ||

| Блок верификации включен для всех тестовых групп. | Block enable by group - восстановите индивидуально включенные/отключенные настройки этого блока для всех тестовых групп. В зависимости от вашего предыдущего выбора тип узла изменяется на включенный |

Когда вы используете Verification Manager, чтобы включить блок верификации модели для текущей активной группы, в модели блок отображает метку Override. Для примера, в ex_verif_mgr_test_signals модель, когда вы выбираете Group 2 из списка Active Group Диспетчер Верификации показывает, что блок Check Static Upper Bound1 включен.

В модели блок Check Static Upper Bound1 не вычеркивается, но отображает метку Override.

Если ваша модель содержит много блоков верификации, утомительно включать и отключать блоки по отдельности. Используя Verification Manager, можно включить и отключить все блоки в подсистеме. На панели Verification block settings щелкните правой кнопкой мыши узел подсистемы![]() и выберите из следующих опций контекстного меню:

и выберите из следующих опций контекстного меню:

Contents enable for all groups - Включите все блоки верификации в этой подсистеме для всех тестовых групп.

Contents enable by group - восстановление индивидуально включенных/отключенных настроек каждого блока верификации в этой подсистеме для всех тестовых групп.

Contents group enable - индивидуально включите все блоки верификации в этой подсистеме для текущей активной группы.

Contents group disable - индивидуально отключите все блоки верификации в этой подсистеме для текущей активной группы.

Для примера, в ex_verif_mgr_test_signals модель, можно включить все блоки верификации для всех тестовых групп, дважды кликнув мышью на ex_verif_mgr_test_signals узел и выбор Contents enable for all groups. В Verification Manager все узлы изменяются на включенные для всех групп.![]()

Чтобы восстановить индивидуально включенные/отключенные настройки для каждого блока верификации в каждой группе, дважды кликните ex_verif_mgr_test_signals Узлом и выберите Contents enable by group.

Если у вас есть Simulink Control Design™, вы можете:

Отслеживайте характеристики временной области и частотного диапазона.

Задайте ограничения на характеристики линейной системы.

Проверяйте, что ограничения выполняются во время симуляции.

Для получения справочной информации об отдельных блоках см. «Верификация модели» (Simulink Control Design).

Check Static Lower Bound | Check Static Upper Bound | Scope | Signal Builder | Sine Wave