Ограничьте значения сигналов при доказывании свойств модели

Simulink Design Verifier

При работе в режиме проверки свойств Simulink® Design Verifier™ программного обеспечения доказывает, что свойства вашей модели удовлетворяют заданным критериям (см. «Что такое Property Proving?»). В этом режиме можно использовать блоки Proof Assumption, чтобы задать допущения для сигналов в вашей модели. Параметр Values позволяет вам задать ограничения на значения сигналов во время проверки свойства. Блок применяет указанный параметр Values к своему входному сигналу, а программное обеспечение Simulink Design Verifier доказывает или опровергает, что свойства вашей модели удовлетворяют заданным критериям.

Диалоговое окно параметра блока также позволяет:

Включите или отключите допущение.

Укажите, что блок должен отображать свой параметр Values в Редактор.

Укажите, что блок должен отображать свой выходной порт.

Примечание

Программное обеспечение Simulink и Simulink Coder™ игнорируют блок Proof Assumption во время симуляции модели и генерации кода, соответственно. Программа Simulink Design Verifier использует блок Proof Assumption только при доказывании свойств модели.

Используйте параметр Values, чтобы ограничить значения сигналов в доказательствах свойств. Задайте любую комбинацию скаляров и интервалов в форме MATLAB® массив ячеек. Для получения информации об массивах ячеек см. Раздел «Массивы ячеек».

Совет

Если параметр Values задает только одно скалярное значение, вам не нужно вводить его в виде массива ячеек MATLAB.

Каждый из скалярных значений содержит одну камеру в массиве, например:

{0, 5}Закрытый интервал содержит двухэлементный вектор как камера в массиве, где каждый элемент задает конечную точку интервала:

{[1, 2]}Также можно задать скалярные значения с помощью Sldv.Point конструктор, который принимает одно значение в качестве своего аргумента. Интервалы можно задать с помощью Sldv.Interval конструктор, который требует двух входных параметров, т.е. нижнюю границу и верхнюю границу для интервала. Вы также можете предоставить одно из следующих значений в качестве третьего входного параметра, который задает включение или исключение конечных точек интервала:

'()' - Задает открытый интервал.

'[]' - Определяет закрытый интервал.

'(]' - Определяет интервал открытия влево.

'[)' - Задает открытый вправо интервал.

Примечание

По умолчанию Sldv.Interval рассматривает интервал как закрытый, если вы опускаете его третий входной параметр.

Как пример, параметр Values

{0, [1, 3]}задает:

0 - скаляр

[1, 3] - закрытый интервал

Параметр Values

{Sldv.Interval(0, 1, '[)'), Sldv.Point(1)}задает:

Sldv.Interval(0, 1, '[)') - правый открытый интервал [0, 1)

Sldv.Point(1) - скаляр

Если для блока Proof Assumption задано несколько скаляров и интервалов, программа Simulink Design Verifier объединяет их с помощью логической операции OR во время проверки свойства. В этом случае программное обеспечение считает все предположение удовлетворенным, если удовлетворен какой-либо один скаляр или интервал.

Блок Proof Assumption принимает сигналы всех встроенных типов данных, поддерживаемых программным обеспечением Simulink. Для обсуждения типов данных, поддерживаемых программным обеспечением Simulink, смотрите Типы данных, поддерживаемые Simulink. Блок не поддерживает сложные входные сигналы.

Укажите, включен ли блок. Если выбран (по умолчанию), программа Simulink Design Verifier использует блок при проверке свойств модели. Удаление этой опции отключает блок, то есть заставляет программное обеспечение Simulink Design Verifier вести себя так, как если бы блок Proof Assumption не существовал. Если эта опция не выбрана, блок появляется серым цветом в редакторе Simulink.

Укажите, ведет ли блок себя как блок Proof Assumption или Test Condition. Выберите Test Condition чтобы преобразовать блок Proof Assumption в блок Test Condition.

Задайте доказательство допущения (см. «Определение доказательственных допущений»).

Укажите, отображает ли блок содержимое своего параметра Values в редакторе Simulink. По умолчанию эта опция выбрана.

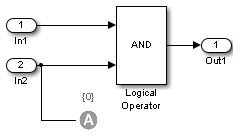

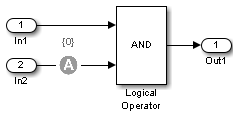

Укажите, отображается ли блок порт выхода в редакторе Simulink. Если выбран (по умолчанию), блок отображает свой выходной порт, позволяя его входному сигналу проходить в качестве выходного сигнала блока. Если не выбран, блок скрывает свой выходной порт и завершает входной сигнал. Следующая графика иллюстрирует внешний вид блока в каждом случае.

Pass through style (show Outport): Selected

Pass through style (show Outport): Deselected