Во время анализа поиска ошибок проектирования программное обеспечение проверяет заданные минимальное и максимальное значения на промежуточных сигналах в течение всей модели и на портах выхода. Эти значения определяют design ranges.

Анализ проверяет указанные минимальное и максимальное значения на:

Simulink® выходы блоков, за исключением ограничений, описанных в следующем разделе

Simulink.Signal объекты

Stateflow® объекты данных

MATLAB® для объектов данных генерации кода

Глобальные данные записывают

Если анализ обнаруживает, что сигнал превышает проект области значений, результаты идентифицируют, где в модели произошли ошибки. В сложение можно сгенерировать модель тестовой обвязки, содержащую тесты, которые демонстрируют, как произошла ошибка.

Если вы анализируете проверку модели, превышены ли указанные минимальные и максимальные значения, программное обеспечение не может проверить минимальные и максимальные значения, заданные на:

Любой Mux блок с выходом, соединенным с блоком Selector

Merge блочные входы

Чтобы обойти это ограничение, используйте Simulink.Signal объект на выходе блока Merge и задайте область значений на Simulink.Signal объект.

Примечание

Для получения информации о том, как анализ Simulink Design Verifier™ обрабатывает заданные минимальное и максимальное значения на входных портах, см. «Минимальные и максимальные входные ограничения».

В этом разделе вы создаете и анализируете модель, которая имеет заданные минимальное и максимальное значения проекта на:

Входные порты

Порты выхода двух промежуточных блоков

Анализ поиска ошибок проектирования идентифицирует блоки, где выходные значения превышают проектную область значений. Если анализ обнаруживает эту ошибку, этот пример демонстрирует, как анализ использует указанные минимальное и максимальное значения при продолжении анализа.

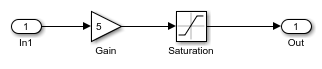

Создайте модель для этого примера:

В MATLAB панели инструментов на вкладке Home выберите New > Simulink Model.

Из библиотеки Simulink Обычно используемые блоки добавьте следующие блоки к модели и присвойте указанные значения параметров.

| Блок | Вкладка | Параметр | Значение |

|---|---|---|---|

| Inport | Signal Attributes | Minimum | 0 |

| Inport | Signal Attributes | Maximum | 5 |

| Выгода | Main | Gain | 5 |

| Выгода | Signal Attributes | Output minimum | 0 |

| Выгода | Signal Attributes | Output maximum | 20 |

| Выгода | Signal Attributes | Output data type | int16 |

| Насыщение | Main | Upper limit | 25 |

| Насыщение | Main | Lower limit | -25 |

| Насыщение | Signal Attributes | Output minimum | -25 |

| Насыщение | Signal Attributes | Output maximum | 25 |

| Вспомогательный порт | Никаких изменений | ||

Соедините четыре блока как показано на рисунке.

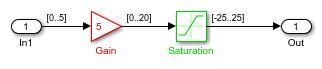

Чтобы отобразить указанные минимальное и максимальное значения, на вкладке Debug, выберите Information Overlays > Signal Data Ranges.

На вкладке Modeling нажмите Model Settings.

В диалоговом окне Параметров конфигурации, на панели Solver, под Solver selection:

Установите Type значение Fixed-step.

Программное обеспечение Simulink Design Verifier не поддерживает решатели переменных шагов.

Установите Solver значение discrete (no continuous states).

На панели Design Verifier установите для Mode значение Design error detection.

На панели Design Verifier > Design Error Detection:

Выберите Specified minimum and maximum value violations.

Очистите параметры Integer overflow и Division by zero.

В этом примере вы проверяете только на промежуточные минимальные и максимальные нарушения.

Чтобы сохранить эти настройки и выйти из диалогового окна Параметров конфигурации, нажмите OK.

Сохраните модель и назовите ее ex_interim_minmax.

Чтобы проанализировать модель примера, чтобы идентифицировать любые промежуточные сигналы, которые нарушают заданные минимальное и максимальное значения, выполните поиск ошибок проектирования анализ.

На вкладке Design Verifier нажмите Detect Design Errors.

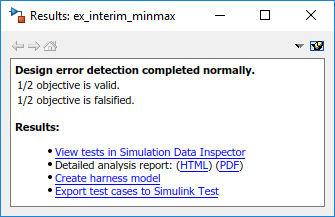

После завершения анализа:

Программа подсвечивает модель с результатами анализа.

Диалоговое окно Simulink Design Verifier Results открывает и показывает сводные данные анализа.

В окне модели Gain блок окрашен в красный цвет, а Saturation блок - в зеленый цвет. Это указывает, что:

По крайней мере, одна цель, связанная с блоком Gain, была сфальсифицирована. В данном примере анализ сфальсифицировал ровно одну цель.

Все цели, связанные с блоком Saturation, были удовлетворены. В данном примере анализ удовлетворял только одной цели.

Чтобы понять эти результаты:

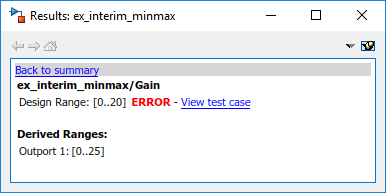

Щелкните на блоке Gain.

Окно Результатов Simulink Design Verifier показывает, что область значений проекта для выхода была [0.. 20], но анализ обнаружил ошибку и сгенерировал тест, которое демонстрирует эту ошибку. Поскольку область значений проекта для входного блока является [0.. 5], когда вход в Gain блок 5, выход 25, что превышает заданное максимальное значение на этом порте.

Анализ вычисляет и отображает производные области значений, чтобы помочь вам понять, как был превышен проект области значений.

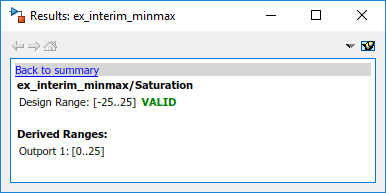

Щелкните на блоке Saturation.

Окно Simulink Design Verifier Results показывает, что вывод блока Saturation никогда не превышал диапазон проектирования [-25.. 25]. Вход в блок Saturation никогда не превышал [0.. 25], что является производной областью значений, которое анализ распространил из блока Gain.

Когда анализ завершается, можно создать модель тестовой обвязки, содержащую тесты, которые приводят к ошибкам.

Для модели с примером просмотрите тест, которая вызвала проект области значений ошибку в блоке Gain:

После завершения анализа и подсветки модели щелкните блок Gain.

В окне Simulink Design Verifier Results нажмите View test case.

Программа создает модель тестовой обвязки с именем ex_interim_minmax_harness и открывает блок Signal Builder в модель тестовой обвязки, который содержит тест.

В блоке Signal Builder один тест, значение сигналов которого 5, заставил выход блока Gain равняться 25, что превышает заданное максимальное значение 20.

Прежде чем моделировать этот тест, в диалоговом окне Параметров конфигурации, на панели Diagnostics > Data Validity, установите Simulation range checking warning или error.

Установка этого параметра задает диагностическое действие, которое должно быть принято, если Simulink обнаруживает сигналы, которые превышают заданные минимальные или максимальные значения во время симуляции.

Если вы задаете warning, симуляция отобразит предупреждающее сообщение и продолжит.

Если вы задаете errorсимуляция отображает сообщение об ошибке и останавливается.

Нажмите кнопку OK, чтобы сохранить изменения и закрыть диалоговое окно Параметры конфигурации.

В Signal Builder окне блока нажмите Start simulation, чтобы симулировать модель с этим тестом.

Как ожидалось, в окне MATLAB в симуляции отображается предупреждение или ошибка о том, что выходное значение блока Gain превышает заданный максимум.

Можно также сгенерировать HTML, содержащий подробную информацию об отчете анализа для ex_interim_minmax модель. Чтобы создать этот отчет, в окне Simulink Design Verifier Results, нажмите Generate detailed analysis report. Отчет об анализе откроется в браузере.

В отчете об анализе в Design Error Detection Objectives Status главе доклада приводятся подробные результаты по двум категориям:

Objectives Proven Valid - Значения выхода для блока Saturation всегда находятся в пределах проекта области значений.

Objectives Falsified with Test Cases - Значения выхода для блока Gain нарушили проект области значений.